# Fuzzy Simulated Evolution Algorithm for VLSI Cell Placement

by

### Ali Syed Hussain

A Thesis Presented to the

FACULTY OF THE COLLEGE OF GRADUATE STUDIES

KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

**MASTER OF SCIENCE**

In

**COMPUTER ENGINEERING**

December, 1998

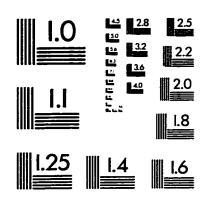

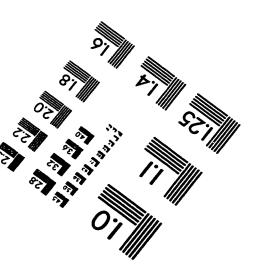

**INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI

films the text directly from the original or copy submitted. Thus, some

thesis and dissertation copies are in typewriter face, while others may be

from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the

copy submitted. Broken or indistinct print, colored or poor quality

illustrations and photographs, print bleedthrough, substandard margins,

and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete

manuscript and there are missing pages, these will be noted. Also, if

unauthorized copyright material had to be removed, a note will indicate

the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by

sectioning the original, beginning at the upper left-hand corner and

continuing from left to right in equal sections with small overlaps. Each

original is also photographed in one exposure and is included in reduced

form at the back of the book.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white

photographic prints are available for any photographs or illustrations

appearing in this copy for an additional charge. Contact UMI directly to

order.

IMI

A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor MI 48106-1346 USA 313/761-4700 800/521-0600

|  | · |  |

|--|---|--|

## **NOTE TO USERS**

The original document received by UMI contains pages with indistinct print. Pages were microfilmed as received.

This reproduction is the best copy available

**UMI**

FUZZY SIMULATED EVOLUTION

ALGORITHM FOR

VLSI CELL PLACEMENT

BY

ALI SYED HUSSAIN

A Thesis Presented to the

FACULTY OF THE COLLEGE OF GRADUATE STUDIES

KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the

Requirements for the Degree of

MASTER OF SCIENCE

In

COMPUTER ENGINEERING

DECEMBER 1998

UMI Number: 1393213

UMI Microform 1393213 Copyright 1999, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

UMI 300 North Zeeb Road Ann Arbor, MI 48103

# KING FAHD UNIVERSITY OF PETROLEUM AND MINERALS DHAHRAN 31261, SAUDI ARABIA

### COLLEGE OF GRADUATE STUDIES

This thesis, written by

## ALI, SYED HUSSAIN

under the direction of his Thesis Advisor and approved by his Thesis Committee, has been presented to and accepted by the Dean of the College of Graduate Studies, in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE IN COMPUTER ENGINEERING

Thesis Committee

Dr. Sadiq. M. Sait (Chairman

Dr. Mabib Joussef (Co - chairman

Dr. Hasan Barada (Member)

Dean, College of Graduate Studies

14/2/99 Date Dedicated

to

my beloved parents

## Acknowledgments

All praise be to Allah, Subhanahu-wa-ta-Aaala, for his limitless help and guidance. May Allah bestow peace on his prophet, Muhammad (pbuh), and his family. I acknowledge the support and facilities provided by King Fahd University of Petroleum and Minerals, Dhahran, Saudi Arabia.

My family, especially my most loving Mummy and Daddy were constant source of motivation. Their love and support carried me through some difficult moments in my life. Their prayers, guidance and inspiration led to this accomplishment.

I would like to express my profound gratitude and appreciation to my thesis committee chairman Dr. Sadiq M. Sait and co-chairman Dr. Habib Youssef, for their guidance and patience throughout this thesis. It was because of them that the work at any point of time, never got stressful. Their continuous support, advice and encouragement can never be forgotten. Thanks are also due to my thesis committee member Dr. Hassan Barada for his interest, cooperation and constructive criticism.

I also wish to thank the Chairman of Computer Engineering Department, Dr. Abdullah Almojel and Dean of College of Computer Science and Engineering, Dr.

Khalid AlTawil for all the support they provided in order to achieve this work. Also, my thanks go to the faculty and staff members of Computer Engineering Department for their encouragement. I would like to thank all the research assistant community in KFUPM especially Salman, Naved, Tariq, Faisal and Mansoor for their moral support. Thanks are also due to Ahmad for helping me in arabic translation of thesis abstract.

## **Contents**

|   | Ack  | nowledgments                               | 11 |

|---|------|--------------------------------------------|----|

|   | List | of Tables                                  | ix |

|   | List | of Figures                                 | x  |

|   | Abs  | stract (English)                           | ii |

|   | Abs  | stract (Arabic)                            | iv |

| 1 | Intr | roduction                                  | 1  |

| 2 | Pre  | liminaries                                 | 6  |

|   | 2.1  | Introduction                               | 6  |

|   | 2.2  | Problem Definition                         | 7  |

|   | 2.3  | Standard Cell Layout                       | 7  |

|   | 2.4  | Cost Function                              | 8  |

|   |      | 2.4.1 Wirelength Estimation of VLSI Layout | 9  |

|   |                                 | 2.4.2                                                          | Layout Area                                                                                                 | 10                                     |

|---|---------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------|

|   |                                 | 2.4.3                                                          | Circuit Delay                                                                                               | 11                                     |

|   | 2.5                             | Net De                                                         | elay Bounds                                                                                                 | 13                                     |

|   | 2.6                             | Techno                                                         | ology Details                                                                                               | 16                                     |

|   | 2.7                             | Simula                                                         | ted Evolution (SE) Algorithm                                                                                | 17                                     |

|   |                                 | 2.7.1                                                          | Description of SE Algorithm                                                                                 | 17                                     |

|   | 2.8                             | Fuzzy 1                                                        | Logic                                                                                                       | 22                                     |

|   |                                 | 2.8.1                                                          | Fuzzy Set Theory (FST)                                                                                      | 22                                     |

|   |                                 | 2.8.2                                                          | Fuzzy reasoning                                                                                             | 25                                     |

|   | 2.9                             | Conclu                                                         | sion                                                                                                        | 27                                     |

|   |                                 |                                                                |                                                                                                             |                                        |

| 3 | Lite                            | rature                                                         | Review                                                                                                      | 28                                     |

| 3 | Lite                            |                                                                | Review                                                                                                      |                                        |

| 3 |                                 | Introdu                                                        |                                                                                                             | 28                                     |

| 3 | 3.1                             | Introdu                                                        | iction                                                                                                      | 28<br>29                               |

| 3 | 3.1                             | Introdu<br>Genera<br>3.2.1                                     | l Placement Techniques                                                                                      | 28<br>29<br>29                         |

| 3 | 3.1                             | Introdu<br>Genera<br>3.2.1<br>3.2.2                            | ction                                                                                                       | 28<br>29<br>29<br>30                   |

| 3 | 3.1                             | Introdu<br>Genera<br>3.2.1<br>3.2.2<br>Fuzzy                   | Constructive Placement Schemes                                                                              | 28<br>29<br>29<br>30<br>36             |

| 3 | 3.1<br>3.2<br>3.3               | Introdu<br>Genera<br>3.2.1<br>3.2.2<br>Fuzzy Applica           | Constructive Placement Schemes                                                                              | 28<br>29<br>29<br>30<br>36<br>38       |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5 | Introdu<br>Genera<br>3.2.1<br>3.2.2<br>Fuzzy Applica<br>Conclu | Constructive Placement  Iterative Placement Schemes  Logic Based Placement Schemes  ations of SE algorithms | 28<br>29<br>29<br>30<br>36<br>38<br>41 |

|   | 4.1  | Introduction                                                            | <del>1</del> 2 |

|---|------|-------------------------------------------------------------------------|----------------|

|   | 4.2  | Proposed Scheme and Implementation Details                              | 14             |

|   |      | 4.2.1 Initial Solution                                                  | 14             |

|   |      | 4.2.2 Fuzzy Goal-based Cost Measure                                     | <del>1</del> 5 |

|   |      | 4.2.3 Proposed Evaluation Scheme                                        | 19             |

|   |      | 4.2.4 Selection                                                         | 51             |

|   |      | 4.2.5 Allocation                                                        | 51             |

|   |      | 4.2.6 Stopping Criterion                                                | 57             |

|   | 4.3  | Experiments and Results                                                 | 58             |

|   |      | 4.3.1 Effect of the Size of the Fuzzy Window on FSE_FA 6                | 61             |

|   |      | 4.3.2 Comparison of SE, FSE_WA and FSE_FA                               | 62             |

|   |      | 4.3.3 Comparing FSE_WA and FSE_FE                                       | 67             |

|   | 4.4  | Conclusion                                                              | 75             |

| 5 | Effe | ect of Selection Bias on Algorithm Efficiency 7                         | 77             |

|   | 5.1  | Effects of Bias on Quality of Solution                                  | 80             |

|   | 5.2  | Normalized Goodness Values                                              | 84             |

|   | 5.3  | Variable Bias: Function of Average Cell Goodness $(B = \mathcal{F}(G))$ | 88             |

|   | 5.4  | Comparison of Bias Schemes                                              | 89             |

|   | 5.5  | Fuzzy Allocation and Variable Bias SE algorithm (FSE_VB)                |                |

|   | 5.6  | Conclusion                                                              |                |

| 6 | Cor | sion            |     |  |

|---|-----|-----------------|-----|--|

|   | 6.1 | Future Research | .03 |  |

|   | BIF | LIOGRAPHY 10    | 05  |  |

## List of Tables

| 2.1 | Technology parameters used in this research                             | 16 |

|-----|-------------------------------------------------------------------------|----|

| 4.1 | Classification of our SE implementations                                | 59 |

| 4.2 | Parameter values for different stages of the SE algorithm               | 60 |

| 4.3 | The characteristics of circuits and layouts used in our experiments.    |    |

|     | (LH = layout heights in micron, Avg. RCH = average routing channel      |    |

|     | height in micron, $O_1$ = optimum wire length in micron, $O_2$ = Sum of |    |

|     | the switching delay of the longest path in $nsec$ , $O_3$ = optimum row |    |

|     | length of the layout in micron.)                                        | 60 |

| 4.4 | Results of FSE_WA for different weights for circuit c499                | 60 |

| 4.5 | Results of FSE_FA for different sizes of fuzzy window (w). Where        |    |

|     | wire length $(L)$ and layout width $(W)$ are in micron. The circuit     |    |

|     | delay $(D)$ and execution time of the algorithm $(T)$ are in $ns$ and   |    |

|     | minutes respectively.                                                   | 63 |

| 4.6 | Best layout found by SE, FSE_WA and FSE_FA                              | 65 |

| 4.7 | Best layout found by FSE_FE and FSE_WA                                          | 75 |

|-----|---------------------------------------------------------------------------------|----|

| 5.1 | Effect of bias on quality of solution generated and execution time              |    |

|     | of the SE algorithm. The wire length cost of the solution (L) is in             |    |

|     | micron and the execution time (T) is in minutes                                 | 83 |

| 5.2 | Comparison of solution quality and execution times of best fixed bias           |    |

|     | and normalized goodness SE algorithm. The wire length cost of the               |    |

|     | solution (L) is in micron and the execution time (T) is in minutes. B           |    |

|     | is best fixed bias value                                                        | 86 |

| 5.3 | Comparison of solution quality and execution times of best fixed bias           |    |

|     | and variable bias $(B = \mathcal{F}(G))$ SE algorithms. The wire length cost of |    |

|     | the solution (L) is in micron and the execution time (T) is in minutes.         |    |

|     | B is best fixed bias value                                                      | 90 |

| 5.4 | Best layout found by FSE_VB and FSE_WA. The wire length cost                    |    |

|     | (L) and layout width (W) are in micron. The circuit delay cost (D)              |    |

|     | is in ns and execution time of the algorithm (T) is in minutes                  | 96 |

## List of Figures

| 2.1 | Layout of a standard cell placement                                        | 8  |

|-----|----------------------------------------------------------------------------|----|

| 2.2 | Steiner tree approximation for estimation of interconnect length. The      |    |

|     | length of the tree is distance of the bisecting line $(W)$ and depth is    |    |

|     | $\sum_{i=1}^n h_i$                                                         | 10 |

| 2.3 | Structure of the simulated evolution algorithm.                            | 19 |

| 2.4 | Sorted individual best fit placement.                                      | 22 |

| 2.5 | Membership function for a fuzzy set A                                      | 23 |

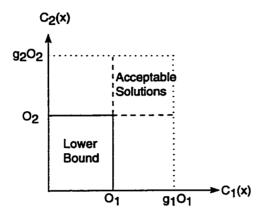

| 4.1 | Range of acceptable solution set.                                          | 46 |

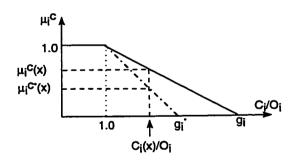

| 4.2 | Membership function within acceptable range. By lowering the goal          |    |

|     | $g_i$ to $g_i^*$ the preference for objective "i" has been increased       | 47 |

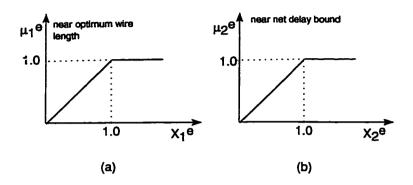

| 4.3 | Membership functions used in fuzzy evaluation stage. (a) function for      |    |

|     | near optimum wire length $(\mu_1^e)$ (b) function for near net delay bound |    |

|     | $(\mu_2^e)$                                                                | 51 |

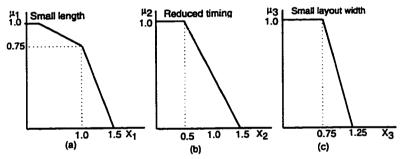

| 4.4  | Membership functions for three fuzzy variables used in Fuzzy Alloca-    |    |

|------|-------------------------------------------------------------------------|----|

|      | tion Scheme of the SE algorithm.                                        | 56 |

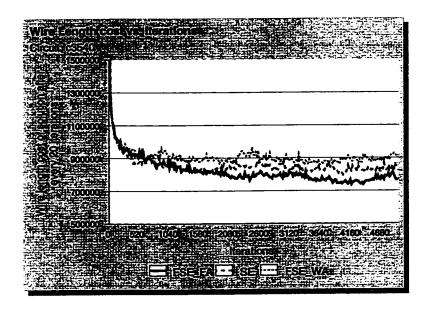

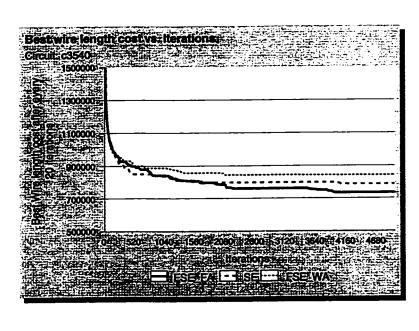

| 4.5  | Wire length costs of solutions against iteration count: (a) length of   |    |

|      | the current solution (after every 20 iterations) (b) length of the best |    |

|      | solution                                                                | 68 |

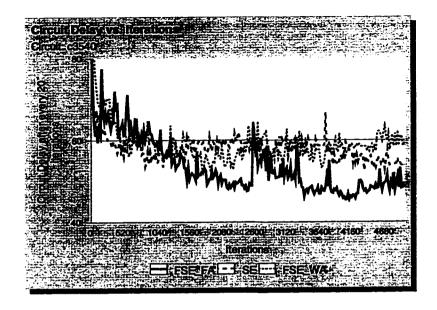

| 4.6  | Circuit delay of solutions: (a) delay of the current solution (after    |    |

|      | every 20 iterations) (b) delay of the best solution                     | 69 |

| 4.7  | Layout width against iteration count: (a) width of the current solu-    |    |

|      | tion (after every 20 iterations) (b) width of the best solution         | 70 |

| 4.8  | Overall cost of the solutions represented as membership values of       |    |

|      | solutions in fuzzy set acceptable solution: (a) current membership      |    |

|      | values (after every 20 iterations) (b) best membership values           | 71 |

| 4.9  | Average cell goodness against iteration count: (a) cell goodness of the |    |

|      | current solution (after every 20 iterations) (b) goodness of the best   |    |

|      | solution                                                                | 72 |

| 4.10 | Cardinality of selection sets of FSE_FA, SE and FSE_WA                  | 73 |

| 5.1  | The effect of bias on the Simulated Evolution algorithm. (a) quality    |    |

|      | of solution generated by SE (b) execution time of the algorithm         | 81 |

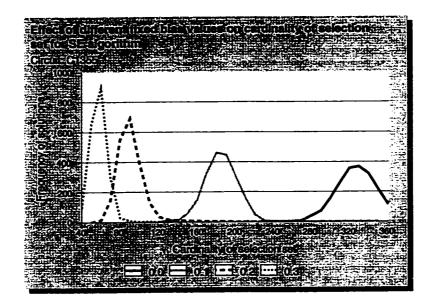

| 5.2  | Cardinality of selection set against against frequency of solutions for |    |

|      | different fixed bias SE algorithm.                                      | 82 |

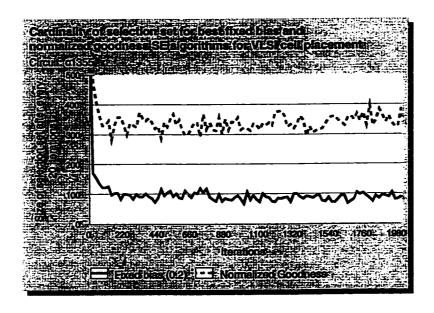

| 5.3 | Comparison of best fixed bias and normalized goodness SE algorithm.       |    |

|-----|---------------------------------------------------------------------------|----|

|     | (a) size of the selection set (b) solution quality.                       | 87 |

| 5.4 | Comparison of different bias schemes (a) current wire length cost (b)     |    |

|     | best wire length cost                                                     | 91 |

| 5.5 | Cardinality of selection set against frequency of solutions for different |    |

|     | bias schemes for the SE algorithm.                                        | 93 |

| 5.6 | Comparison of different bias SE algorithms (a) average cell goodness      |    |

|     | (b) best average cell goodness                                            | 94 |

#### THESIS ABSTRACT

Name: ALI, SYED HUSSAIN

Title: FUZZY SIMULATED EVOLUTION ALGORITHM

FOR VLSI CELL PLACEMENT

Major Field: COMPUTER ENGINEERING

Date of Degree: DECEMBER 1998

Simulated Evolution (SE) in an iterative heuristic to generate near optimal solutions to NP-Hard problems. VLSI cell placement is an NP-Hard problem with many conflicting objectives namely, wire length, circuit delay and area. The best solution for such a problem is the one which scores lowest with respect to all objectives. However, such a solution most likely does not exist. In order to identify the best solution generated by the Simulated Evolution algorithm, we propose a novel approach of fuzzy goal-based cost measure. This approach overcomes the problems related to the controversial weighted sum approach. It also allows easy incorporation of user preferences for different objectives. We have also proposed fuzzification of allocation and evaluation stages of the SE algorithm. The allocation scheme tries to minimize multiple objectives and adds controlled randomness as opposed to original deterministic allocation schemes. Experiments with benchmark tests demonstrate a noticeable improvement in solution quality. The fuzzy evaluation scheme combines wire length and net delay bounds for computation of individual cell goodnesses. It results in improvements in circuit delay but slight increase in the wire length. We have also proposed a variable bias scheme in place of fixed bias in the SE algorithm. The fixed bias scheme requires several trial runs to determine best value. In contrast, the variable bias is a function of average cell goodness, automatically adjusts its value and saves the SE algorithm from trial runs. The results of the variable bias scheme are comparable to the best fixed bias scheme.

#### MASTER OF SCIENCE DEGREE

KING FAHD UNIVERSITY OF PETROLEUM AND MINERALS Dhahran, Saudi Arabia

December 1998

## خلاصة الرسالة

اسم الطالب الكامل: سيد حسين على

عنـــوان الدراســـــــة: خوارزم النشوء المحاكي الغائم لوضع الخلايا في الدوائر المتكاملة عالية الكثافة جدا

تاريسيخ الشهسادة: ديسمبر 1998

النشوء المحاكى (Simulated Evolution) عبارة عن مستكشف تسلسلي يستخدم لإيجاد حلول قريبة من الحل الأمشال للمشاكل التي لا يمكن حلها بكثيرات الحدود (NP-Hard Problems). وضع الحلايا في الدوائر المتكاملة عائية الكثاف... جدا مشكلة لا يمكن تمثيلها بكثيرة حدود ولها أهداف متعارضة ألا وهي طول التوصيلات، زمن التنفيذ وانساحة الكلية. أفضل الحلول لمشكلة كهذه هو الذي يحقق أقل القيم في جميع الأهداف إلا أن حلا كهذا لا يوجد غالبا. لتعريف الحسال الأمثل الذي يقدمه حوارزم النشوء المحاكى، نقدم طريقة جديدة لحساب تكلفة الحل بطريقة غامضة معتمدة على الهذف. المتعلقة بطريقة المجموع الموزون. إضافة إلى ذلك فإن هذه الطريقة تسممع باعتبار أفضليات المستخدم لمختلف الأهداف. كما نقدم طريقة لتغميض مرحلة التوزيع ومرحلة التقييم في الحوارزم المذكور. طريقة التوزيع عاول تقليل قيم الأهداف المتعارضة وإضافة عشوائية محكومة خلافا للطريقة الأصلية ذات التوزيع المحدد. التحدرب على دوائر الاختبار تثبت تطورا ملحوظا في نوعية الحل. طريقة التقييم الغامض تجمع طول التوصيلات وزمنها لحساب جودة الخلايا متفرقة. ينتج عن ذلك تحسن في زمن التنفيذ وزيادة بسيطة في طول التوصيلات. إضافة إلى ذلك، لحساب جودة الخلايا متفرقة. ينتج عن ذلك تحسن في زمن التنفيذ وزيادة بسيطة في طول التوصيلات. إضافة إلى ذلك، القيمة الأنسب. في المقابل، التحفيز المتغير دالة تعتمد على متوسط جودة الخلية، تضبط قيمتها تلقائيا لتوفر التحسارب. نتائج التحفيز المتغير قرية من أفضل نتائج التحفيز الثابت.

درجة الماجستير في العلوم حامعة الملك فهد للبترول والمعادن الظهران، المملكة العربية السعودية التاريخ: ديسمبر 1998

## Chapter 1

## Introduction

In Very Large Scale Integration (VLSI) circuit design, *Placement* is the process of arranging circuit blocks on a layout. In *standard cell* design, where circuit blocks are of fixed height and variable widths, placement consists of determining optimum positions of all blocks on the layout to satisfy a number of objectives [1, 2]. The simplest version of the placement problem is the optimization of wire length for one dimensional placement. Even this simplified version is NP-Hard [3, 4]. More complex versions of this problem are characterized by multiple objectives and constraints such as interconnect timing delay, area, wire length etc. It is not possible to enumerate all combinations and come up with the best solution. Therefore we have to use some intelligent methods known as "heuristics", to get near optimal solutions in reasonable amount of time. These heuristics fall into two categories: *constructive* and *iterative*.

Constructive heuristics produce a complete solution by making deterministic moves. Some examples of constructive schemes are force directed placement, numerical optimization, min-cut placement etc. These schemes are reviewed in [1, 2]. Constructive techniques are fast but fall short of generating good layouts. It is due to the fact that they always have local view of the search space [5].

Iterative heuristics attempt to improve a complete solution by making controlled stochastic moves [5]. Generally, we can classify iterative schemes into two subclasses. Schemes which always accept good solutions like local search, force directed interchange etc., and schemes which can accept bad solutions probabilistically like simulated annealing [6], genetic algorithms [7], simulated evolution [8] and stochastic evolution [37]. Probabilistic iterative schemes generally outperform constructive and greedy schemes because their hill climbing property (i.e., accepting bad solutions) saves them from getting trapped in local optima [5].

Iterative heuristics have been used for the VLSI cell placement. The use of genetic algorithm (GA) for placement is proposed in [9, 10, 11, 12, 13]. Similarly use of simulated annealing (SA) [6] for VLSI cell placement is discussed and reported in [1, 2, 14, 15, 16]. There are some concerns about the execution time of these schemes [17] and premature convergence of GA [18]. In order to overcome these problems, Kling and Banerjee proposed the *Simulated Evolution* (SE) heuristic [19], which combines iterative improvement and constructive perturbation. It saves itself from getting trapped in local optima by using stochastic selection of design compo-

nents for perturbation. The advantage of this heuristic is reduced execution time than simulated annealing and genetic algorithm [8].

For multiobjective optimization, fuzzy logic provides an easy way of expressing expert human knowledge in decision making process of any iterative heuristic. The advantage of fuzzy logic over classical crisp logic is that it establishes an approximate truth value of propositions in accordance with the rules designed by the expert, while in crisp logic the proposition will be either true or false. Furthermore, it provides a rigorous algebra for dealing with imprecise information.

### Objectives of Research

In this thesis we present a Fuzzy Simulated Evolution Algorithm for multiobjective optimization of VLSI Standard Cell Placement. In our scheme we minimize three cost parameters of the placement layout: interconnection wire length, delay and layout width. We propose a novel way of identifying the best solution generated by the SE algorithm. This scheme uses a fuzzy goal-based cost measure which combines multiple cost parameters into a scalar cost measure. Apart from proposing this fuzzy cost measure, we have also investigated the fuzzification of other stages of the algorithm. The SE algorithm consists of three distinct steps: evaluation, selection and allocation. We propose fuzzification of allocation and evaluation stages of the simulated evolution algorithm. We propose a "fuzzy controlled stochastic allocation" instead of the previously purely constructive sorted individual best

fit allocation strategy. The experiments show that the proposed fuzzy allocation scheme based SE algorithm (FSE\_FA) results in an overall improved solution quality compared to a weighted average allocation based algorithm (FSE\_WA) as well as wire length based single objective SE algorithm (SE) as originally proposed by Kling and Banerjee [8]. Our proposed fuzzy evaluation scheme combines wire length and net delay bounds for evaluating placement of a circuit block in a location. The experiments indicate that for bigger circuits the proposed evaluation scheme based SE algorithm (FSE\_FE) results in a reduction in circuit delay compared to the wire length only evaluation scheme.

Selection bias is a parameter of the SE algorithm. We have investigated the effects of this parameter on the simulated evolution algorithm. We propose three dynamic bias variants. The results of our modifications are compared with fixed bias [8] and normalized goodness measure [20].

### Organization of Thesis

The rest of this thesis is organized as follows. Chapter 2 gives preliminary information helpful in understanding the rest of the thesis. This chapter formally defines the VLSI cell placement problem, describes the standard cell layout style and placement problem, computation of cost function and contains a review of fuzzy logic. It also reviews the classical simulated evolution algorithm.

In Chapter 3 we review related literature. This chapter covers VLSI cell place-

ment schemes, fuzzy logic based placement schemes and different studies which use SE in computer aided design problems.

In Chapter 4 we propose fuzzy goal-based cost measure. Furthermore, fuzzy allocation and evaluation schemes for the simulated evolution algorithm for VLSI cell placement are also proposed. Details of our implementations of these schemes are given. We compare and contrast these schemes with multiobjective weighted average SE algorithm and single objective SE implementation similar to the one proposed by Kling and Banerjee [8].

In Chapter 5 we investigate the effect of selection bias on simulated evolution algorithm. In this chapter we have proposed variable bias concept. Our proposals allow a bias which is a function of the problem instance. We also compare results of proposed scheme with the existing schemes like fixed bias [8] and normalized goodness [20]. The thesis ends with conclusion and future work in Chapter 6.

## Chapter 2

## **Preliminaries**

### 2.1 Introduction

Necessary problem specific information is included in this chapter. This information is needed to understand concepts, terminology and related work described in the subsequent chapters. We formally define the VLSI cell placement problem in Section 2.2. We will also describe the Standard Cell Placement (Section 2.3) and cost computation functions for such a placement (Section 2.4). We have used net delay bounds in our implementation of the simulated evolution algorithm. The transformation of the path constraints into net delay bounds is given in Section 2.5. Details of the environment used in our experiments are given in Section 2.6.

This research is based on the use of the simulated evolution algorithm. Thus, a quick review of this heuristic is given in Section 2.7. A primer on fuzzy logic is

given in Section 2.8. The chapter ends with a conclusion in Section 2.9.

## 2.2 Problem Definition

Given a set of modules  $M = \{m_1, m_2, ..., m_n\}$  and a set of signals  $S = \{S_1, S_2, ..., S_k\}$ , we associate with each module  $m_i \in M$  a set of signals  $S_m$ , where  $S_m \subseteq S$ . Similarly with each signal  $S_i \in S$  we associate a set of modules  $M_{si}$ , where  $M_{si} = \{m_j | s_i \in S_{m_j}\}$ .  $M_{si}$  is said to be a signal net. We are also given a set of slots or locations  $L = \{L_1, L_2, ..., L_p\}$ , where  $p \geq n$ . The placement problem is to assign each  $m_i \in M$  to a unique location  $L_j$  such that some objectives are to be optimized [1]. Generally, minimization of interconnect wire length has been widely used as the objective of VLSI placement. However, advancement in technology has resulted in reduction in gate switching delay making the interconnect delay a prominent factor in overall circuit delay [21]. Reduction of interconnect delay and layout area along with wire length are important objectives in the placement stage of the VLSI physical design automation process.

## 2.3 Standard Cell Layout

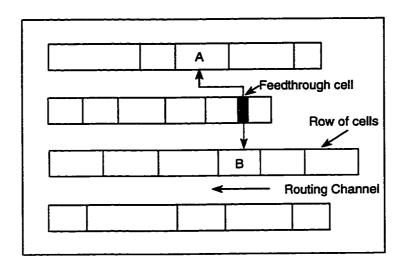

In standard cell design all the cells are constrained to have the same height, while width of the cell is variable and depends upon its complexity [1]. Cells are placed in horizontal rows and the cell rows are separated by horizontal routing channels.

In order to connect cells within a row or cells from two different rows, channels are used for running interconnect wires. Connecting cells from two non-adjacent rows, requires feed through cells in intermediate rows. The feed through cells allow running vertical wires from cell rows. Figure 2.1 shows block diagram of a standard cell layout.

Figure 2.1: Layout of a standard cell placement.

## 2.4 Cost Function

In this section we will review the estimation models for finding the cost of a VLSI placement layout. As mentioned earlier, in this work we attempt to minimize three quantities: wire length, interconnect delay, and area, The following text describes the estimation schemes used in our implementations for these three parameters.

### 2.4.1 Wirelength Estimation of VLSI Layout

Usually, layout placement generators optimize the total interconnect wire length. Reduction in wire length results in cost reduction, reduced chip area in standard cell design and improvement in circuit delay. The cost of a solution due to wire length is determined by adding the wire length estimates for all the nets in the circuit.

Different estimation schemes for net length have been used in the placement algorithms. For example (a) semi-perimeter method, (b) complete graph, (c) minimum chain, (d) source to sink connection, (e) minimum spanning tree, and (f) minimum Steiner tree are used to estimate net length [2]. A Steiner tree is the shortest route for connecting a set of pins [1]. However, determination of minimum steiner tree is known to be NP-Complete [1]. Therefore, in this work we approximate the steiner tree using following technique.

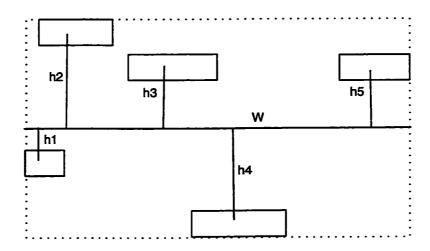

Steiner tree approximation is a quick and accurate way to estimate net length. Figure 2.2 illustrates this approximation method. For each net, a bounding rectangle is determined. The rectangle is partitioned into two parts depending upon the smaller dimension. If the width (height) of the rectangle is more than the other dimension, then the rectangle is partitioned into two parts by a horizontal (vertical) line passing through the center of the net. The *length* of the tree will be the distance of the bisecting line and the summation of all the projections from the center of

net blocks to the bisecting line. In Figure 2.2 rectangle is partitioned horizontally because the width of the rectangle is more than the height. This scheme provides a quick and good estimation of the wire length.

Figure 2.2: Steiner tree approximation for estimation of interconnect length. The length of the tree is distance of the bisecting line (W) and depth is  $\sum_{i=1}^{n} h_i$ .

## 2.4.2 Layout Area

In standard cell design, circuit blocks have fixed height and variable widths. Blocks are placed in rows with routing channels separating two adjacent rows. The overall layout area is represented by the rectangle, which bounds these rows and routing channels. In our work, the heights of routing channels are initially estimated and assumed to be fixed. This leaves only width of layout that can be minimized resulting in reduced area. If cells are placed in such a way that all the rows have approximately the same width, then the placement is considered to be good with respect to area.

### 2.4.3 Circuit Delay

From the perspective of a layout generator, the VLSI circuit consists of circuit blocks and interconnection between the blocks. A net is an equipotential interconnect of pins on different cells. One circuit block can be part of many nets. A path is an alternating sequence of blocks and nets from source net to sink net. A source net can be either input pad or output of memory element whereas the sink net can be output pad or input of memory element. Both source and sink of a path are controlled by the same clock.

The overall performance of the VLSI circuit depends upon how fast it can process signals i.e., its clock speed. The propagation delay of signals of a VLSI circuit consists of two elements, switching delay and interconnect delay. Due to improvement in technology, gate switching delays have considerably decreased. The effect of this decrease is that the wiring delay factor becomes prominent in the overall chip delay. The layout generator is concerned with reducing the interconnect delay.

Let path  $\pi$  consist of nets  $\{v_1, v_2, ...., v_k\}$ , then its path delay  $T_{\pi}$  is expressed by the following equation.

$$T_{\pi} = \sum_{i=1}^{k-1} (CD_{v_i} + ID_{v_i})$$

(2.1)

where  $CD_{v_i}$  is the switching delay of the cell driving net  $v_i$  and  $ID_{v_i}$  is the interconnect delay of net  $v_i$ . The overall circuit delay is equal to the  $T_{\pi_c}$  where path  $\pi_c$  is the longest path in the layout (the most critical path).

For a layout generator the switching delay is constant, while the interconnect delay depends on the distance between the members of the net. Using the (lumped) RC delay model, this delay is due to interconnect resistance and capacitance. Since the effect of interconnect resistance is very negligible, we can ignore it. The delay due to interconnect capacitance for net  $v_i$  is given by Equation 2.2.

$$ID_{v_i} = LF_{v_i} \times C_{v_i} \tag{2.2}$$

where  $LF_{v_i}$  is load factor of the driving block and  $C_{v_i}$  is the interconnect capacitance. The load factor is independent of the layout. The interconnect capacitance depends upon the distance between the blocks of the respective net. If two layers of metal are used for routing the nets then following set of equations show how the interconnect capacitance of a net  $v_i$  is computed.

$$C_{v_i} = C_{v_i}^a + C_{v_i}^f (2.3)$$

$$C_{v_i}^a = (C_{m_1} \times L_1^i + C_{m_2} \times L_2^i) \times \omega \tag{2.4}$$

$$C_{n_i}^f = 2 \times ((\omega + L_1^i) \times C_{f_1} + (\omega + L_2^i) \times C_{f_2}$$

(2.5)

where

$C_{v_i}$  = Interconnect capacitance of net  $v_i$ .

$C_{v_i}^a$  = Area Capacitance of net  $v_i$ .

$C_{v_i}^f$  = Fringe Capacitance of net  $v_i$ .

$C_{m_1}$  = Plate capacitance per unit area of metal 1.

$C_{m_2}$  = Plate capacitance per unit area of metal 2.

$C_{f_1}$  = Fringe capacitance per unit length of perimeter of metal 1.

$C_{f_2}$  = Fringe capacitance per unit length of perimeter of metal 2.

$\omega$  = Width of metal 1 or metal 2.

$L_1^i$  = Length of metal 1 used in connecting net  $v_i$ .

$L_2^i$  = Length of metal 2 used in connecting net  $v_i$ .

In Equations 2.3 to 2.5,  $\omega$ ,  $C_{m_1}$ ,  $C_{m_2}$ ,  $C_{f_1}$ ,  $C_{f_2}$  are technology dependent parameters. Section 2.6 gives the characteristics of the technology used in this work.

## 2.5 Net Delay Bounds

As we have seen in Section 2.4.3, the delay of a VLSI circuit depends on the sum of interconnect delay and switching delay of the longest path. A circuit will be free from long-path problems if, for all paths  $\pi \in \Pi$ ,  $SLACK_{\pi} \geq 0$ . A negative slack indicates that circuit will not be able to propagate the signal through path within the required time. The  $SLACK_{\pi}$  is computed as follows.

$$SLACK_{\pi} = LRAT_{\pi} - T_{\pi} \tag{2.6}$$

where  $LRAT_{\pi}$  and  $T_{\pi}$  are the "latest required arrival time" and the "actual arrival time" of the signal to the sink of path  $\pi$ .  $T_{\pi}$  is computed as given in Equation 2.1 while  $LRAT_{\pi}$  depends on the clock period and some technology dependent parameters like clock skew and setup time at the path sink.

Path slacks represent the upper constraints on the delay of respective paths. These constraints can be transformed to the net constraints. However, for a layout to be free from long path problems, net constraints need not be satisfied in their entirety. We have used net bounds obtained by minimax-PERT algorithm [22], that transforms path constraints into net bounds. These bounds are used in fuzzy logic based selection scheme in the simulated evolution algorithm (proposed in Section 4.2.3). Following is a brief description of the problem of determining net constraints and the approach used by minimax-PERT algorithm.

Thus, the net constraints for this net must satisfy the longest path traversing this net. Let  $\pi$  be a path in circuit represented as graph G = (V, E) and  $V_{\pi}$  is the set of vertices it traverses. The delay along path  $\pi$  is given by the Equation 2.1. The switching delay is independent of the layout. Therefore, for the final layout to be free from long path problems, the interconnect delays must satisfy the following

constraint:

$$\sum_{v_i \in V_{\pi}} ID_{v_i} \le LRAT_{\pi} - \sum_{v \in V_{\pi}} CD_{v_i} \quad \forall \pi \in \Pi$$

(2.7)

where  $\Pi$  is the set of all paths in circuit graph G. The net constraints must satisfy the inequality 2.7. Using *minimax* approach, the timing bound for each net  $v_i$  on path  $\pi$  is assigned as follows.

$$u_{v_i}^{\pi} = Slack_{\pi} \times \frac{w_{v_i}}{\sum_{u \in V_{\pi}} w_u}$$

(2.8)

Where

$w_{v_i} =$  the weight of net  $v_i$

$= LF_{v_i} \times AcL_{v_i}$

Let  $\Pi_v$  be the set of paths going through net  $v_i$ . A consistent bound will be minimum of  $u_{v_i}^{\pi}$  bounds for all  $\Pi_v$  paths. We can represent this bound as follows:

$$u_{v_i}^* = \min_{\pi \in \Pi_n} u_{v_i}^{\pi} \tag{2.9}$$

The problem of finding  $u_{v_i}^*$  requires enumerating all the paths in the design. This is an NP-Hard [23]. Minimax-PERT algorithm approximates these bounds after enumerating a polynomial number of paths using a PERT-like trace of the graph. Interested reader can consult [22] for description of this algorithm.

| Metal Type | ω        | Sheet Resistance   | -                            | Fringe Capacitance         |

|------------|----------|--------------------|------------------------------|----------------------------|

|            | (micron) | $\Omega / \square$ | $10^{-4} \text{ pF} / \mu^2$ | $10^{-4} \text{ pF} / \mu$ |

| Metal 1    | 4.0      | 0.06               | 0.26                         | 0.82                       |

| Metal2     | 4.0      | 0.033              | 0.15                         | 0.85                       |

Table 2.1: Technology parameters used in this research.

## 2.6 Technology Details

In our work we have adopted standard cell design using a 2  $\mu$  p-well CMOS technology. The parameters for cells like timing characteristics and dimensions are given in [24]. Furthermore, it is assumed that two layers of routing are used. Metal 1 is used for routing of horizontal tracks and metal 2 is used for routing of vertical tracks. The values of capacitances and resistances of these layers are available in [25]. The values used in our computation are given in Table 2.1. Since the sheet resistance values are very negligible compared to capacitance values, we ignore the effect of resistance on delay.

In order to make interconnect delay as a prominent factor in the overall circuit delay, we have reduced the switching delay  $(CD_{v_i})$  in Equation 2.1 by a factor of 4. It is done to emulate a high speed advanced technology in which switching delays are major portion in the overall circuit delay.

## 2.7 Simulated Evolution (SE) Algorithm

Simulated Evolution (SE) is a general iterative heuristic proposed in [19]. It falls in the category of algorithms which emphasize the behavioral link between parents and offspring, or between reproductive populations, rather than the genetic link [18]. This scheme combines the iterative improvement and constructive perturbation and saves itself from getting trapped in local minima by using stochastic approach. It iteratively operates a sequence of evaluation, selection and allocation (perturbation) on one solution. Using a time homogeneous irreducible Markov chain, Kling and Banerjee [26] showed that algorithm converges in the limit to a global minimum with probability one.

In this section we will review simulated evolution (SE) algorithm in detail, as given in [8].

## 2.7.1 Description of SE Algorithm

The Simulated Evolution is a general heuristic for solving a variety of combinatorial optimization problems. The SE proceeds as follows. It starts with a randomly generated valid initial solution. The main loop of the algorithm consists of three steps: evaluation, selection and allocation. These steps are carried out repetitively in a main loop until some stopping condition is satisfied. Other than these three steps, some input parameters for the algorithm are initialized in an earlier step known as

initialization. Following is the description of these procedures. The pseudo code of the algorithm is given in Figure 2.3.

#### Initialization

Initialization step is carried out only once. It consists of selecting a starting valid solution for the problem under consideration. This solution can be generated randomly or the output of any constructive heuristic. The other important parameters which can be initialized in this step are a stopping condition and selection bias (B). Different stopping conditions can be used. For example, the stopping condition can be a fixed number of iterations of the main loop or a function of improvement in the solution cost. Selection bias is used to compensate errors made in the estimation of the optimum cost used in the computation of goodness (see the evaluation stage below). The selection bias controls the magnitude of the perturbation of current solution. It effects the overall execution speed of the algorithm and the quality of the final solution. A carefully selected value of the bias results in a good quality solution.

#### **Evaluation**

In this step, each individual member of the solution is evaluated on the basis of problem constraints and objectives. This evaluation is represented by the **goodness** for each element of the current solution. The goodness of an element of the design

```

Algorithm Simulated_Evolution(B, \Phi_{initial}, StoppingCondition)

NOTATION

B = Bias Value.

\Phi= Complete Solution.

e_i= Individual cell in \Phi.

O_i= Lower bound on cost of i^{th} cell.

g_i= Goodness of i^{th} cell in \Phi.

C_i= Current cost of i^{th} cell in \Phi.

S= Queue to store the selected cells.

ALLOCATE(e_i, \Phi_i)=Function to allocate e_i in partial solution \Phi_i

Repeat

EVALUATION: For Each e_i \in \Phi DO

begin

g_i = \frac{O_i}{C_i}

end

For Each e_i \in \Phi DO

SELECTION:

begin

IF Random > Min(q_i + B, 1)

THEN

begin

S = S \cup e_i; Remove e_i from \Phi.

end

end

Sort the elements of S

ALLOCATION: For Each e_i \in S DO

begin

ALLOCATE(e_i, \Phi_i)

end

Until

Stopping Condition is satisfied

Return Best solution.

(Simulated_Evolution)

End

```

Figure 2.3: Structure of the simulated evolution algorithm.

is defined as follows.

$$g_i = \frac{o_i}{a_i} \tag{2.10}$$

where  $o_i$  is the optimum value on the cost of element i and  $a_i$  is the actual cost estimate for this element in the current design. The goodness represents a measure of how near each element is to its optimum position. As is obvious from Equation 2.10, the goodness of an element is between 0 and 1. A value of goodness near 1 means that element i is near its optimum location.

#### Selection

The goodness is used to probabilistically select elements in the selection step. Elements with low goodness have a higher probability of getting selected for reposition. Selection bias (B) is used to compensate errors made in estimation of the optimum cost. Its objective is to inflate or deflate the goodness of elements. A high positive value of bias decreases the probability of selection or vice versa. A carefully tuned bias value results in good solution quality and reduced execution time [26]. The selection step results in a partial solution of only unselected elements, while selected elements are saved in a queue for allocation.

#### Allocation

The purpose of the allocation is to perturb the current solution in such a way that the selected elements are assigned to better design positions. The allocation

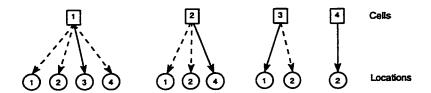

function affects the quality of solution as well as convergence of the search. Different constructive allocation schemes are proposed in [8]. One such scheme is sorted individual best fit, where all the selected elements are sorted in descending order in a queue with respect to their connectivity with the partial solution. The sorted elements are removed one at a time and trial moves are carried out for all the available empty positions at that time. The element is finally placed in a position where maximum reduction in cost for the partial solution is achieved. This process is continued until the selected queue is empty. Figure 2.4 illustrates this scheme for VLSI cell placement. There are four selected VLSI cells and and as many empty locations in the layout. The head of line cell (cell 1) is tried in all four locations and finally placed in slot number 3 because the reduction in cost is maximum. Then second cell is tried on remaining slots and placed in slot 4. This process is repeated for all the remaining selected cells. The overall complexity of this algorithm is  $O(s^2)$ where s is the number of selected elements. Other more elaborate allocation schemes are weighted bipartite matching allocation and branch-and-bound search allocation [8]. However, these schemes are more complex allocation strategies than "sorted individual best fit", but result in comparable solution quality [8]. In this work we have used a fuzzy sorted individual best fit allocation scheme.

Figure 2.4: Sorted individual best fit placement.

## 2.8 Fuzzy Logic

## 2.8.1 Fuzzy Set Theory (FST)

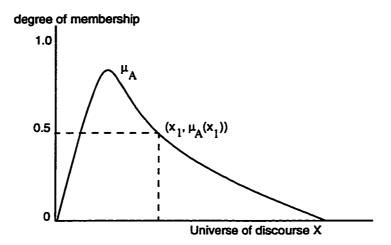

A crisp set is normally defined as a collection of elements or objects  $x \in X$  that can be finite, countable or uncountable. Each single element can either belong to a set or not. However, in real life situations objects do not have crisp [1 or 0] membership criteria. Fuzzy Set Theory (FST) aims to represent vague information, like "very hot" and "quite cold", which are difficult to represent in classical (crisp) set theory. In fuzzy set an element may partially belong to a set. Formally, a fuzzy set is characterized by a membership function which provides a measure of the degree of presence for every element of the set [27, 28]. A fuzzy set A of a universe of discourse X is defined as  $A = \{(x, \mu_A(x)) | all \ x \in X\}$ , where  $\mu_A(x)$  is a memerbership function of  $x \in X$  being an element in A [29]. Figure 2.5 shows one example of a membership function.

Like crisp sets, set operations such as union, intersection, and complementation etc., are also defined on fuzzy sets. There are many operators for fuzzy union and fuzzy intersection. For fuzzy union, the operators are known as s-norm operators

Figure 2.5: Membership function for a fuzzy set A.

(denoted as  $\oplus$ ). While fuzzy intersection operators are known as **t-norm** (denoted as \*). Some examples of **s-norm** operators are given below, (where A and B are fuzzy sets of universe of discourse X) [27].

- 1. Maximum.  $[\mu_{A \bigcup B}(x) = \max[\mu_A(x), \mu_B(x)]]$ .

- 2. Algebraic sum.  $[\mu_{A \bigcup B}(x) = \mu_{A}(x) + \mu_{B}(x) \mu_{A}(x)\mu_{B}(x)]$ .

- 3. Bounded sum. [  $\mu_{A \bigcup B}(x) = \min(1, \mu_A(x) + \mu_B(x))$ ].

- 4. Drastic sum. [  $\mu_{A \bigcup B}(x) = \mu_{A}(x)$  if  $\mu_{B}(x) = 0$ ,  $\mu_{B}(x)$  if  $\mu_{A}(x) = 0$ , 1 if  $\mu_{A}(x)$ ,  $\mu_{B}(x) > 0$ ].

An s-norm operator satisfies commutativity, monotonicity, associativity and  $\mu_{A \cup 0} = \mu_{A}$  properties. Following are some examples of fuzzy intersection operators known as t-norm.

- 1. Minimum.  $[\mu_A \cap B(x) = \min[\mu_A(x), \mu_B(x)]]$ .

- 2. Algebraic product.  $[\mu_{A \cap B}(x) = \mu_{A}(x)\mu_{B}(x)]$ .

- 3. Bounded product. [  $\mu_{A \cap B}(x) = \max(0, \mu_A(x) + \mu_B(x) 1)$ ].

- 4. Drastic product.  $[\mu_{A \cap B}(x) = \mu_{A}(x) \text{ if } \mu_{B}(x) = 1, \mu_{B}(x) \text{ if } \mu_{A}(x) = 1, 0 \text{ if } \mu_{A}(x), \mu_{B}(x) < 1].$

Like s-norms, t-norms also satisfy commutativity, monotonicity, associativity and  $\mu_{A \cap 1} = \mu_A$  properties. Additionally, the membership function for fuzzy complementation operator is defined as.

$$\mu_{\overline{B}}(x) = 1 - \mu_B(x)$$

### Ordered Weighted Averaging Operator

Generally, formulation of multi criteria decision functions do not desire pure "anding" of t-norm nor the pure "oring" of s-norm. The reason for this is the complete lack of compensation of t-norm for any partial fulfillment and complete submission of s-norm to fulfillment of any criteria. Also the indifference to the individual criteria of each of these two forms of operators led to the development of Ordered Weighted Averaging (OWA) operators [30]. This operator allows easy adjustment of the degree of "anding" and "oring" embedded in the aggregation. According to [30], "orlike" and "andlike" OWA for two fuzzy sets A and B are implemented as given

in Equations 2.11 and 2.12 respectively.

$$\mu_{A \cup B}(x) = \beta \times \max(\mu_A, \mu_B) + (1 - \beta) \times \frac{1}{2}(\mu_A + \mu_B)$$

(2.11)

$$\mu_{A \cap B}(x) = \beta \times \min(\mu_A, \mu_B) + (1 - \beta) \times \frac{1}{2}(\mu_A + \mu_B)$$

(2.12)

$\beta$  is a constant parameter in the range [0,1]. It represents the degree to which OWA operator resembles a pure "or" or pure "and" respectively.

### 2.8.2 Fuzzy reasoning

Fuzzy reasoning is a mathematical discipline invented to express human reasoning in vigorous mathematical notation. Unlike classical reasoning in which propositions are either true or false, fuzzy logic establishes approximate truth value of propositions based on linguistic variables and inference rules. In order to represent imprecise ideas, Zadeh [31] introduced the concept of linguistic variable. A linguistic variable is a variable whose values are words or sentences in natural or artificial language [32]. The set of values a linguistic variable can take is called a term set. This set is constructed by means of primary terms and by placing modifiers known as hedges like "more", "many", "few" etc., before primary terms. The term set represents a precise syntax in order to form a vast range of values the linguistic variable can take. The linguistic variables can be composed to form propositions using connectors like AND, OR and NOT. Formally, a linguistic variable comprises five elements [33].

- 1. The variable name.

- 2. The primary term set.

- 3. The Universe of discourse U.

- 4. A set of syntactical rules that allows composition of the primary terms and hedges to generate the term set.

- A set of semantic rules that assigns each element in the term set a linguistic meaning.

For example, wire length can be used as linguistic variable for VLSI cell placement problem. According to the syntactical rule, the set of linguistic values of wire length may be defined as very small wire length, small wire length, somewhat small wire length, large wire length. The universe of discourse for linguistic variable is possible range of wire length for some designs. For instance, universe of discourse for linguistic variable wire length can be the interval  $[100000 \ \mu, 150000 \ \mu]$ . The set of semantic rules define fuzzy sets for each linguistic value. A linguistic value is characterized by its corresponding fuzzy set. The membership in fuzzy set is controlled by membership functions like Figure 2.5. It shows the designer's knowledge of the problem.

### 2.9 Conclusion

In this chapter we have seen relevant material necessary to understand subsequent chapters. We have defined the VLSI cell placement problem and reviewed the cost functions with respect to interconnect wire length, layout area and circuit delay. We have also seen the transformation of path delay constraints into net constraints. We will later use these constraints in the SE based placement scheme to improve the circuit delay. The technology dependent constants and parameters are also given .

In this chapter we have also reviewed the simulated evolution heuristic and fuzzy logic. This heuristic is a powerful stochastic iterative heuristic for general combinatorial optimization problems. It is based on the analogy between optimization and evolutionary processes. Underlying principle of this heuristic is that evolutionary system be subjected to the evaluation process such that it stochastically discards inferior parts and retains superior parts of the system. The constructive perturbation in allocation stage ensures that the algorithm will converge to a suboptimal solution. On the other hand, fuzzy logic provides a convenient algebra of combining conflicting objectives and expert human knowledge.

## Chapter 3

## Literature Review

#### 3.1 Introduction

The VLSI cell placement problem is an NP-hard problem [34]. The simplified version of this problem is the optimization of wire length for one dimensional placement of cells. Even this simplified problem of optimally placing n cells requires enumeration of n! options. This is impractical even for circuits having few hundred cells. Because of exponential complexity of this problem, clever techniques known as "heuristics" are used to generate near optimal solutions in reasonable amount of time.

In this chapter, we review some of the important studies carried out in this area.

Section 3.2 reviews placement techniques which use crisp knowledge for decision making. Fuzzy logic allows a convenient way of combining human expert knowledge in decision making. Therefore, several studies have used fuzzy logic based decision

making in placement techniques. These studies are reported in Section 3.3. As this research is based on Simulated Evolution Algorithm (described in Section 2.7), therefore we have reviewed the applications of SE on computer-aided design (CAD) problems. This review in reported in Section 3.4.

## 3.2 General Placement Techniques

#### 3.2.1 Constructive Placement

Constructive placement schemes build a placement in a piecewise manner. These schemes assign cells one by one cells are placed. The algorithm starts with an initial solution known as seed. Then other cells are selected (one at a time in order of their connectivity to the placed modules) and placed at a vacant location near to the already placed cells [2]. This process continues until all cells are placed. Such schemes are very fast but fall short of good placement. This is due to the fact that these schemes make decision about placing a cell in a location on the basis of partial placement only. Secondly, once a decision is made, no matter how bad it is, there is no mechanism to reverse it. Therefore, these schemes may remain trapped in local minima.

These algorithms are generally used to generate initial solutions for iterative algorithms. The reason of using these techniques is their fast execution time. Other examples of constructive placement techniques are numerical optimization, place-

ment by partitioning and force directed scheme. These heuristics are surveyed in [2].

#### 3.2.2 Iterative Placement Schemes

In contrast to the constructive techniques, iterative schemes require enormous computational time to generate good placement. Iterative techniques start with an initial solution and repeatedly modify the solution in each iteration until no more improvement occurs. The modification in solution is intended to reduce the cost of the solution. Iterative schemes can be further classified on the basis of whether they can accept bad solutions probabilistically or not. Those iterative algorithms which allow acceptance of bad moves probabilistically fall in the sub-category of "stochastic iterative algorithms". This property is called "hill climbing property". It saves algorithms from getting trapped in local minima. However, it is required that the acceptance of bad moves be controlled to avoid random traversal of search space. Examples of such probabilistic iterative schemes are simulated annealing (SA), genetic algorithm (GA) and simulated evolution (SE).

There are iterative heuristics which do not allow acceptance of bad moves. These schemes are known as "deterministic iterative techniques". Examples of such techniques are min-cut, force directed interchange and local search etc. These schemes are discussed in [1, 2].

#### **Stochastic Iterative Schemes**

Three stochastic iterative algorithms have been successfully applied on the VLSI cell placement problem. These algorithms are simulated annealing (SA) [6], genetic algorithm (GA) [35], and simulated evolution (SE) [19]. Following is a brief review of these implementations.

#### Simulated Annealing

Simulated Annealing is a popular combinatorial optimization algorithm proposed by Kirkpatrick et. al. [6]. It is derived from the analogy of the physical annealing process of metals. SA works on a single solution. The neighborhood state of the solution is generated by randomly selecting modules and interchanging their positions. All good moves are accepted. However, bad moves are stochastically accepted. The acceptance probability of bad moves is controlled by a cooling schedule. In early stages of the search, number of bad moves are accepted with high probability. However, as search progresses, cooling temperature decreases, so does the probability of accepting bad moves. In the last part of the search, SA behaves as a greedy algorithm, accepting only the good moves. For details of simulated annealing algorithm interested readers are referred to [5].

Sechen [36] used SA to solve the VLSI placement problem. Their implementation is known as Timberwolf. The algorithm performs placement and routing in three stages. The first stage is concerned with the cell placement in order to reduce

interconnect wire length. A neighbor function produces new states by making a random selection from three perturb functions i) move a single cell to a new location ii) swap two cells iii) mirror a cell about the x-axis. The cost function contains total estimated wire length, penalty for cell overlap and length of the row exceeding (or falling short of) the expected length. The annealing process is started at a very high temperature. Initially the temperature falls very rapidly. In intermediate range the temperature is reduced slowly and in the final stage it again falls rapidly. Most of the improvement in the quality of solution is achieved in the intermediate temperature range. The remaining two stages of the algorithm are concerned with routing.

In order to reduce the execution time of SA, Mallela et. al. [15] proposed a clustering based SA for the standard cell placement. In the first stage, using SA they place clusters of cells formed on the basis of interconnections. In the second stage, the clusters are broken into individual cells and then cells are placed using SA. This hierarchal SA reduces the problem size without compromising on the quality of solution.

Simulated annealing is a very successful heuristic for combinatorial optimization. However, it suffers from two major drawbacks. It requires careful tuning of its control parameters and it also needs excessive computation time [37]. Tao et. al., in [17] have shown that SA takes more execution time due to non aggressive neighborhood search. During each iteration of SA, algorithm chooses a random

neighboring solution which is not always most profitable one. The real cost improves mostly in a narrow time range.

#### Genetic Algorithm

Genetic Algorithm (GA) is another powerful and popular optimization algorithm which works by emulating the natural process of evolution as a means of progressing toward the optimum. It was invented by Holland [35]. Unlike SA which works repeatedly on single solution, GA works on a set of solutions in parallel. The set of solutions are known as a population. Each solution is represented by a string of symbols known as chromosome. Four genetic operators namely selection, crossover, mutation and inversion are repeatedly applied on a collection of solutions to generate new offsprings. Extensive literature is available on genetic algorithms and their use in combinatorial optimization problems. Interested reader is referred to [5, 7].

Cohoon et. al. [38] used GA for VLSI cell placement. They proposed an algorithm with the name "Genie". In their algorithm, initial population is a mix of individuals generated by two methods. They have used randomly generated individuals along with individuals generated by a greedy constructive heuristic. If the entire population consists of individuals generated using a greedy constructive heuristics then genetic algorithm converges prematurely to a local minimum. The presence of random layouts in initial population provides diversification. Fitness of individual solution is determined on the basis of interconnect wire length only. The

fitness function does not account for possible cell overlaps or variation in row length. Different types of parent choice functions, crossover operators and individual survival functions were tested. They compared results of GA with that of SA for five circuits. GA was able to generate same quality solution in two cases while in other three tests quality was up to 7% worse than SA.

Shahookar et. al., [2, 9] also implemented GA for the VLSI placement and compared the performance of their algorithm using different crossover operators, like partially mapped (PMX), cycle and order crossover. They used an initial population of randomly generated individuals. The fitness function of an individual was equal to the reciprocal of its total interconnect wire length estimate. Inversion or mutation genetic operators were also used with different probabilities. After crossover the fitness of offspring is evaluated and the population for the next generation is selected from the population of offsprings and parents. According to their study, PMX or cycle crossover performed best, while order crossover was the worst. The quality of final solution generated by GASP was comparable with the results of Timberwolf [2, 9].

Khalid [39] investigated the use of GA for multi-objective optimization of the VLSI cell placement. Not only wire length but also circuit delay and layout area was optimized. The crossover operators were geared to transfer information about satisfied paths (sequence of nets from input to output which transfer signal in same clock pulse) to next generation. This resulted in timing improvement of up to 17%

against a min-cut placer.

Holt et. al. [12] proposed GEEP, a GA based low power layout system. GEEP reduces interconnect capacitance by an average of 20% over recursive min-cut area optimizing placement. They included the low population diversity in GA to achieve fast execution time.

Genetic algorithm requires extensive computational time and high memory. Furthermore, when population has individuals with equal fitness then it is likely that GA will converge prematurely [18].

#### Simulated Evolution

Simulated Evolution (SE) is also an iterative heuristic proposed by Kling and Banerjee [8]. This algorithm is inspired by the simulated annealing. However, instead of

carrying out a random selection and stochastic perturbation as in the case of SA,

simulated evolution uses stochastic selection based on individual goodness and constructive perturbation. Due to these characteristics SE can generate near optimal

solutions in reduced execution time than SA. Kling and Banerjee applied SE for VLSI

placement problem and achieved solution quality comparable to SA in considerably

less execution time. Simulated Evolution algorithm is described in Section 2.7.

## 3.3 Fuzzy Logic Based Placement Schemes

VLSI cell placement problem contains multiple conflicting objectives. As an example, if we are optimizing wire length and layout area, it is possible that one particular move in an iterative algorithm reduces area but increases wire length. It is difficult to decide whether this type of move is good or bad. Use of crisp logic for such situations will not be able to represent the expert opinion. Therefore, fuzzy logic provides an alternative reasoning mechanism which can satisfy conflicting objectives by using expert human knowledge [32]. Fuzzy logic has been used in VLSI design automation problems. Most of the schemes proposed in the literature use fuzzy logic in constructive heuristics. Following is a brief review of some of the schemes.

Lin et. al., in [32] discuss their implementation of fuzzy rule based sea of gates placement mechanism. It is a constructive cluster growth heuristic in which decisions regarding which cell to select, and where to place it, are carried out using fuzzy logic. Fuzzy logic was used to facilitate multi-objective decision making among conflicting placement objectives like reducing wire length, layout area and circuit delay. Similarly in [40], constructive placement scheme is described in which fuzzy logic is used to construct a connection matrix to represent the 'true' degree of connectivity between cells. The extension of this work is reported in [41]. The authors have proposed a hierarchical placement strategy. In the first stage, a connection matrix is formed which is used in the fuzzy similarity process for clustering. In the

second stage, final placement is carried out by using fuzzy c-means clustering and linear ordering process to partition the modules. It is reported that this constructive algorithm has overall complexity of  $O(n^{2.5})$  where n is the number of modules.

Ball et. al., in [42] describe two methods of constructive partitioning and placement. Both schemes are based on *fuzzy c-means* algorithm. The first method minimizes wire length by force directed relaxation and fast clustering technique. The second method uses fuzzy similarity relation for specifying similarities between the cells. The set of modules are partitioned into subsets based on their characteristic features such as connectivity, size, aspect-ratios, power consumption etc.

Mackey et. al., in [43], describe a performance driven macro cell placement algorithm. Their technique optimizes inter-device delay by using a quad-partitioning algorithm with tabu search and fuzzy cost function. The algorithm repeatedly quad-partitions the layout, places the cells in regions and optimizes the regions by doing cell movements and cell swaps across the regions. This partitioning and optimization continues until the number of cells in each region is small enough to be easily placed. Three values contribute to fuzzy cost of a solution: total path length cut by region boundaries, maximum path length cut by region boundaries and total number of paths cut by region boundaries. It is claimed that fuzzy based cost function improves the placement by shortening the longest path through the circuit.

Yukimatsu et. al., in [44] give the description of hierarchical fuzzy expert system for placement of parts on printed circuit board. Their scheme starts with dividing the

set of parts into several blocks. The presence of parts in the blocks is given by fuzzy values, which represent the degree of belonging (DOB). Each block is represented by one major component. In the first stage of placement, these blocks are placed on the layout using simulated annealing, ignoring the area of blocks. Then placement areas are assigned taking into consideration the DOBs of the components. These areas can overlap. In the second stage parts are placed based on the rough placement according to their DOBs to the blocks. Each position of the device is optimized using constructive heuristics. Results show that the final solution is feasible.

Hakeem [45], used fuzzy logic based genetic algorithm (GA) for the floorplanning problem. Floorplanning problem is also a hard problem of VLSI physical design stage. It is carried out before placement and finds locations of macro blocks on a layout. His proposed fuzzy GA scheme used the fuzzy decision making approach for cost computation. He reported comparable results to a weighted sum approach.

## 3.4 Applications of SE algorithms

Simulated Evolution (SE) was proposed as a general iterative heuristic. It has been used in optimization of number of problems related to computer-aided design (CAD). Following is a brief review of some studies which use SE for combinatorial optimization problems in CAD.

Ly et. al. [46] have used SE for high level synthesis problem. A high level

synthesis tool maps the abstract behavior specifications (like algorithm) represented by control/data flow graphs (CDFG) into data path circuit and a finite state machine (FSM) description. The FSM specifies the controller required to sequence the data path through control steps. The synthesis task can be divided into two sub-tasks namely scheduling and allocation. The scheduling is concerned with assignment of each node of CDFG to a control step such that all conflicts due to data/control flow dependencies are resolved. The allocation task is concerned with assigning hardware cells to CDFG nodes and edges so that resulting circuit can implement the algorithm. In [46] authors have formulated scheduling and allocation steps of high level synthesis as optimum assignment problem. SE algorithm is applied for both steps. Scheduling is carried out first and then allocation is determined so that hardware (or area) is reduced. The results of experiments show that SE based synthesis requires less run times to generate designs as well as quality of final generated solution is comparable to existing schemes.

Asynchronous pipeline design requires a well-designed interconnection circuit. This design results in high speed performance by eliminating the clock skew problems of synchronous system. Kuw et. al. have reported study of partitioning and scheduling of asynchronous pipelines [47]. The scheduling of operations into stages is carried out by using simulated evolution algorithm. For two test cases, their implementation was able to achieve sub-optimal solutions.

In [48] SE algorithm is used to solve gate-matrix layout problem. The gate-

matrix layout problem is solved as a one-dimensional transistor gates placement problem. After generating a constructive solution, the algorithm repeatedly works on it by removing ill fit designs based on their individual goodness and re-allocating them to empty slots. As reported in [48] authors obtained good results.

Routing of VLSI circuits is another NP-complete problem [1]. There are several studies in recent years which use SE in one form or the other to solve this problem. For example Wang et. al. have used SE for rip-up and re-route steps in order to resolve the channel capacity violations of initial routing step [49]. In order to decrease path delays of circuit, their implementation works on critical path based routing rather than net based routing. Similarly Yuh et. al. have used SE based performance and routability driven router algorithm for field programmable gate arrays (FPGAs) [20]. In the first stage of the algorithm, nets are routed sequentially according to their criticality. In the second stage, violating nets/paths with respect to routing resource and timing constraints are ripped up and re-routed. For this stage SE heuristic is used to find near optimal solution. Experimental results show that their implementation gives better results with respect to reduction in delay and improvement in routability over many existing routing algorithm. Similarly in [50, 51, 52] SE has been used for VLSI routing problem.

## 3.5 Conclusion

In this chapter we reviewed VLSI placement schemes. One can broadly classify these schemes on the basis of how they build the solution. Constructive schemes use a piece wise placement strategy in which individual cells are placed one by one until complete layout is ready. Iterative schemes work on a complete solution and repeatedly try to improve the quality of layout. If the selection of a move is greedy i.e., always accepting good moves, then such a scheme is sub-classified as deterministic iterative heuristic. Constructive schemes and deterministic iterative heuristics are likely to be trapped in local minima because of their narrow view and limited traversal of search space.

Stochastic iterative heuristics are iterative heuristics which allow probabilistic acceptance of bad moves. Although these heuristics are very time consuming, they guarantee generation of sub-optimal solution. One characteristic of these schemes is that they carry out a controlled walk in the search space. Examples of such heuristics are simulated annealing, genetic algorithm, simulated evolution etc. Detail reviews of these and other algorithms are found in [5].