### Design and Analysis of a High-Performance Fault-Tolerant ATM Network

by

Ghaleb A. Al-Hashim

A Thesis Presented to the

FACULTY OF THE COLLEGE OF GRADUATE STUDIES

KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

MASTER OF SCIENCE

In

**COMPUTER ENGINEERING**

May, 1998

**INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI

films the text directly from the original or copy submitted. Thus, some

thesis and dissertation copies are in typewriter face, while others may be

from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the

copy submitted. Broken or indistinct print, colored or poor quality

illustrations and photographs, print bleedthrough, substandard margins,

and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete

manuscript and there are missing pages, these will be noted. Also, if

unauthorized copyright material had to be removed, a note will indicate

the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by

sectioning the original, beginning at the upper left-hand corner and

continuing from left to right in equal sections with small overlaps. Each

original is also photographed in one exposure and is included in reduced

form at the back of the book.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white

photographic prints are available for any photographs or illustrations

appearing in this copy for an additional charge. Contact UMI directly to

order.

UMI

A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor MI 48106-1346 USA 313/761-4700 800/521-0600

# DESIGN AND ANALYSIS OF A HIGH-PERFORMANCE FAULT-TOLERANT ATM NETWORK BY GHALEB A. AL-HASHIM A Thesis Presented to the FACULTY OF THE COLLEGE OF GRADUATE STUDIES KING FAHD UNIVERSITY OF PETROLEUM & MINERALS DHAHRAN, SAUDI ARABIA In Partial Fulfillment of the Requirements for the Degree of MASTER OF SCIENCE In COMPUTER ENGINEERING MAY 1998

UMI Number: 1390778

UMI Microform 1390778 Copyright 1998, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

300 North Zeeb Road Ann Arbor, MI 48103

# KING FAHD UNIVERSITY OF PETROLEUM & MINERALS DHAHRAN, SAUDI ARABIA

This thesis, written by

### **GHALEB A. AL-HASHIM**

under the direction of his thesis committee, and approved by all the members, has been presented to and accepted by the Dean of the College of Graduate Studies, in partial fulfillment of the requirements for the degree of

### MASTER OF SCIENCE IN COMPUTER ENGINEERING.

**Thesis Committee**

r. Mostafa I. Abd-El-Barr Chairman)

98

Dr. Khalid M. Al-Tawil (Member)

Dr. Hasan Cam (Member)

Department Chairman

Dean, College of Graduate Studies

Date: 10/6/98

Dedicated to

my parents and my family.

### Acknowledgments

I thank Allah, the Lord of worlds, for His mercy and limitless help and guidance. May peace and blessings be upon Mohammed the last of the messengers.

Acknowledgment is due to KFUPM for the support of this project.

I would like to express my deep appreciation to my Thesis advisor Dr. M. I. Abd-El-Barr for his invaluable advice and encouragement. I also wish to thank the other members of my Thesis committee Dr. K. M. Al-Tawil and Dr. H. Cam for their helpful suggestions and comments.

My thanks go also to my friends and colleagues, especially Mr. W. K. Al-Marhoon, Mr. T. M. Al-Nemer, and my cousin Mr. T. H. Al-Hashim, for their support and encouragement.

I am grateful to my family, especially my wife and children for their patience and understanding during my busy schedule.

# **Contents**

| ACKNOWLEDGMENTS                                                 |                                         |

|-----------------------------------------------------------------|-----------------------------------------|

| CONTENTS                                                        | · ]                                     |

| LIST OF FIGURES                                                 |                                         |

| LIST OF TABLES                                                  | X                                       |

| ABSTRACT (ENGLISH)                                              |                                         |

| ABSTRACT (ARABIC)                                               |                                         |

| CHAPTER 1                                                       | •====================================== |

| INTRODUCTION                                                    |                                         |

| CHAPTER 2                                                       | 12                                      |

| LITERATURE SURVEY ON ATM SWITCH ARCHITECTURES                   |                                         |

| 2.1 MOTIVATION 2.1.1 Integrated Services Digital Network (ISDN) | 12                                      |

| 2.1.2 Broadband ISDN                                            | 15                                      |

| 2.3.1 Time-Division Architectures                               | 35<br>36                                |

| 2.3.1.1 Shared-memory Type2.3.1.2 Shared-medium Type            | 36                                      |

| 2.3.2 Space-Division Architectures                              |                                         |

| 2.3.2.1 Crossbar type                                           | 45                                      |

| 2.3.2.2 N <sup>2</sup> Disjoint Paths type         |     |

|----------------------------------------------------|-----|

| 2.3.2.3 Banyan-Based type                          | 51  |

| 2.3.2.3.1 Non Fault-Tolerant Banyan-Based Networks | 50  |

| Baseline Banyan Network                            | 50  |

| Buffered-Banyan Network                            |     |

| Double Banyan Network                              | 64  |

| Pseudo Randomizer-Banyan Network                   | 65  |

| Randomized Routing-Dilated Banyan Network          | 67  |

| Permutation-Banyan Network                         | 67  |

| Bypass Queues-Banyan Network                       | 67  |

| Batcher-Banyan Network                             | 69  |

| Rerouting-Banyan Network                           | 72  |

| Double Phase Banyan Network                        | 74  |

| Tandem-Banyan Network                              | 76  |

| Pipeline Banyan Network                            | 77  |

| Parallel-Tree Banyan Switching Fabric (PTBSF)      | 80  |

| 2.3.2.3.2 Fault-Tolerant Banyan-Based Networks     | 82  |

| MD-Omega Network                                   | 82  |

| Extra Stage Shuffle-Exchange Network               | 84  |

| Extra Stage Cube Network                           | Q1  |

| Benes' Network                                     | 87  |

| SEROS Switching Element                            | 01  |

| Itoh's Network                                     | 94  |

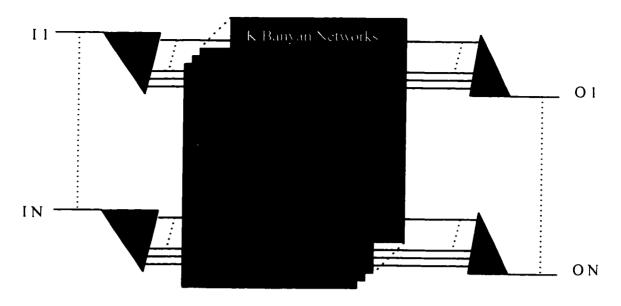

| Parallel Banyan Network                            | 97  |

| Tagle & Sharma's Network                           | 99  |

| Baseline-Tree (B-Tree) Network                     | 101 |

| LIN and WANG's Banyan Network                      | 107 |

| Reliable And Zealous Network (RAZAN)               | 109 |

|                                                    |     |

| CHAPTER 3                                          | 112 |

| PROPOSED SWITCHING FABRIC ARCHITECTURE             | 112 |

| 3.1 DESIGN EVOLUTION                               |     |

|                                                    |     |

| 3.2 BINARY TREE BANYAN NETWORK                     |     |

| 3.2.1 BTBN ARCHITECTURE                            | 130 |

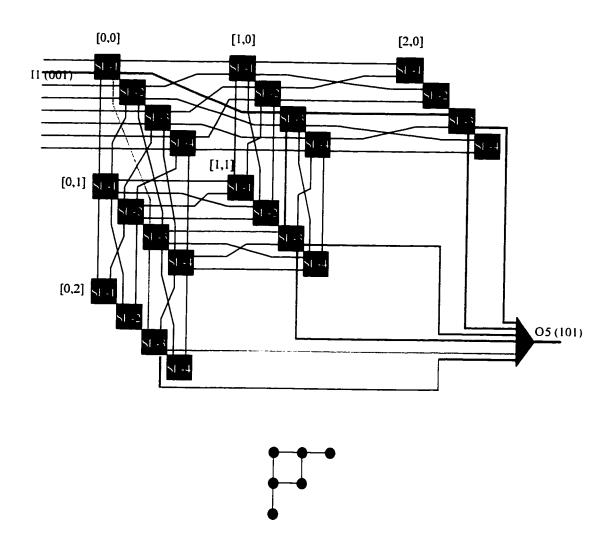

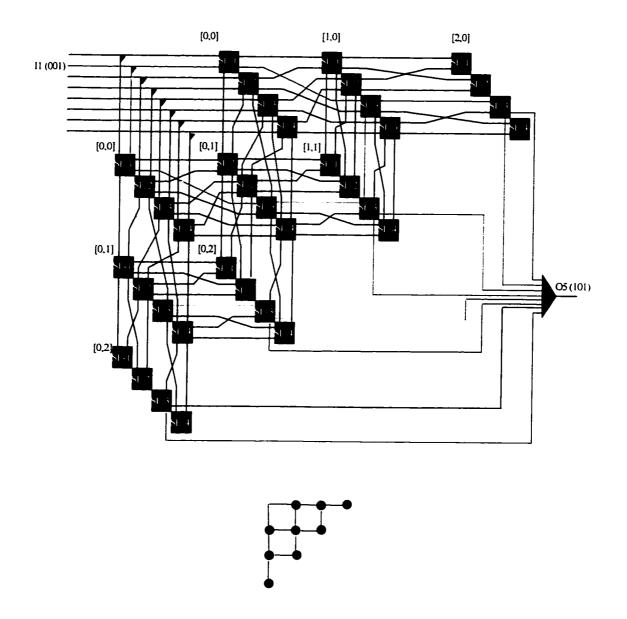

| 3.2.2 BTBN ROUTING                                 | 147 |

| 3.2.3 BIBN COMPLEXITY                              | 162 |

| 3.2.4 BTBN Expandability                           | 161 |

| CHAPTER 4                              | 167  |

|----------------------------------------|------|

| FAULT-FREE BTBN PERFORMANCE EVALUATION | 167  |

| 4.1 PERMUTATION TRAFFIC                | 167  |

| 4.2 UNIFORM TRAFFIC                    | 170  |

| 4.2.1 Analytical Model                 | 170  |

| Parallel Banyan Network                | 171  |

| Tagle and Sharma's Network             | 171  |

| B-Tree (1) Network                     | 175  |

| BTBN Network                           | 178  |

| Analytical Comparison                  | 180  |

| 4.2.2 Analytical Versus Simulation     | 186  |

| 4.3 HOT SPOT TRAFFIC                   |      |

| 4.4 ATM INPUT TRAFFIC                  | 197  |

| 4.4.1 ATM SERVICE REQUIREMENTS         | =- : |

| 4.4.2 ATM TRAFFIC MODELS               | 201  |

| 4.4.3 ATM TRAFFIC SIMULATION           | 204  |

| CHAPTER 5                              | 207  |

| FAULTY BTBN PERFORMANCE EVALUATION     | 207  |

| CHAPTER 6                              | 239  |

| BTBN RELIABILITY ANALYSIS              | 239  |

| CHAPTER 7                              | 250  |

| CONCLUSION AND FUTURE WORK             |      |

| REFERENCES                             |      |

| VITA                                   |      |

# **List of Figures**

| Figure 2.1  | Synchronous Transfer Mode                                                    | 18 |

|-------------|------------------------------------------------------------------------------|----|

| Figure 2.2  | Asynchronous Transfer Mode                                                   | 22 |

| Figure 2.3  | ATM combines the flexibility of packet switching with the                    |    |

|             | simplicity of circuit switching                                              | 22 |

| Figure 2.4  | B-ISDN ATM Protocol Reference Model                                          | 25 |

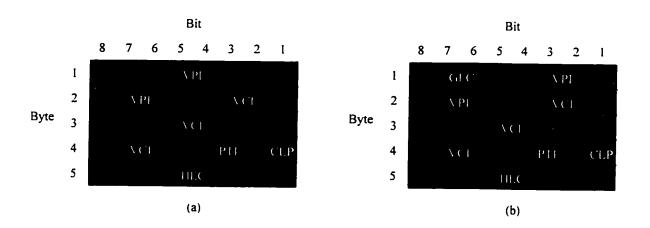

| Figure 2.5  | ATM Cell                                                                     | 28 |

| Figure 2.6  | ATM Cell header structure: (a) NNI; and (b) UNI                              | 28 |

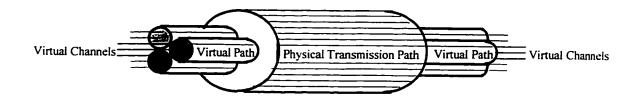

| Figure 2.7  | Relationship between virtual channel, virtual path and transmission path     | 33 |

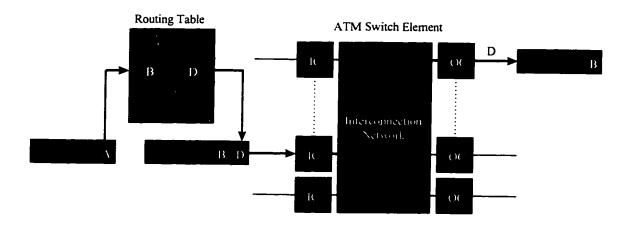

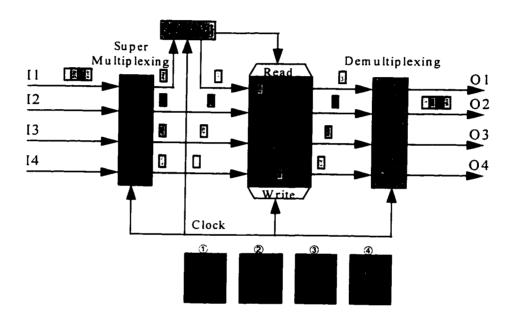

| Figure 2.8  | ATM Cell switching                                                           | 33 |

| Figure 2.9  | Coprin: A 4 X 4 shared-memory ATM switch fabric developed by the French CNET | 37 |

| Figure 2.10 | A 4 X 4 shared-bus ATM switch fabric                                         | 41 |

| Figure 2.11 | ATOM switching fabric architecture                                           | 41 |

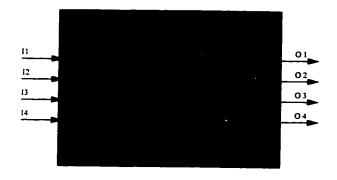

| Figure 2.12 | Abstract reference model for space-division ATM switching                    |    |

|             | fabrics class                                                                | 44 |

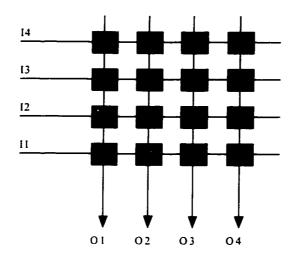

| Figure 2.13 | A 4 X 4 crossbar ATM switch fabric                                           | 46 |

| Figure 2.14 | Nonblocking three-stage space-division switch fabric                         | 46 |

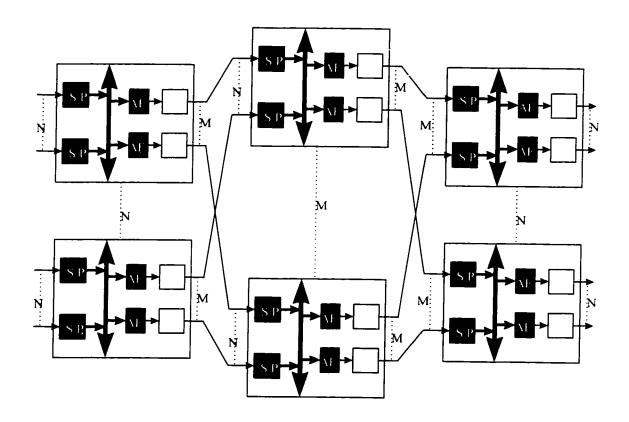

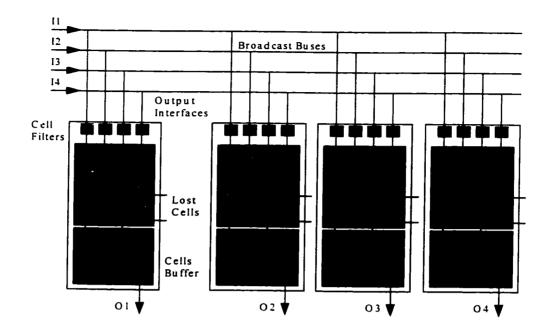

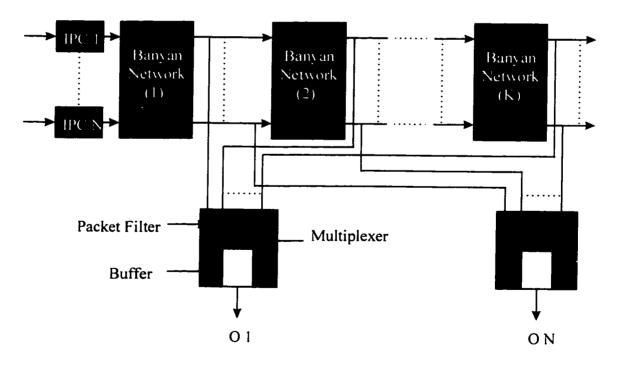

| Figure 2.15 | A 4 X 4 Knockout ATM switch fabric                                           | 49 |

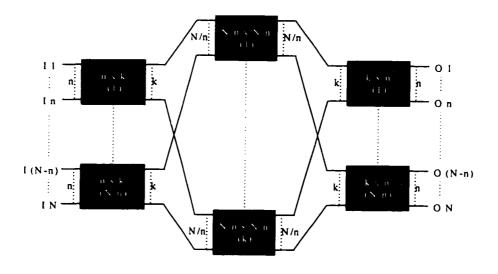

| Figure 2.16 | Modular growth of 2N X 2N Knockout switch                                    | 49 |

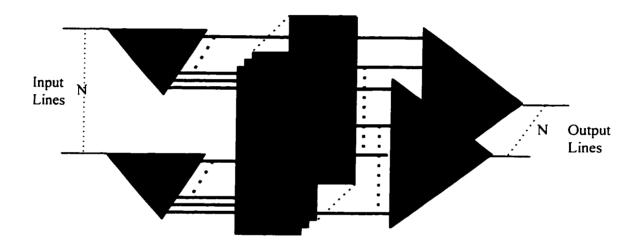

| Figure 2.17 | A 16 X 16 Knockout switch-based MIN                                          | 52 |

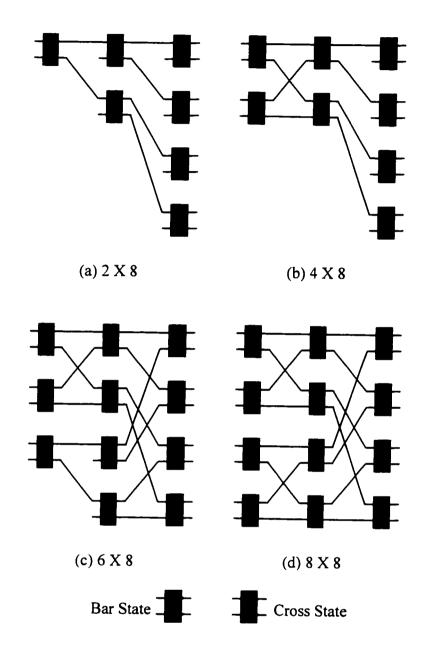

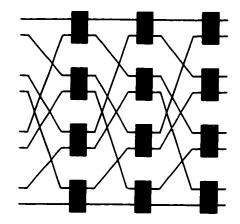

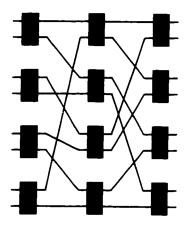

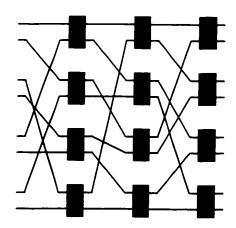

| Figure 2.18 | Constructing an 8 X 8 multistage network using binary switches               | 54 |

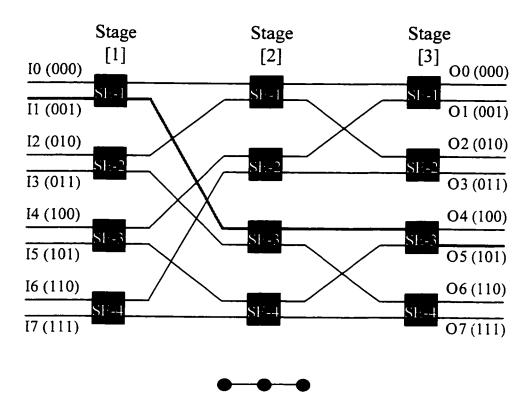

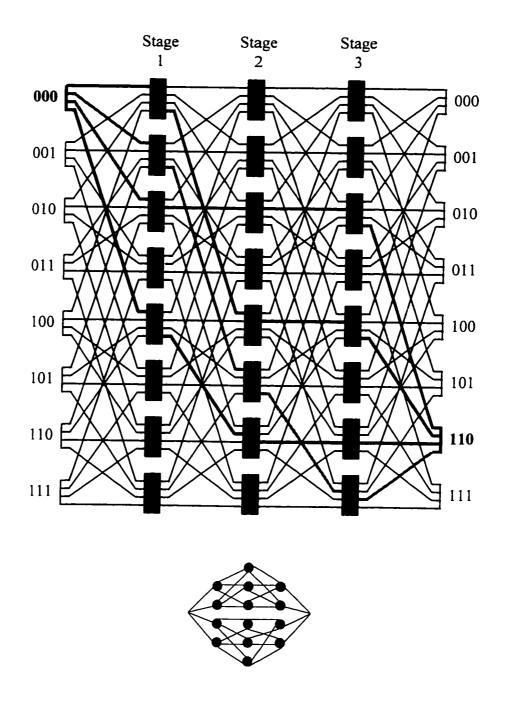

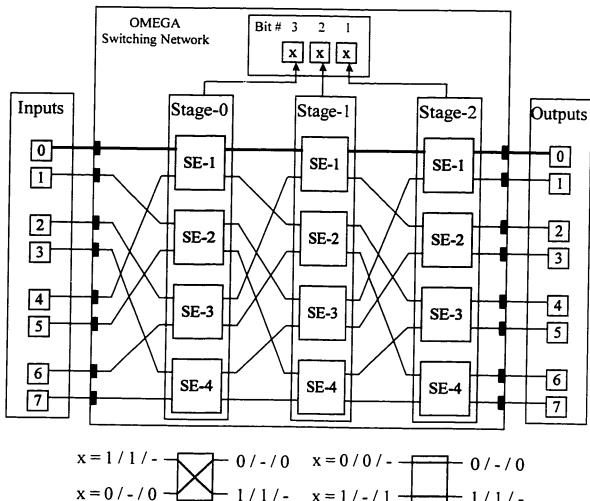

| Figure 2.19 | An 8 X 8 OMEGA multistage network using binary switches                      | 55 |

| Figure 2.20 | An 8 X 8 delta multistage network                                            | 55 |

| Figure 2.21 | A modified 8 X 8 delta multistage network                                    | 55 |

| igure 2.22  |                                                                              | 60 |

| igure 2.23  |                                                                              | 63 |

| igure 2.24  |                                                                              | 63 |

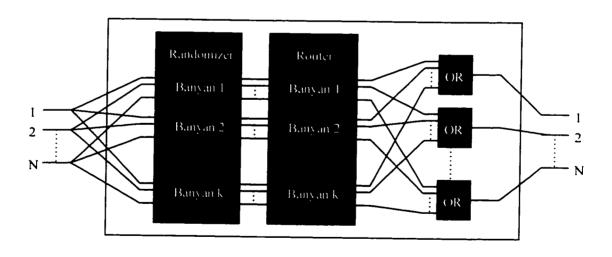

| igure 2.25  |                                                                              | 66 |

| igure 2.26  | An N X N permutation-banyan network                                          | 66 |

| Figure 2.27 | An N X N bypass queues-banyan network                            |

|-------------|------------------------------------------------------------------|

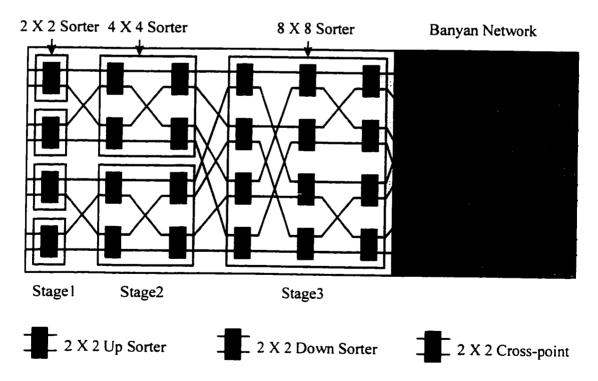

| Figure 2.28 | An 8 X 8 Batcher-banyan network                                  |

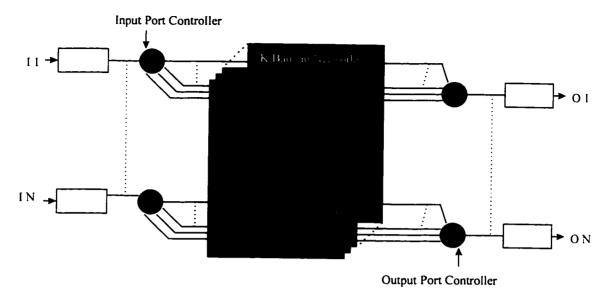

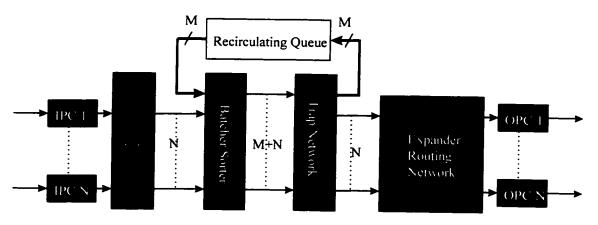

| Figure 2.29 | An N X N Batcher-banyan switching network                        |

| Figure 2.30 | An N X N Batcher-banyan Starlite switching network               |

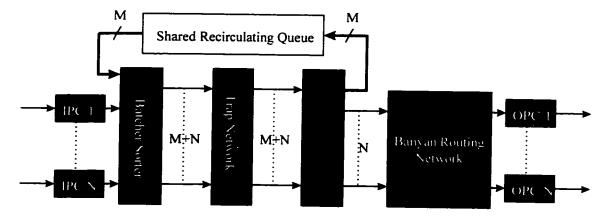

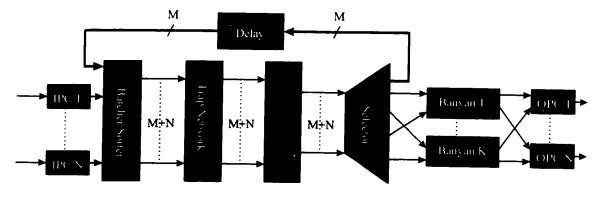

| Figure 2.31 | An N X N Batcher-banyan Sunshine switching network               |

| Figure 2.32 | A 16 X 16 rerouting -banyan network                              |

| Figure 2.33 | An N X N double phase banyan network                             |

| Figure 2.34 | An N X N Tandem-banyan network                                   |

| Figure 2.35 | An N X N pipeline banyan network                                 |

| Figure 2.36 | An 8 X 8 PTBSF                                                   |

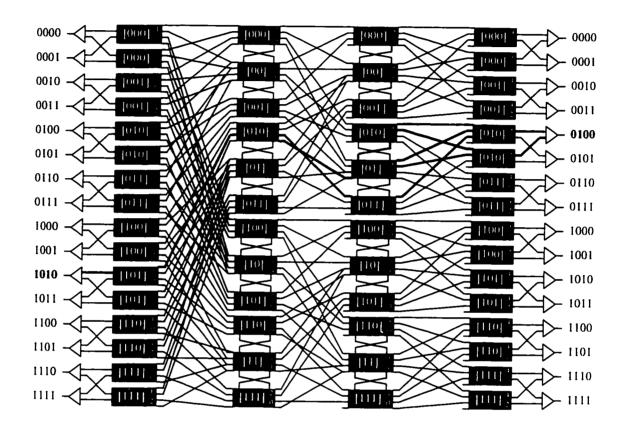

| Figure 2.37 | A 16 X 16 MD-Omega network                                       |

| Figure 2.38 | An 8 X 8 extra stage shuffle-exchange network                    |

| Figure 2.39 | An 8 X 8 extra stage cube network                                |

| Figure 2.40 | An 8 X 8 Benes' network                                          |

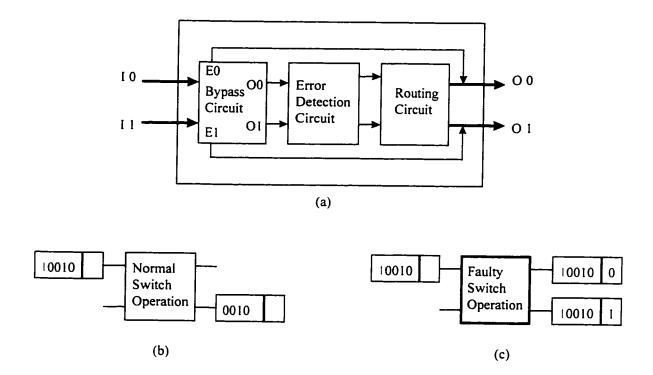

| Figure 2.41 | A 2 X 2 SEROS switch element                                     |

| Figure 2.42 | An 8 X 8 Itoh's network                                          |

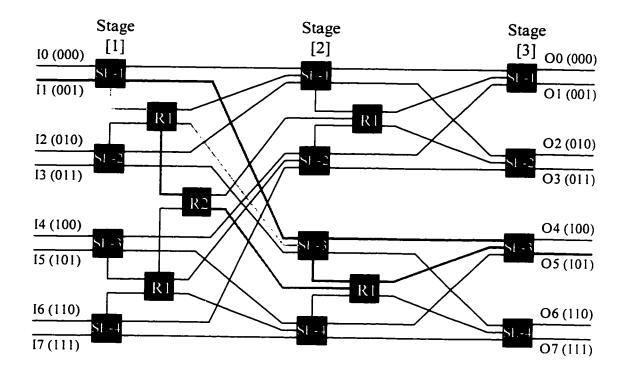

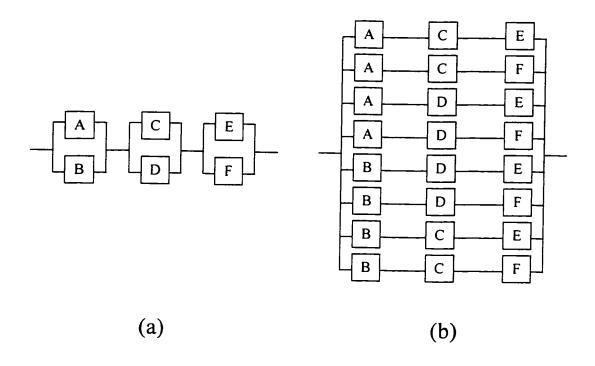

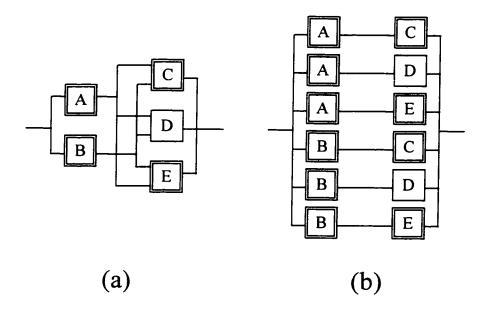

| Figure 2.43 | An 8 X 8 parallel banyan network                                 |

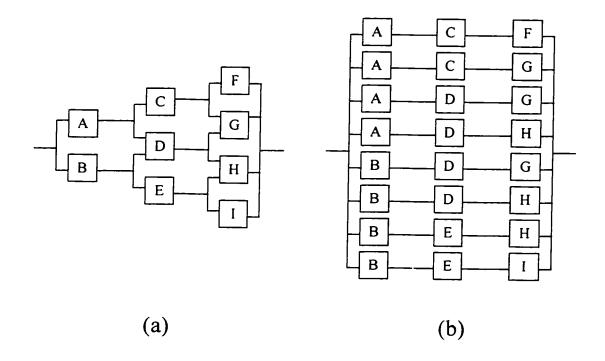

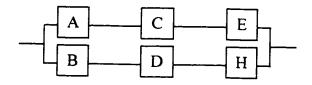

| Figure 2.44 | An 8 X 8 Tagle & Sharma's network                                |

| Figure 2.45 | An 8 X 8 baseline-tree network                                   |

| Figure 2.46 | An 8 X 8 baseline-tree(1) network                                |

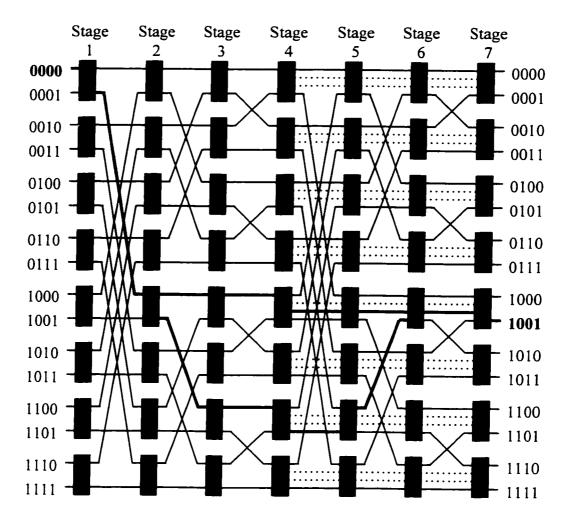

| Figure 2.47 | A 16 X 16 LIN and WANG's banyan network                          |

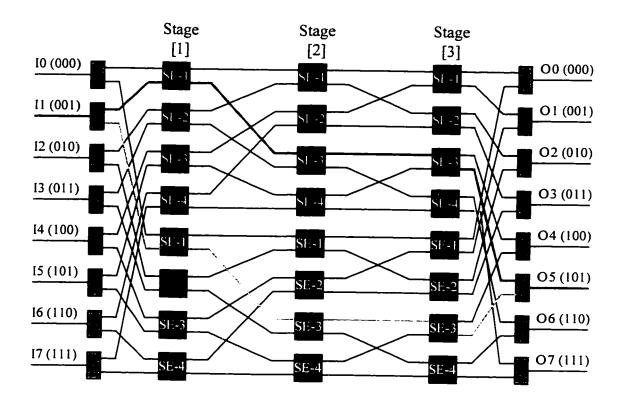

| Figure 2.48 | An 8 X 8 RAZAN network                                           |

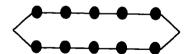

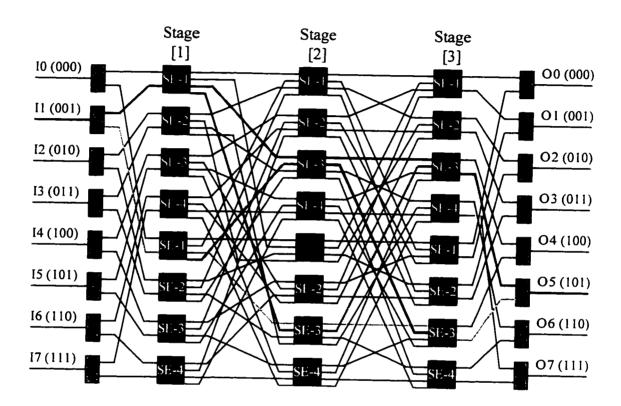

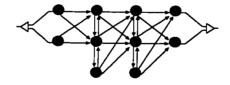

| Figure 3.1  | 8 X 8 shuffle-exchange (Omega) network                           |

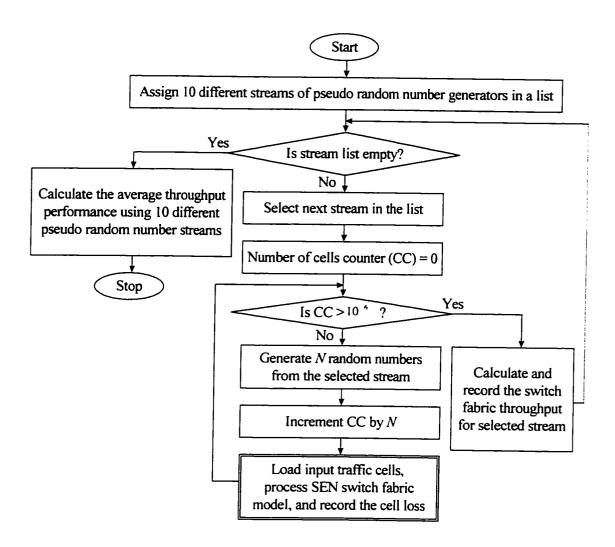

| Figure 3.2  | Experimental design simulation model for SEN                     |

| Figure 3.3  | SEN throughput performance comparison                            |

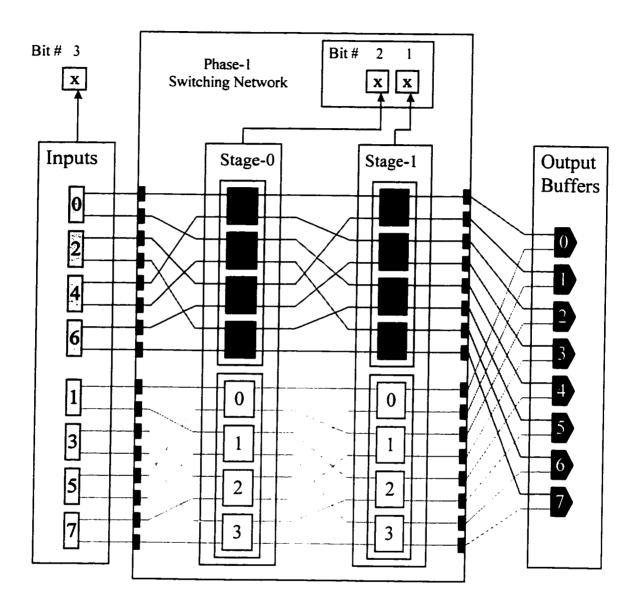

| Figure 3.4  | Phase-1: 8 X 8 switching network                                 |

| Figure 3.5  | Throughput performance of phase-1 and parallel banyan            |

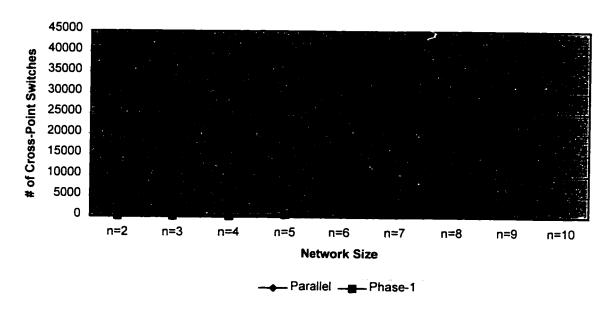

| Figure 3.6  | Cross-point switches complexity of phase-1 and parallel banyan   |

| J           | networks                                                         |

| Figure 3.7  | Interconnection links complexity of phase-1 and parallel banyan  |

| <b>-</b>    | m a + a - l - a                                                  |

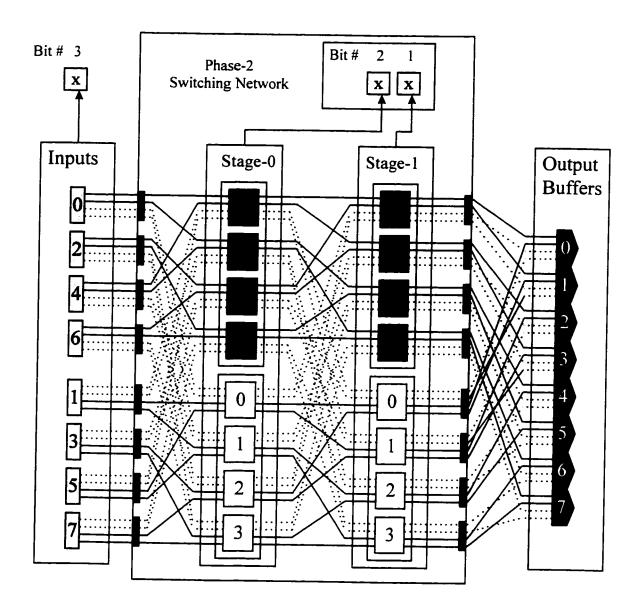

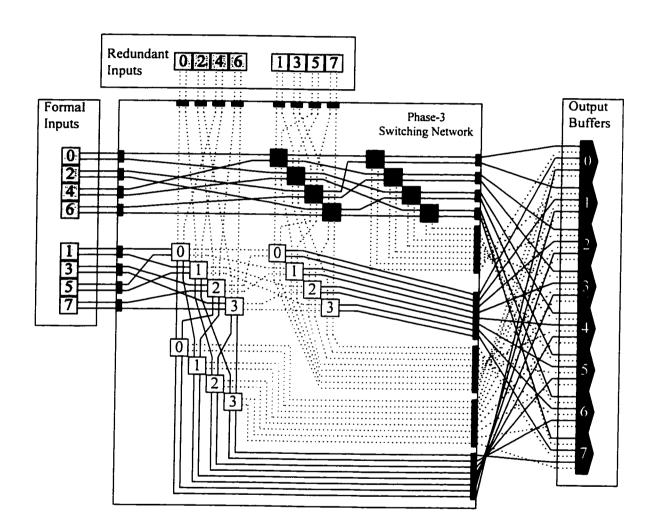

| Figure 3.8  | Phase-2: 8 X 8 switching network                                 |

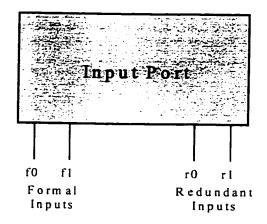

| Figure 3.9  | Input port links                                                 |

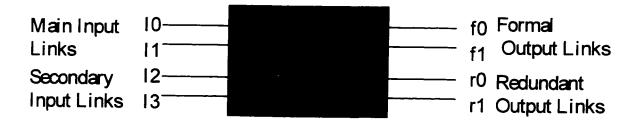

| Figure 3.10 | Phase-2: 4X4 switching element                                   |

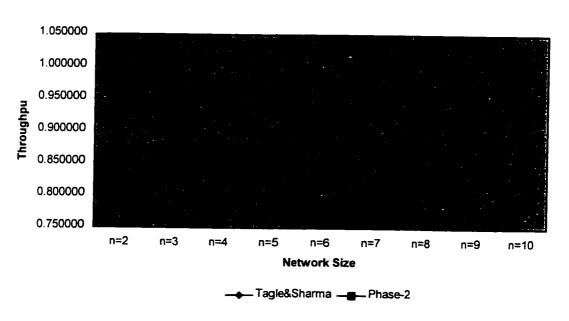

| Figure 3.11 | Throughput performance of phase-2 and Tagle & Sharma's           |

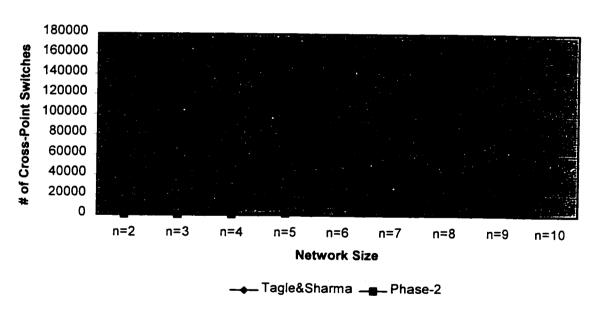

| Figure 3.12 | networks  Cross-point switches complexity of phase-2 and Tagle & |

|             | Sharma's networks                                                |

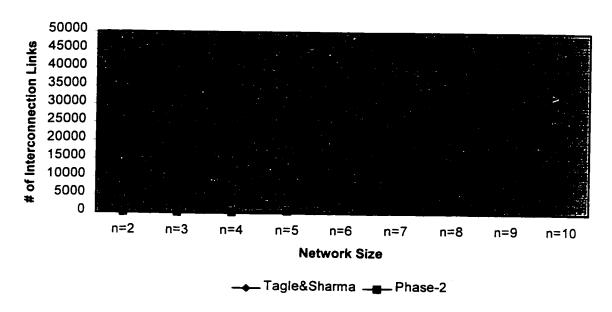

| Figure 3.13 | Interconnection links complexity of phase-2 and Tagle and        |

|             | Sharma's networks                                                   | 13   |

|-------------|---------------------------------------------------------------------|------|

| Figure 3.14 | Phase-3: 8 X 8 switching network                                    | 13   |

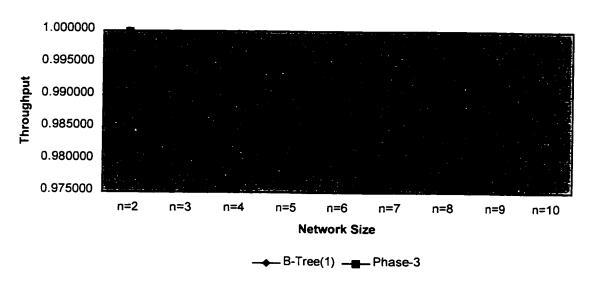

| Figure 3.15 | Throughput performance of phase-3 and B-Tree (1) networks           | 13   |

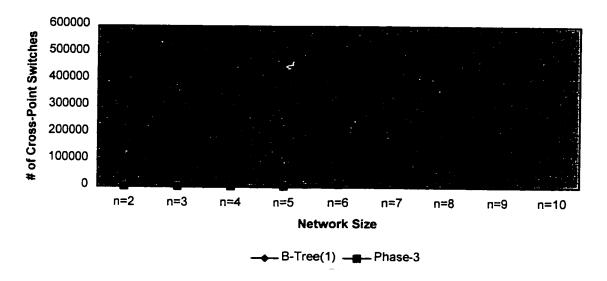

| Figure 3.16 | Cross-point switches complexity of phase-3 and B-Tree (1) networks  | 13   |

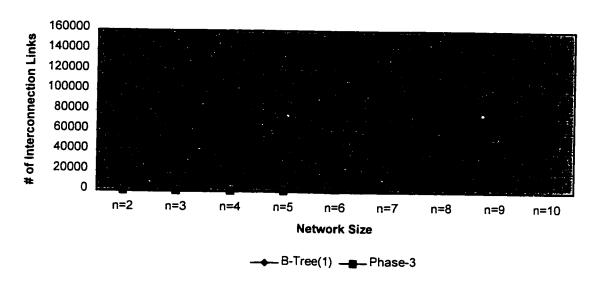

| Figure 3.17 | Interconnection links complexity of phase-3 and B-Tree (1) networks | 13   |

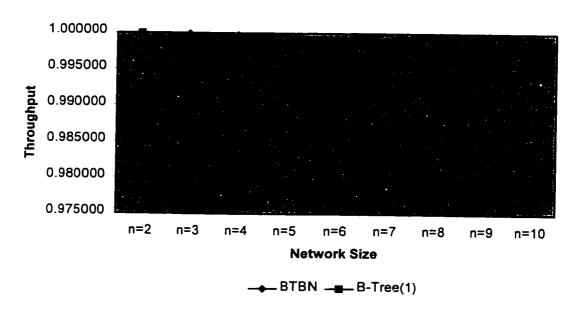

| Figure 3.18 | Throughput performance of BTBN and B-Tree (1) networks              | 14   |

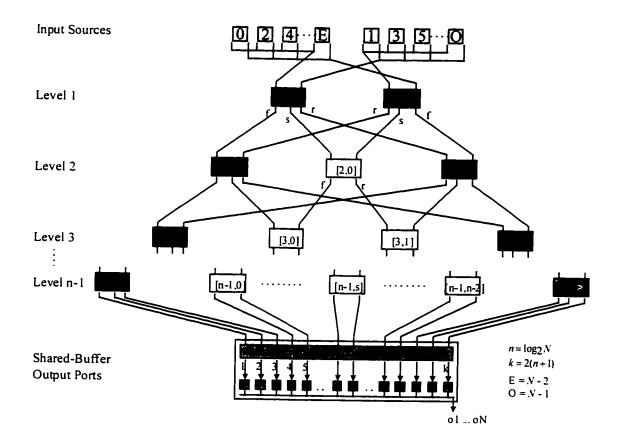

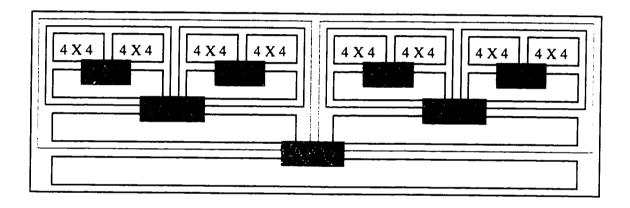

| Figure 3.19 | N X N BTBN                                                          | 14   |

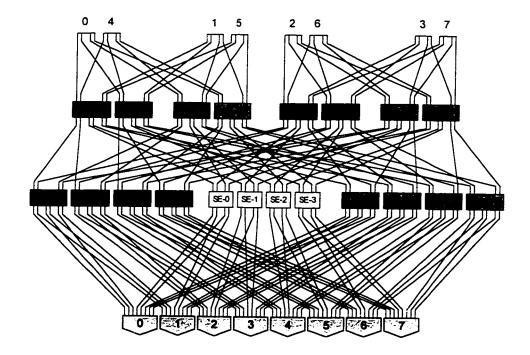

| Figure 3.20 | BTBN switching elements                                             | 14   |

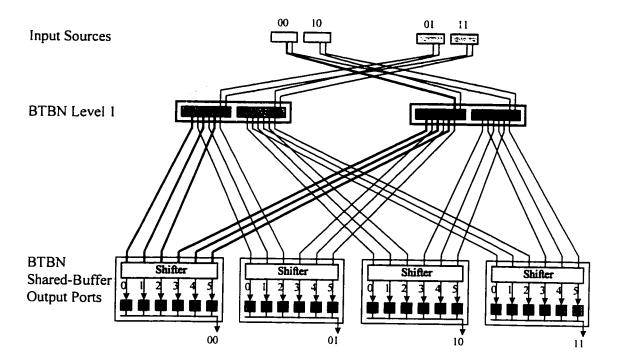

| Figure 3.21 | 4 X 4 BTBN                                                          | 14   |

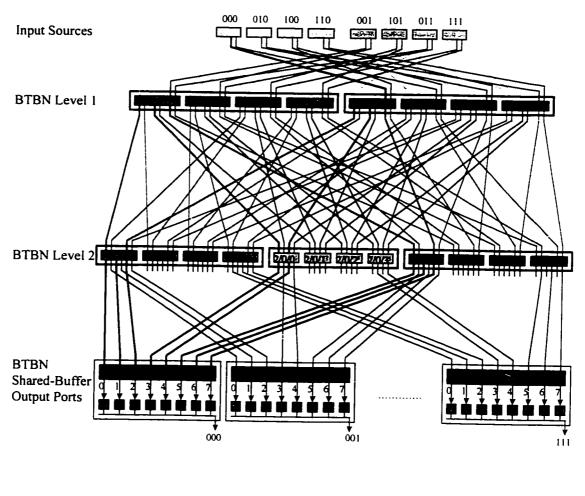

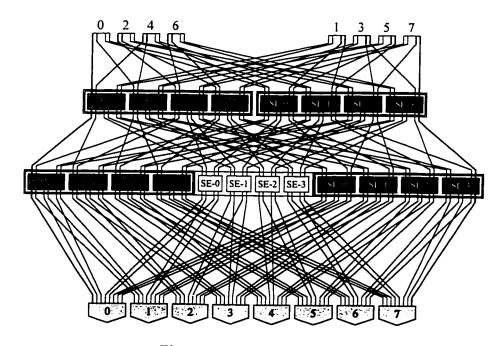

| Figure 3.22 | 8 X 8 BTBN                                                          | 14   |

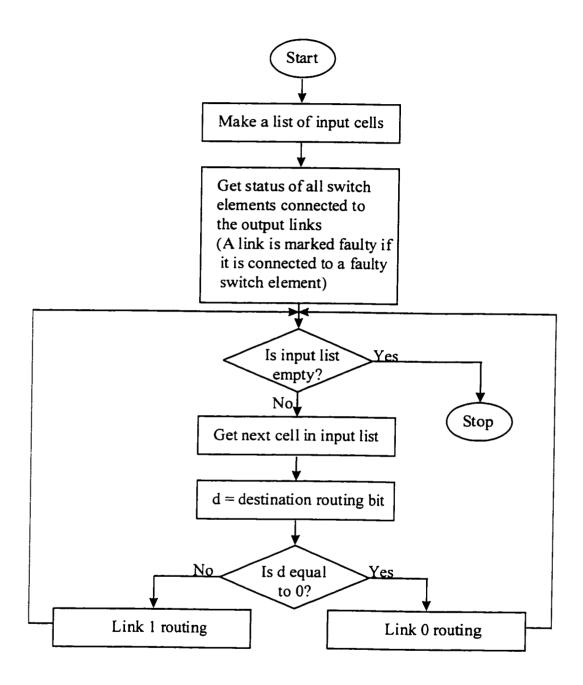

| Figure 3.23 | BTBN routing algorithm                                              | 14   |

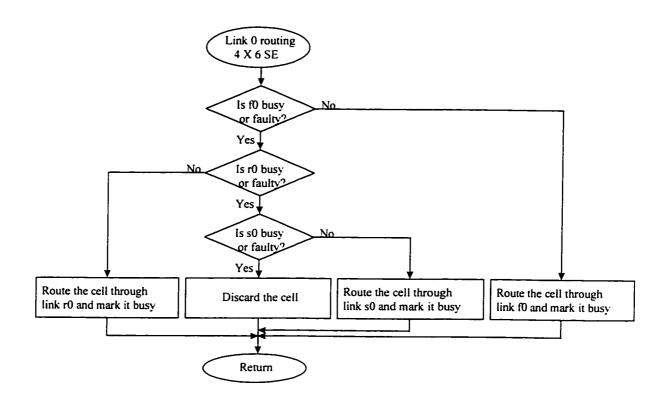

| Figure 3.24 | Output link 0 routing algorithm for 4 X 6 switching element         | 14   |

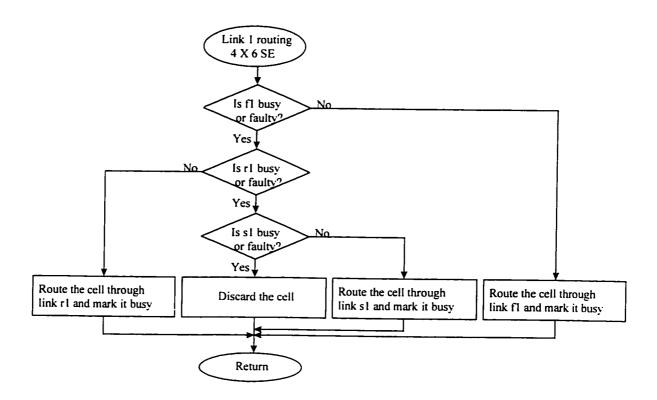

| Figure 3.25 | Output link 1 routing algorithm for 4 X 6 switching element         | 15   |

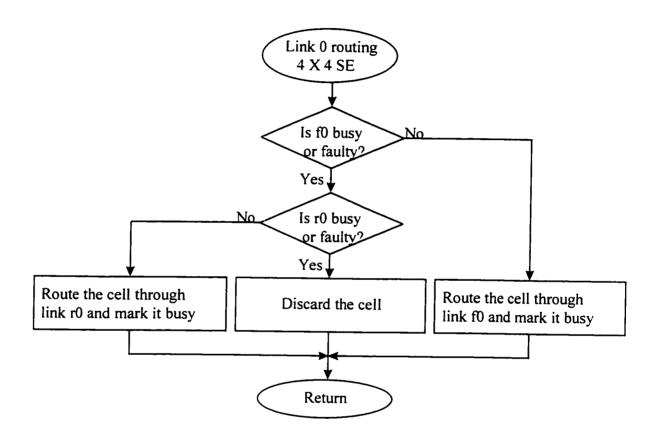

| Figure 3.26 | Output link 0 routing algorithm for 4 X 4 switching element         |      |

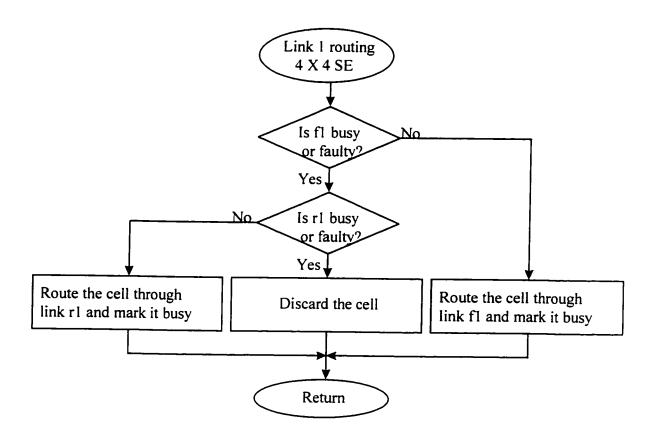

| Figure 3.27 | Output link 1 routing algorithm for 4 X 4 switching element         | 15   |

| Figure 3.28 | Cross-point switches complexity of BTBN, B-Tree (1), Tagle          | 15   |

| Ç           | and Sharma's, and parallel banyan networks                          | 15   |

| Figure 3.29 | Interconnection links complexity of BTBN, B-Tree (1), Tagle         | 15   |

| 8           | and Sharma's, and parallel banyan networks                          | 150  |

| Figure 3.30 | Switching network complexity of BTBN, B-Tree (1), Tagle and         | 15   |

| J           | Sharma's, and parallel banyan networks                              | 150  |

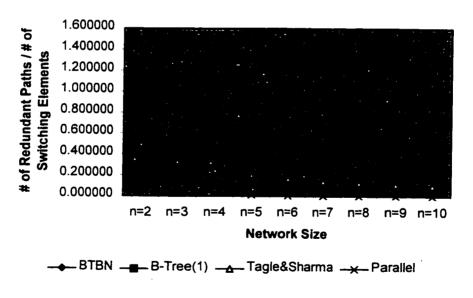

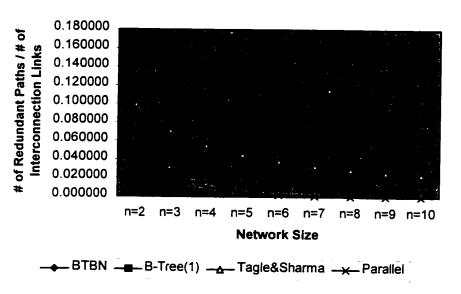

| Figure 3.31 | Redundant paths of BTBN, B-Tree (1), Tagle and Sharma's,            | 159  |

|             | and parallel banyan networks                                        | 1.00 |

| Figure 3.32 | Switching element contribution of BTBN, B-Tree (1), Tagle           | 160  |

| <b>0</b>    | and Sharma's, and parallel banyan networks                          | 16   |

| Figure 3.33 | Interconnection link contribution of BTBN, B-Tree (1), Tagle        | 162  |

| Ü           | and Sharma's, and parallel banyan networks                          | 163  |

| Figure 3.34 | Illustration of BTBN modularity and expandability                   | 163  |

| Figure 3.35 | Building 8 X 8 BTBN using two 4 X 4 BTBN networks                   | 164  |

| Figure 3.36 | 8 X 8 BTBN                                                          | 166  |

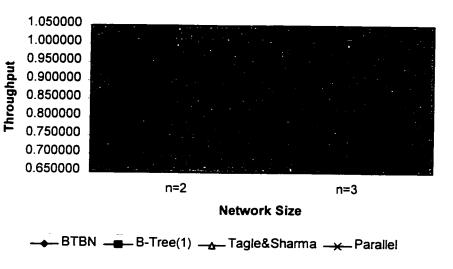

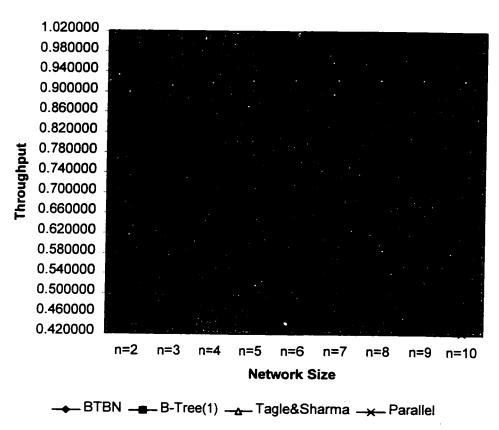

| Figure 4.1  | Throughput performance under permutation input traffic for          | 166  |

| C           | BTBN, B-Tree (1), Tagle and Sharma's, and parallel banyan           |      |

|             | networks                                                            | 1.00 |

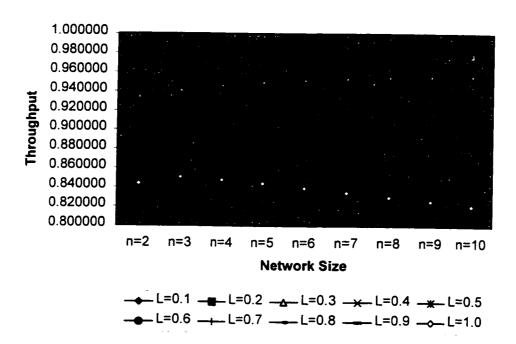

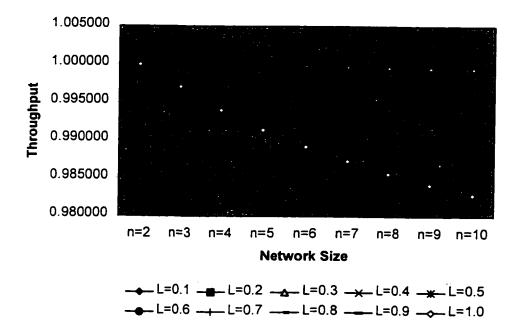

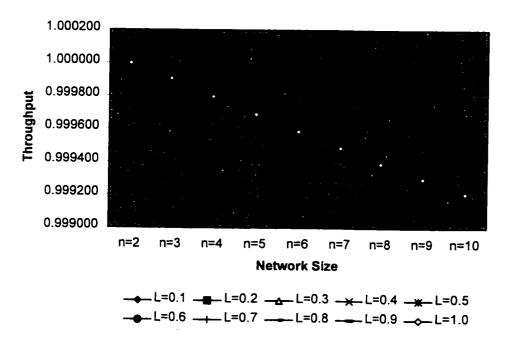

| Figure 4.2  | Analytical throughput performance under various loads of            | 169  |

| 5           | uniform input traffic for parallel banyan network                   | 170  |

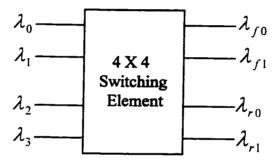

| Figure 4.3  | Load labeling for a 4 X 4 switching element                         | 172  |

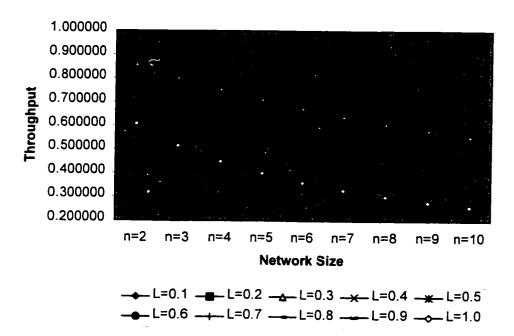

| Figure 4.4  | Analytical throughput performance under various loads of            | 173  |

| <b>G</b>    | uniform imput traffic for T. 1 101                                  | 17/  |

|             |                                                                     | 176  |

| Figure 4.5  | Analytical throughput performance under various loads of uniform input traffic for B-Tree (1) network                                                        | 177 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

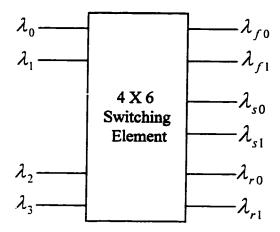

| Figure 4.6  | Load labeling for a 4 X 6 switching element                                                                                                                  | 179 |

| Figure 4.7  | Analytical throughput performance under various loads of uniform input traffic for BTBN network                                                              |     |

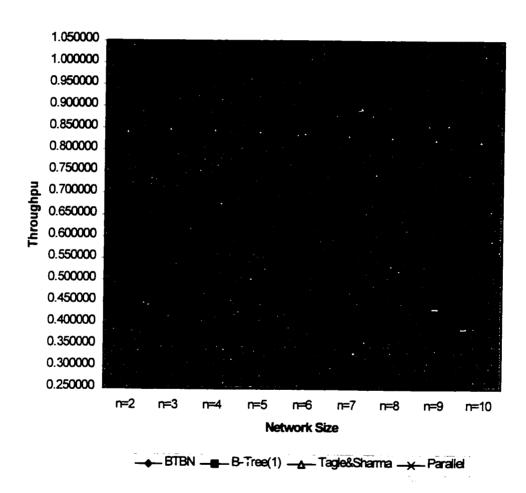

| Figure 4.8  | Analytical throughput performance under 50% load of uniform input traffic                                                                                    | 182 |

| Figure 4.9  | Analytical throughput performance under 100% load of uniform input traffic                                                                                   | 183 |

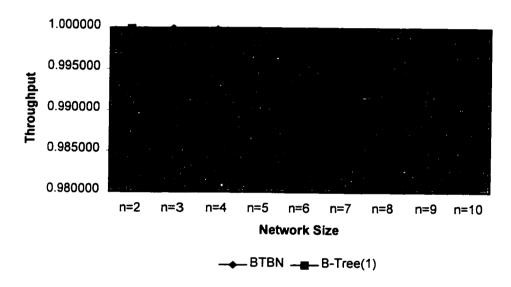

| Figure 4.10 | Analytical throughput performance under 100% load of uniform input traffic for BTBN and B-Tree (1) networks                                                  | 185 |

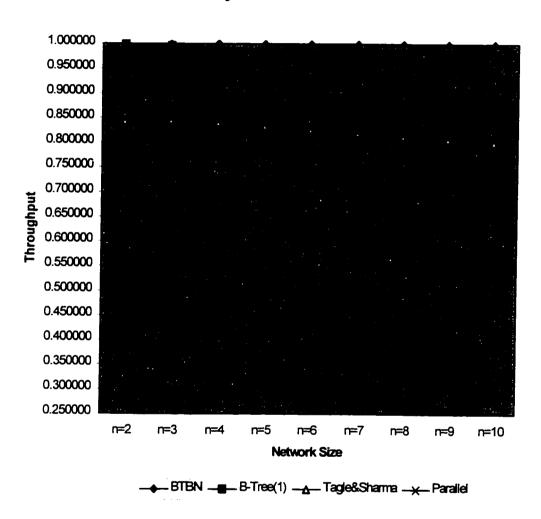

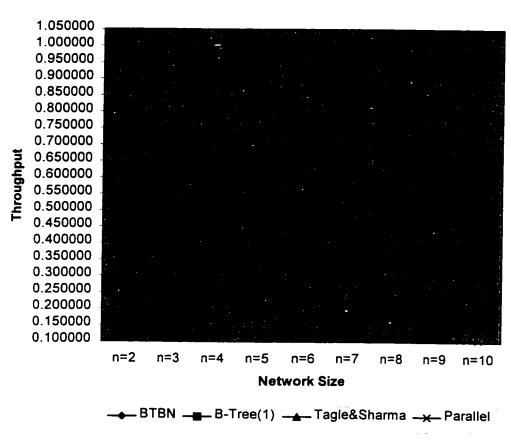

| Figure 4.11 | Throughput performance under 100% load of uniform input traffic (Simulation)                                                                                 | 187 |

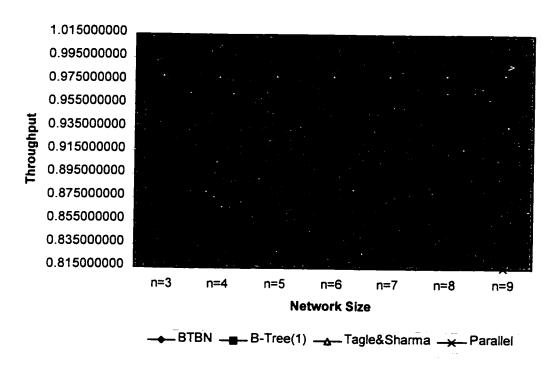

| Figure 4.12 | Throughput performance under 100% load of uniform input traffic for BTBN and B-Tree (1) networks. (Analytical vs. Simulation)                                | 188 |

| Figure 4.13 | Throughput performance under 100% load of uniform input traffic for parallel banyan and Tagle and Sharma's networks. (Analytical vs. Simulation)             | 189 |

| Figure 4.14 | Simulation throughput performance under various percentages of hot spot input traffic for BTBN network                                                       | 192 |

| Figure 4.15 | Simulation throughput performance under various percentages of hot spot input traffic for B-Tree (1) network                                                 | 193 |

| Figure 4.16 | Simulation throughput performance under various percentages of hot spot input traffic for Tagle and Sharma's network                                         | 194 |

| Figure 4.17 | Simulation throughput performance under various percentages of hot spot input traffic for parallel banyan network                                            | 195 |

| Figure 4.18 | Throughput performance under 25% hot spot input traffic. (Simulation)                                                                                        | 196 |

| Figure 4.19 | Throughput performance under 50% hot spot input traffic. (Simulation)                                                                                        | 198 |

| Figure 4.20 | Throughput performance under 75% hot spot input traffic. (Simulation)                                                                                        | 199 |

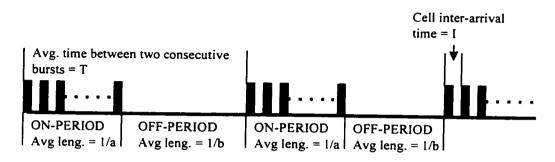

| Figure 4.21 | ON/OFF source model                                                                                                                                          | 202 |

| Figure 4.22 | Simulation throughput performance under ATM input traffic (10% Voice, 20% Connectionless data, 30% Connection                                                |     |

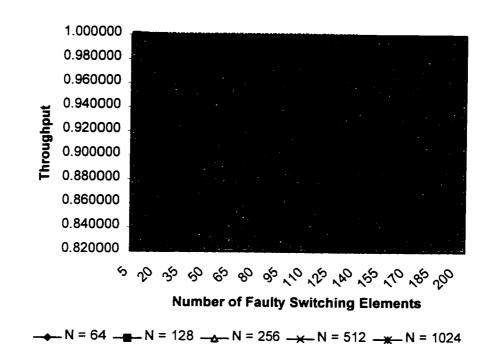

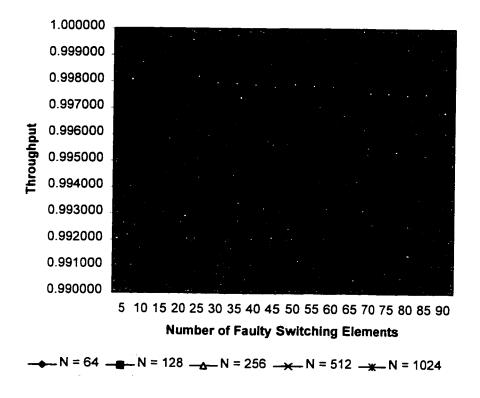

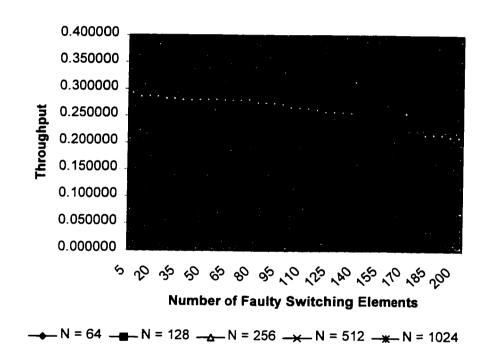

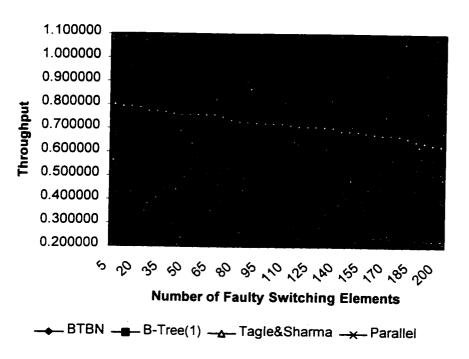

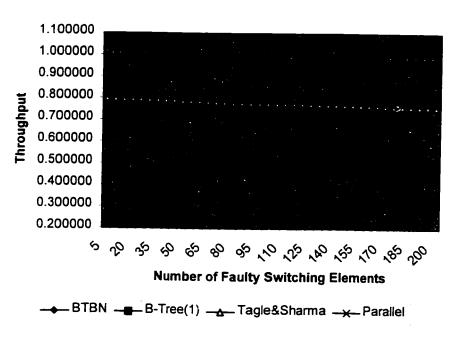

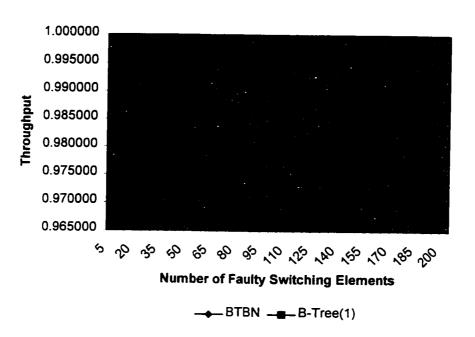

| Figure 5.1  | oriented data, and 40% VBR video/data) Throughput performance under uniform input traffic and up to 200 randomly selected faulty switching elements for BTBN | 206 |

|             | networks                                                                                                                                                     | 210 |

| Figure 5.2  | Throughput performance under uniform input traffic and up to 90 randomly selected faulty switching elements for BTBN networks                               |     |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

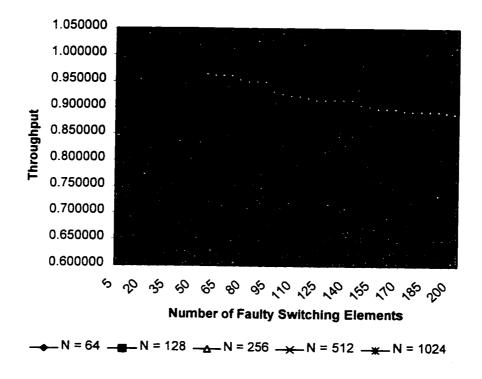

| Figure 5.3  | Throughput performance under uniform input traffic and up to 200 randomly selected faulty switching elements for B-Tree (1) networks                        |     |

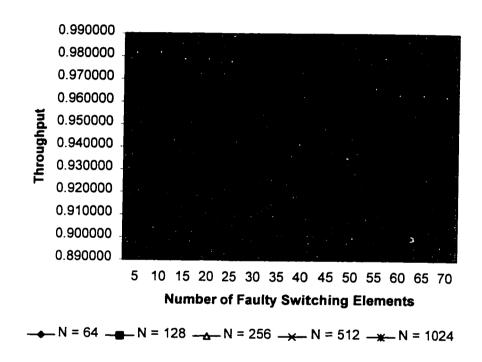

| Figure 5.4  | Throughput performance under uniform input traffic and up to 70 randomly selected faulty switching elements for B-Tree (1)                                  |     |

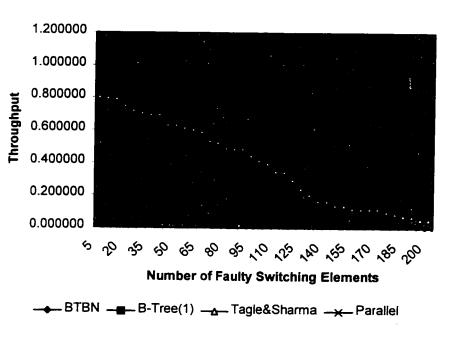

| Figure 5.5  | Throughput performance under uniform input traffic and up to 200 randomly selected faulty switching elements for Tagle and                                  | 214 |

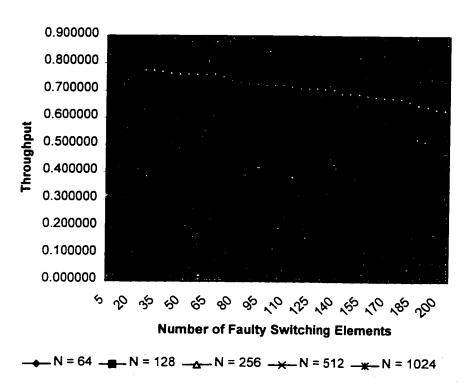

| Figure 5.6  | Sharma's networks Throughput performance under uniform input traffic and up to 200 randomly selected faulty switching elements for parallel banyan networks | 215 |

| Figure 5.7  | Throughput performance under uniform input traffic and up to 200 randomly selected faulty switching elements for 64 X 64 networks                           | 216 |

| Figure 5.8  | Throughput performance under uniform input traffic and up to 200 randomly selected faulty switching elements for 128 X 128 networks                         | 217 |

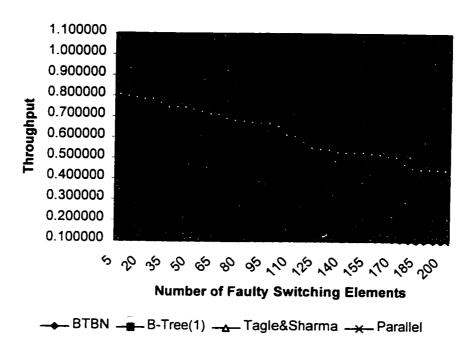

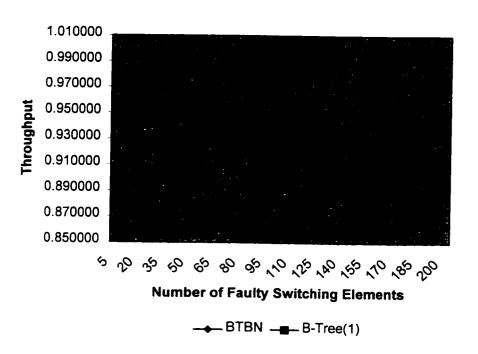

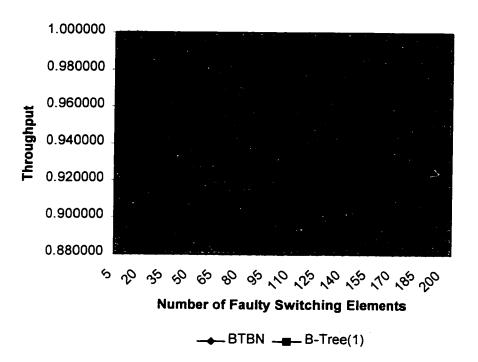

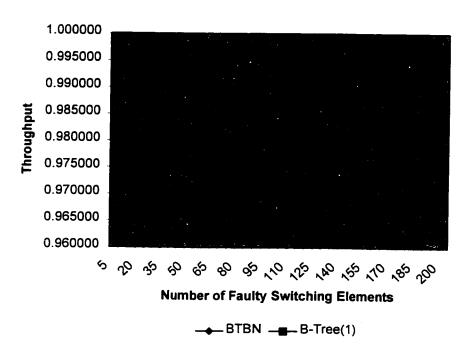

| Figure 5.9  | Throughput performance under uniform input traffic and up to 200 randomly selected faulty switching elements for 128 X 128 BTBN and B-Tree (1) networks     | 219 |

| Figure 5.10 | Throughput performance under uniform input traffic and up to 200 randomly selected faulty switching elements for 256 X 256 networks                         | 220 |

| Figure 5.11 | Throughput performance under uniform input traffic and up to 200 randomly selected faulty switching elements for 256 X 256 BTBN and B-Tree (1) networks     | 221 |

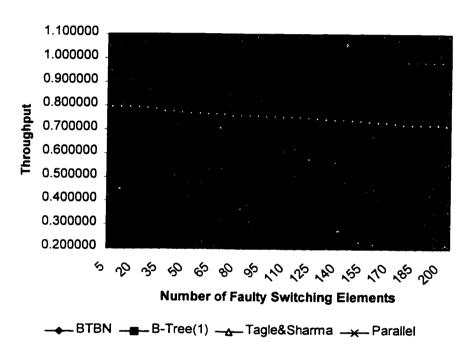

| Figure 5.12 | Throughput performance under uniform input traffic and up to 200 randomly selected faulty switching elements for 512 X 512 networks                         | 223 |

| Figure 5.13 | Throughput performance under uniform input traffic and up to 200 randomly selected faulty switching elements for 512 X 512 BTBN and B-Tree (1) networks     | 224 |

| Figure 5.14 | Throughput performance under uniform input traffic and up to 200 randomly selected faulty switching elements for 1024 X 1024 networks                       | 225 |

| Figure 5.15 | Throughput performance under uniform input traffic and up to                                                                                                | 226 |

| 4 X      |

|----------|

| 227      |

| and      |

| 229      |

| and      |

| 230      |

| and      |

| orks 231 |

| and      |

| s 232    |

| spot     |

| ing      |

| 234      |

| pot      |

| yan      |

| - 235    |

| ffic     |

| 236      |

| and      |

| 237      |

| and      |

| 238      |

| 241      |

| 243      |

|          |

| 243      |

| 245      |

| 248      |

| 249      |

|          |

# List of Tables

| Table 3.1   | SEN throughput performance comparison                           | 12   |

|-------------|-----------------------------------------------------------------|------|

| Table 3.2   | Throughput performance of phase-1 and parallel banyan           |      |

|             | networks                                                        | 12   |

| Table 3.3   | Cross-point switches complexity of phase-1 and parallel banyan  |      |

|             | networks                                                        | 12   |

| Table 3.4   | Interconnection links complexity of phase-1 and parallel banyan |      |

|             | networks                                                        | 12   |

| Table 3.5   | Throughput performance of phase-2 and Tagle & Sharma's          |      |

|             | networks                                                        | 13   |

| Table 3.6   | Cross-point switches complexity of phase-2 and Tagle &          |      |

|             | Sharma's networks                                               | 13   |

| Table 3.7   | Interconnection links complexity of phase-2 and Tagle and       |      |

|             | Sharma's networks                                               | 13   |

| Table 3.8   | Throughput performance of phase-3 and B-Tree (1) networks       | 13   |

| Table 3.9   | Cross-point switches complexity of phase-3 and B-Tree (1)       |      |

| <b></b>     | networks                                                        | 13   |

| Table 3.10  | Interconnection links complexity of phase-3 and B-Tree (1)      |      |

| ~ 11        | networks                                                        | 13   |

| Table 3.11  | Throughput performance of BTBN and B-Tree (1) networks          | 140  |

| Table 3.12  | 8 X 8 BTBN routes from input port 0 to output port 0            | 15:  |

| Table 3.13  | Cross-point switches complexity of BTBN, B-Tree (1), Tagle      |      |

|             | and Sharma's, and parallel banyan networks                      | 156  |

| Γable 3.14  | Interconnection links comploying of DTDNI D.T. (1) T.           |      |

| able 3.14   | Interconnection links complexity of BTBN, B-Tree (1), Tagle     |      |

|             | and Sharma's, and parallel banyan networks                      | 15   |

| Γable 3.15  | Switching network complexity of BTBN, B-Tree (1), Tagle and     |      |

| . 4510 5.15 | Chaman 1 1 11 11                                                | 1.51 |

|             | -                                                               | 159  |

| Table 3.16  | Redundant paths of BTBN, B-Tree (1), Tagle and Sharma's,        |      |

|             | standard padds of Dibit, D-free (1), Tagle and Snarma's,        |      |

|             | and parallel banyan networks                                                                                   | 160 |

|-------------|----------------------------------------------------------------------------------------------------------------|-----|

| Table 3.17  | Switching element contribution of BTBN, B-Tree (1), Tagle                                                      |     |

|             | and Sharma's, and parallel banyan networks                                                                     | 162 |

| Table 3.18  | Interconnection link contribution of BTBN, B-Tree (1), Tagle                                                   |     |

|             | and Sharma's, and parallel banyan networks                                                                     | 163 |

| Table 4.1   | Throughput performance under permutation input traffic for                                                     |     |

|             | BTBN, B-Tree (1), Tagle and Sharma's, and parallel banyan                                                      |     |

|             | networks                                                                                                       | 169 |

| Table 4.2   | Analytical throughput performance under various loads of                                                       |     |

|             | uniform input traffic for parallel banyan network                                                              | 172 |

| Table 4.3   | Analytical throughput performance under various loads of                                                       |     |

|             | uniform input traffic for Tagle and Sharma's network                                                           | 176 |

| Table 4.4   | Analytical throughput performance under various loads of                                                       |     |

|             | uniform input traffic for B-Tree (1) network                                                                   | 177 |

| Table 4.5   | Analytical throughput performance under various loads of                                                       |     |

|             | uniform input traffic for BTBN network                                                                         | 181 |

| Table 4.6   | Throughput performance under 100% load of uniform input                                                        |     |

|             | traffic for BTBN and B-Tree (1) networks. (Analytical vs.                                                      |     |

|             | Simulation)                                                                                                    | 188 |

| Table 4.7   | Throughput performance under 100% load of uniform input                                                        |     |

|             | traffic for parallel banyan and Tagle and Sharma's networks.                                                   |     |

| <b></b>     | (Analytical vs. Simulation)                                                                                    | 189 |

| Table 4.8   | Simulation throughput performance under various percentages                                                    |     |

| T 11 40     | of hot spot input traffic for BTBN network                                                                     | 192 |

| Table 4.9   | Simulation throughput performance under various percentages                                                    |     |

| T 11 4 10   | of hot spot input traffic for B-Tree (1) network                                                               | 193 |

| Table 4.10  | Simulation throughput performance under various percentages                                                    |     |

| T-1.1 4 1 1 | of hot spot input traffic for Tagle and Sharma's network                                                       | 194 |

| Table 4.11  | Simulation throughput performance under various percentages                                                    |     |

| T-bl- 4 10  | of hot spot input traffic for parallel banyan network                                                          | 195 |

| Table 4.12  | ITU-T recommended traffic parameters for various ATM input                                                     |     |

| Table 4.13  | source models                                                                                                  | 202 |

| 14016 4.13  | Simulation throughput performance under ATM input traffic                                                      |     |

|             | (10% Voice, 20% Connectionless data, 30% Connection                                                            |     |

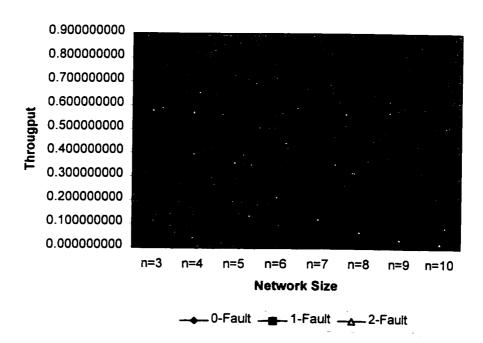

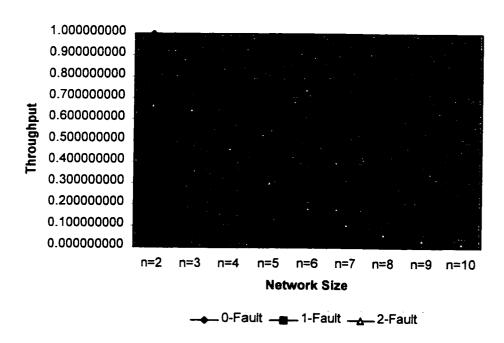

| Table 5.1   | oriented data, and 40% VBR video/data)                                                                         | 206 |

| radic J. I  | Throughput performance under 100% hot spot input traffic and                                                   |     |

| Γable 5.2   | single / double faults simulation for BTBN networks                                                            | 229 |

| . wore J. 4 | Throughput performance under 100% hot spot input traffic and single / double faults simulation for D. Tare (1) | 226 |

| Γable 5.3   |                                                                                                                | 230 |

| 1 4010 3.3  | Throughput performance under 100% hot spot input traffic and                                                   |     |

| single / double faults simulation for Tagle and Sham's networks | 231                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Throughput performance under 100% hot spot input traffic and    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| single / double faults simulation for parallel banyan networks  | 232                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Throughput performance under 100% hot spot input traffic        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| simulation for switching fabric's networks                      | 236                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Throughput performance under 100% hot spot input traffic and    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| single fault simulation for switching fabric's networks         | 237                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Throughput performance under 100% hot spot input traffic and    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| double fault simulation for switching fabric's networks         | 238                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

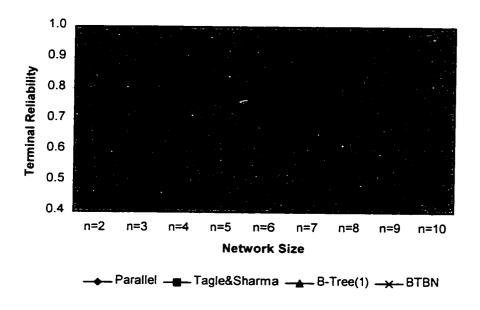

| Terminal reliability of switching fabrics using first method    | 248                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

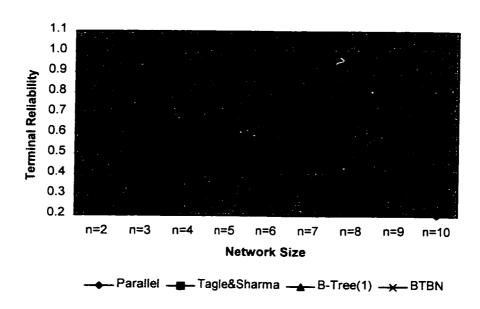

| Terminal reliability of switching fabrics using second method   | 249                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                 | Throughput performance under 100% hot spot input traffic and single / double faults simulation for parallel banyan networks Throughput performance under 100% hot spot input traffic simulation for switching fabric's networks Throughput performance under 100% hot spot input traffic and single fault simulation for switching fabric's networks Throughput performance under 100% hot spot input traffic and double fault simulation for switching fabric's networks Terminal reliability of switching fabrics using first method |

### **Abstract**

Name:

Ghaleb A. Al-Hashim

Title:

Design and Analysis of a High-Performance Fault-

Tolerant ATM Network

Major Field:

Computer Engineering

Date of Degree:

May 1998

A high-performance fault tolerant Asynchronous Transfer Mode (ATM) switching fabric architecture called Binary-Tree Banyan Network (BTBN) is proposed. It is based on two interconnected parallel banyan networks in a binary tree form. Many ATM switching fabric architectures are proposed in the literature; however, few of them consider both the throughput performance measure and fault tolerance feature in the design. Compared to known and recent switching fabric architectures, BTBN has demonstrated very low cell loss probability and high throughput under normal operation and in the presence of faulty switching element conditions. In addition, any multistage interconnection networks (MIN) such as OMEGA, Delta, Baseline, and any topologically equivalent networks can be used in the BTBN switching fabric. BTBN requires less transmission latency than the simple baseline network, delivers all input cells in the right sequence using simple and distributed self-routing algorithm, and does not have jitter or Head-Of-Line (HOL) problems. In addition, BTBN is modular, scalable, and can be recursively expanded easily.

Master of Science Degree

King Fahd University of Petroleum & Minerals

Dhahran, Saudi Arabia

May 1998

### خلاصة الرسألة

الاســـه: غالب عبدالرضى على الحاشم

عنوان الرسالة: تصميم وتحليل شبكة (ATM) ذات الأداء العالي و انحتملة للخلل

التخصص: هندسة الحاسب الآني

تاريخ التخرج: مايو ١٩٩٨

في هذه الوسالة. نقدم تصييم شبكة (ATM) الجديدة ذات الأداء العاني و انحتملة للخلل المسماة بـ (BTBN). يعتمد تصييم هذه الشبكة على ربط شبكتين متوازيتيز من فيع (Banyan) على شكل شجرة ثنائية. نقد قدمت بحوث كثيرة في تصييم شبكات (ATM) ولكن قليل منها يأخذ بالاعتبار الظروف الغير طبيعية عندما يحدث خلل في مكونات الشبكة. أما شبكة (BTBN) فقد أثبتت كفاءتها العالمية في الظروف العادية وكذلك في حالة وجود خلل في كثير من مكونات الشبكة و ذلك بالمقارنة بعدد من الشبكات المشهورة و منقترحة حديث. اضافة الى ذلك. فانها قابلة للتصعيم باعتماد اي نوع من أنواع الشبكات المترابطة و الموحلية المعروفة بسنقترحة حديث الصافة الى ذلك. فانها قابلة للتصعيم باعتماد اي نوع من أنواع الشبكات المترابطة و الموحلية المعروفة بالذكر أن شبكة (Delta) و (Delta) و (Baseline). والجدير بالذكر أن شبكة (BTBN) خالية من العيوب التي تشتكي منها كثير من الشبكات المقترحة حيث أنها شبكة ذات اعتمادية عالمية و تحتمل الكثير من الخلل المحلوب ارسالها في ترتيبها الصحيح من خلال لكثير من الخلل المحديد من خدال الشبكة مستخدمة برنامج التسيير المبسط و الموزع على جميع مكوناتها . اضافة الى ذلك. امكانية توسيع الشبكة سهونة و مانتظامية في التصيم.

درجة الماجستير في العلوم جامعة الملك فهد للبترول و المعادن الظهران – المملكة العربية السعودية مايو ١٩٩٨

# Chapter 1

### **INTRODUCTION**

Broadband-Integrated Services Digital Network (B-ISDN) is a cost-effective and service-independent network capable of transporting all different communication services and sharing all its available resources among all services. International Telecommunications Union - Telecommunication Standardization Sector (ITU-T) accepted ATM as the ultimate transfer mode solution for B-ISDN. ATM is a connection-oriented packet switching and multiplexing technique to transfer information over B-ISDN where established end-to-end paths are required prior to the beginning of information transfer. ATM has various features that extend the capabilities of current packet-switching networks toward incorporating the most desired features of circuit-switching networks to support real-time and variable bit-rate traffic most efficiently [38,40,64,65].

Several ATM switching fabric architectures have been proposed in the literature. There are two classes of ATM switching fabrics: time-division and space-division. Time-division architectures are further classified as shared-memory and shared-medium. Space-division architectures are classified based on their structures as crossbar, banyan-based and  $N^2$  disjoint paths [12,52,53].

In time-division architectures, the traffic from all N input lines is multiplexed into a single resource of bandwidth equal to N times the bandwidth of a single line. This resource is shared by all input and output ports and can be a common memory or a shared medium such as a bus or a ring. *Coprin* is a shared-memory ATM switching fabric developed by the French CNET. ATM Output buffer Modular (ATOM) is a shared-medium ATM switching fabric developed by NEC. The switching fabric scalability of such architectures is restricted by the limitation on the bandwidth of the shared resource and on the number of input/output ports. Usually, the buffer management and control functions are centralized which increases the switch complexity [12,40,53].

In space-division architectures, multiple concurrent paths are established from the input to the output lines. Each path has the same data rate capacity as an individual line. In addition, the control of the switch can be either centralized or distributed throughout the switching fabric, thereby reducing its design complexity [12,40,52,53].

Although the design of the space-division switching fabric solves the scalability problem of the time-division architectures, some of the space-division switching fabrics have an inherent problem called internal blocking. This problem occurs when multiple disjoint paths can not be established simultaneously to route input cells to the proper destinations. The internal blocking problem limits the throughput of the switching fabric. Many switching fabric designs are proposed to minimize the effect of the internal blocking problem. For example, the crossbar switching fabric is considered as a nonblocking switching fabric [12,40,52,53].

Although, the crossbar switching fabric can successfully switch any destination permutation patterns at the input of the switching fabric to the proper output destinations, it can not switch more than one input cell destined to the same output port simultaneously. This problem is called output contention. This problem severely affects the performance of the switching fabric when the destination patterns traffic is modeled as a hot-spot input traffic where most of the input cells are destined to a specific output port that is highly on demand such as a file server. Another disadvantage of the crossbar switching fabric is the exponential increase in its size (the required number of cross-point switches) with the number of input lines. Hence, it is not recommended for large-size networks [12,29,53].

To solve the internal blocking and output contention problems in space-division switching fabrics, an  $N^2$  disjoint paths switch architecture called the Knockout

switching fabric has been proposed. This is the most efficient, yet very expensive. NXN switching fabric where it is possible to establish  $N^2$  disjoint paths from the input to the output lines simultaneously [82,84].

Banyan-based switch architectures are more practical than the crossbar switching fabric for large size networks. At the same time, they are not as expensive as the Knockout switching fabrics. They are based on MIN. The simplest banyan-based switching fabric is the Baseline Banyan Network. There is at most one path connecting any input to any output lines. This network has two problems: internal blocking and output contention [40].

A buffered-banyan network based on a banyan network with buffers in each switching element is effective for uniform traffic since it minimizes the blocking problem in the Baseline Banyan Network. It, however, introduces other problems for nonuniform traffic such as Head-Of-Line (HOL) blocking, large buffers requirement, and random delays within the switching fabric causing high jitter. HOL happens when one cell is waiting its turn for access to an output port and the other cells behind it are blocked and forced to wait despite the fact that their output ports are possibly idle [52,53].

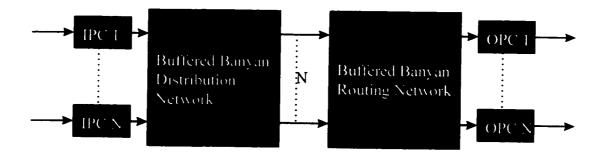

To minimize HOL blocking, Double Banyan Network (DBN) is proposed. The network is based on cascading two buffered banyan networks: a distribution network

followed by a routing network. While the DBN minimizes HOL blocking, it increases the random delays within the switching fabric causing high jitter problem [52].

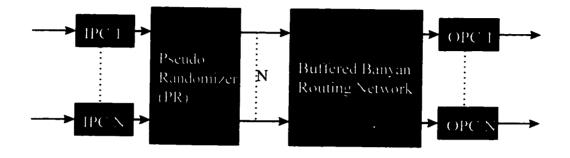

Another solution for HOL blocking is proposed for nonuniform traffic input. The switching fabric is called Pseudo Randomizer-Banyan Network. This network is based on a cell-scattering hardware, called pseudo randomizer; to distribute the nonuniform input traffic uniformly over the entire buffered banyan network by generating random patterns. It has been analyzed under nonuniform traffic and was found to have almost the same performance as that of a banyan network under uniform traffic [83].

Bypass Queues-Banyan Network is proposed to minimize the internal and HOL blocking problems by allowing other cells in the input buffers, called bypass queues. to be transmitted when the leading cell is blocked. It was shown that 90% throughput can be achieved for large-size switching fabric by using four banyan planes in parallel with bypass queues [80].

To minimize internal blocking without introducing the high jitter problem. Batcher-Banyan Network has been proposed [37]. The switch architecture consists of two consecutive networks: batch sorting and banyan networks. Cells are first fed to a batch sorter in which they are sorted according to their destination address, and then routed by a banyan self-routing network. Improved versions of Batcher-Banyan based switch architectures such as the *starlite* and *sunshine* switches are proposed to minimize the output contention problem [12,52,25].

Rerouting-Banyan Network was proposed to minimize cell contention efficiently. It achieves high throughput and low cell loss probability even with hot-spot traffic [62].

In general, a network is called i-fault tolerant if any set of i faults can be tolerated. A robust network can tolerate some instances of i faults. To improve the switching fabric reliability and fault tolerance, most of the banyan-based networks use one or more of the following strategies. The strategies are: switch size and internal links expansion, switching fabric duplication, additional switching elements in each stage, additional input/output ports, use of buffers in each switching element, and enhancement of the internal links speed relative to the input/output ports.

Extra-Stage Shuffle-Exchange Network uses extra stage to the basic Shuffle-Exchange Network to improve its fault tolerance. This is achieved by providing two paths for each input-output pair. The main problem with this network is that the two paths of each input-output pair are not disjoint [71].

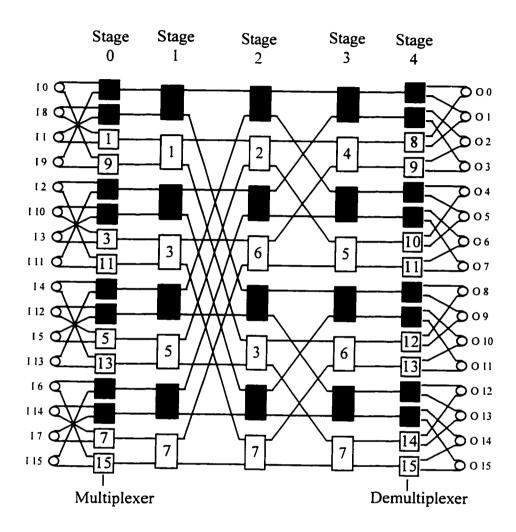

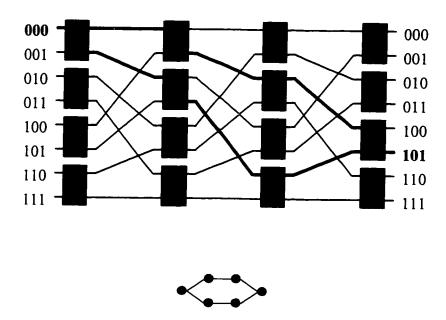

MD-Omega Network is a single fault tolerant switch architecture that is based on a banyan network. It provides two disjoint paths throughout all network stages by using multiplexers at the input stage and demultiplexers replacing the last stage [76]. Extra Stage Cube Network is also proposed to provide two disjoint paths throughout all network stages [16]. The Benes Network minimizes the internal blocking problem and improves the fault tolerance of the switching element [7]. It consists of two baseline networks mirrored to each other sharing the middle stage. However, the

internal blocking problem and the fault tolerance are not improved throughout all stages of the switch architecture. The transmission latency is doubled and the routing complexity is increased.

Itoh Network increases the number of paths from any input to any output pair. It consists of a modified version of the baseline network with added subswitches between stages. The internal blocking problem is minimized and the switching element fault tolerance is improved at the expense of loosing the cells sequence and increasing transmission latency. In addition, the switch architecture is not modular and does not have a regular structure [3].

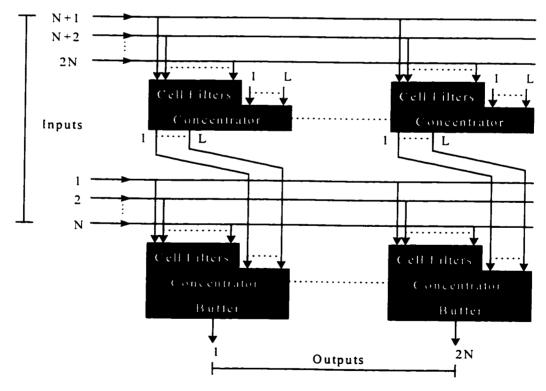

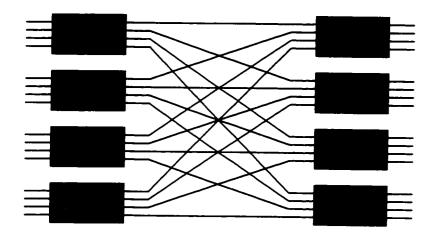

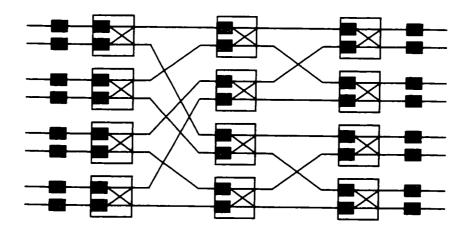

The parallel-banyan network provides two disjoint paths without increasing the transmission latency and loosing the cell sequence. It consists of two parallel baseline networks (planes) connected using input and output routers. Internal blocking and output contention problems are not minimized within each plane [52]. Tagle and Sharma Network minimizes the internal blocking and improves fault tolerance of each plane of the parallel-banyan network. This architecture allows routing from one plane to the other plane if there is cells contention or switching element faults [49].

Tandem-Banyan Network (TBN) has been proposed in order to minimize the internal blocking and output contention problems. It consists of multiple cascaded banyan networks. Unfortunately, the TBN achieves this at the expense of an increase in transmission latency and the out-of-order cell delivery [13,58].

Baseline-Tree Network minimizes internal blocking and output contention problems. In addition, it improves the fault tolerance of the switching elements. It is based on multiple interconnected banyan networks to provide multiple paths from any input to any output pair with minimum cell loss. The Baseline-Tree and Baseline Networks have the same transmission latency [28,27].

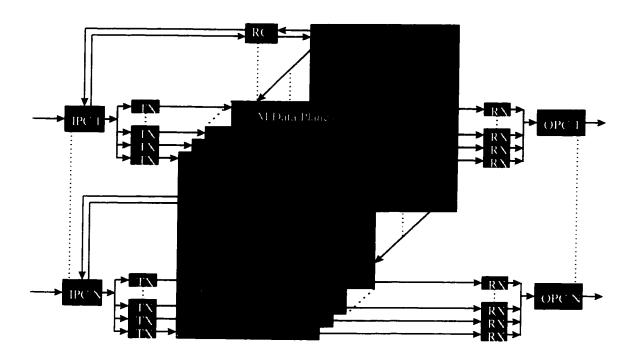

Pipeline-Banyan Network (PBN) is based on parallel banyan data planes controlled by a control plane. The control plane is for path reservation and the data planes are for cells routing. This switch architecture achieves a close to 100% maximum throughput, delay that is independent of the switch size, and in-sequence delivery of cells. Fault tolerance is not considered in the design of PBN [48].

Lin and Wang Banyan Network minimizes internal blocking and achieves fault tolerance by providing large number of paths between each input-output pair. This architecture provides two access points to the output ports to minimize the output contention problem. However, it does not preserve cells sequence in addition to introducing high jitter [26].

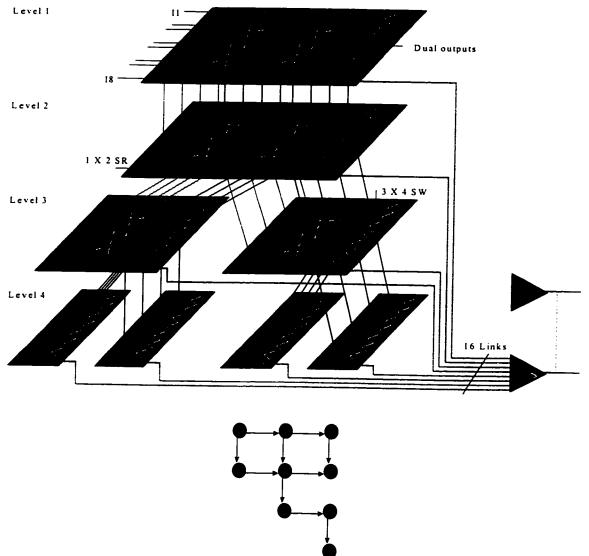

The Parallel-Tree Banyan Switching Fabric (PTBSF) minimizes internal blocking and output contention [77]. It is based on parallel banyan networks interconnected in a tree topology. This architecture consists of several levels. Cells sequence is not guaranteed when contended cells go through several levels in the tree.

Reliable And Zealous Network (RAZAN) minimizes internal blocking and output contention, and achieves fault tolerance by providing disjoint paths and large number

of redundant paths between each input-output pair. RAZAN and Baseline Networks have the same transmission latency. However, it is not scalable since the size of the switching element increase as the network size increases [71].

Most of the proposed switching fabrics attempt to minimize the internal blocking and output contention affects that are inherent problems in MIN. Those problems have a direct effect on the throughput performance. Other problems arise as a result of improving the throughput performance such as HOL problem, high jitter, out-of-order cell delivery, and complex buffer management. Some other solutions are proposed to minimize these arising problems by increasing the hardware complexity. Although this increase in hardware was not designed to cover switching element fault tolerance. some other switching fabrics attempt to improve throughput performance in the presence of faulty switching elements by increasing the hardware complexity. However, those fault tolerant switching fabrics are less concerned on the improvement of the throughput performance under normal conditions. Very few switching fabrics attempt to minimize internal blocking and output contention problems in order to achieve high throughput performance, and at the same time improve on the switching element fault tolerance. From the comprehensive literature survey, recommended criteria to design high performance and fault tolerant space-division MSI switching fabric architecture have evolved. The criteria are summarized in the following list:

- 1. Minimize cell loss during normal operation by

- minimizing the effect of internal blocking

- minimizing output port cell contention by increasing access links to

each output port of the switching fabric

- utilizing shared output buffer for each output port

- distributing the input load throughout the switching fabric

- 2. Maximize throughput performance for uniform and nonuniform input traffic during normal operation by

- allowing multiple access to each input port of the switching fabric

- increasing the internal speed of the switching fabric

- 3. Maximize throughput performance in the presence of faulty switching elements by

- increasing the number of disjoint input-output paths

- increasing the number of redundant input-output paths

- 4. Minimize the switching fabric transmission latency

- by reducing the number of stages required for cell routing

- 5. Deliver cells in sequence, eliminate random delays within the switching fabric (jitter), and maintain the switching fabric synchronization by

- making the input cells pass through the same number of switching

elements in order to reach the correct output port destinations

- keeping the self-routing switching algorithm simple

- minimizing the use of input and internal buffering

- avoiding cells missrouting and non progressive deflection

- 6. Make the switching fabric architecture modular, scalable, easily expandable, and consists of regular structures suitable for VLSI implementation

- 7. Increase the performance contribution of each switching element and each interconnection link in the switching fabric by

- increasing the number of redundant paths

- reducing the required number of interconnection links

- reducing the required number of switching elements

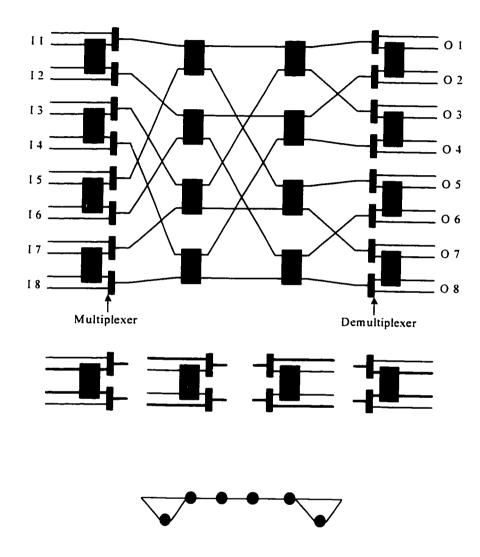

During the switching fabric design of most proposed architectures, more than one criterion from the above list is considered in the design. However, few of the proposed architectures consider both the throughput performance and the fault tolerance aspect in the switching fabric design. In this thesis, a new high-performance fault tolerant switch architecture is proposed. The proposed switch architecture is carefully designed to meet most of the criteria listed above. A detailed literature survey on ATM switching fabric architectures is described in Chapter 2. Chapter 3 describes the design evolution and the architecture of the proposed switching fabric. Chapter 4 presents the results of the performance evaluation of the proposed switch architecture under fault-free conditions. The results of the fault tolerance evaluation are presented in Chapter 5. The reliability analysis of the proposed switch architecture is described in Chapter 6. Finally, the concluding remarks and a projection for the future work activities are provided in Chapter 7.

### Chapter 2

# LITERATURE SURVEY ON ATM SWITCH ARCHITECTURES

### 2.1 Motivation

At present, telecommunication networks are characterized by service specialization. Each network is dedicated to a specific application or a class of services such as telephony, telex transmission, TV distribution, and computer data transmission. Each network is designed to provide its basic services very efficiently [10,12,40,53,54].

This service specialization causes a large number of worldwide independent networks to evolve. Each network requires its own design, implementation.

installation and maintenance. A given network resources can not be shared with other networks providing different services. This is cost inefficient. In addition, there is a strong desire to share data among different public and local area networks. As a result, many telecommunication networks have been connected via network interfaces called gateways and bridges that are required for translating the different network protocols. Those translator devices slowed the communication among different networks. This led to an anxious desire to integrate all telecommunication services based on different traffic characteristics and requirements in a unified fashion in a single large-scale network type. As a result, ITU-T adopted the first set of ISDN recommendations in 1984. ISDN extends the concept of the telephone network by incorporating additional functions and features of circuit-switching and packet switching networks to provide existing and new services in an integrated manner [40,53,54,56].

### 2.1.1 Integrated Services Digital Network (ISDN)

ISDN was a digital end-to-end telecommunications network supporting a wide range of voice and non-voice applications in the same network. The network was characterized by its access requirements and service characteristics and provides digital access to digital transmission services, packet data services, and network-provided data services. Many companies had looked at ISDN as a potential solution to tie their widely separated organizations together, reduce their cycle times, expand their

markets, and improve their ability to interact with their customers and satisfy them [40,52,53,54,56].

ISDN was based on 64-kbps switching technology and was intended to support voice facilities, existing data services, and low-speed video. It integrated most of the required telecommunication services except the transmission of moving highresolution images, digital TV, digital HDTV, video library, and high quality videophony. This is because these services require transmission channels capable of supporting transmission rates greater than the ISDN primary rate. Otherwise, the required transmission time would be unsatisfactory and very long when using the ISDN basic service rate. For instance, it would take over four hours to transmit a onegigabit high-resolution graphics image using a 64-kbps-access line. The main source for the ISDN bandwidth limitation was the lack of reliable and high-bandwidth physical transmission medium. However, the progress made in fiber optic technology allows networks to operate at much higher rates, even over 155 Mbps, than the basic service rate described for ISDN. Consequently, a high-speed ISDN network called B-ISDN can provide all those services requiring high bandwidth. B-ISDN utilizes the progress in fiber optic technology, systems concepts, and speech coding and chip technology [10,40,47,53,54].

## 2.1.2 Broadband ISDN

B-ISDN is a service-independent network capable of transporting all different services and sharing all its available resources. There are many advantages of using B-ISDN such as the flexibility to adapt to changing or new needs, the efficiency in using available resources among all services, and the overall cost reduction of the design, manufacturing, operations and maintenance [42,73].

The term broadband is defined as a "service or system requiring transmission channels capable of supporting rates that are greater than the primary access rate [22]." The concepts of B-ISDN are summarized in [22] as follows: "B-ISDN supports switched, semi-permanent and permanent, point-to-point and point-to-multipoint connections and provides on demand, reserved and permanent services. Connections in B-ISDN support both circuit and packet mode services of a mono and multi-media type and of a connectionless or connection oriented nature and in a bi-directional and uni-directional configuration. A B-ISDN contains intelligent capabilities for the purpose of providing service characteristics, supporting powerful operation and maintenance tools, network control, and management."

B-ISDN is expected to support interactive and distributive services, bursty and continuous traffic, connection-oriented and connectionless services, and point-to-point and complex communications, all in the same network. The types of services B-ISDNs are envisaged to offer can be characterized by one or more of the following

attributes: high bandwidth, bandwidth on demand, varying quality of services parameters, guaranteed service levels, point-to-point, point-to-multipoint, and multipoint-to-multipoint connections, constant-bit-rate and variable-bit-rate services, and connection-oriented or connectionless services [40,53,54].

ITU-T classified possible broadband applications into four categories [53]:

- 1. Conversational services (Video/audio information transmission services)

- 2. Retrieval services (High-resolution image retrieval services)

- 3. Messaging services (Video mail services)

- 4. Distribution services:

- Without user-individual presentation control (Document distribution services)

- With user-individual presentation control (Full-channel broadcast videography)

Accordingly. B-ISDN should be capable of assigning useable capacity dynamically on demand. In addition, B-ISDN switching fabrics should be capable of switching all types of services. In recent years, large technological progress has taken place both in the field of electronics and in the field of optics. This progress allows the economical development of new telecommunication networks running at very high speeds. The evolution of highly reliable fiber systems into the access network provides the necessary high bandwidth required for B-ISDN. In fact, one type of optical fiber called monomode fiber has almost unlimited bandwidth transmission. As technology advances rapidly to meet the need for high-speed communications, the bottlenecks in communications networks are moving from transmission medium to the

communications processors. The throughput and end-to-end delay requirements of applications become limited by the processing power at network nodes, necessitating fast network protocols. The suitability of current network protocols for B-ISDN has not been fully addressed in the standardization committees. One issue that is resolved is the transfer mode: ATM principle is accepted by ITU-T as the ultimate transfer mode solution for B-ISDN. Different transfer modes exist in the telecommunication world each with different features. The following transfer modes are listed in increasing order of protocols complexity and bit rate fluctuation: circuit switching. multirate circuit switching, fast circuit switching, ATM, fast packet switching, frame relaying, frame switching, and packet switching [10,12,40,41,53,54].

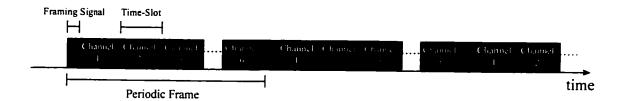

Circuit switching transfer mode is used in telephone networks. To transport information from one node to another, a circuit is established by reserving all links from the source to the destination for a complete duration of the connection. The transmission is based on the STM (Synchronous Transfer Mode) technique. The principle of the STM technique is illustrated in Figure 2.1. The time axis is divided into n-slot frames with one slot dedicated to each channel. Each slot is one time-unit long and can carry a single data unit. A data unit associated with a given channel is identified by its position in the transmission frame. A connection always uses the same time slot in the frame during the complete transmission period. For this reason, all channels for different services must have the same bit rate [40].

Figure 2.1 Synchronous Transfer Mode.

Multirate circuit switching transfer mode is an improved version of the circuit switching transfer mode. It uses the same periodic frame format with a fixed basic channel rate as shown in Figure 2.1. However, each connection can allocate multiple of the fixed basic channel rate. Each channel of one connection must remain synchronized. The required channel synchronization increases the complexity of the switching systems. In addition, the management and correlation of large number of basic rate channels (140,000 basic channels of 1 kbps for HDTV) becomes very complicated. By increasing the bandwidth of the selected basic rate, the channel management complexity is reduced for high bit rate applications. However, the cost is the enormous waste of redundant bandwidth for the low speed applications such as the voice transmission. An enhanced version of this transfer mode was proposed to use multiple basic rates. This enhancement did not overcome a major drawback of this transfer mode; namely its inability to cope efficiently with fluctuating and bursty character sources. Since the resources in the network, with channel bit rate equal to or greater than the peak bit rate, are reserved even when there is an idle period for the sending terminal [40].

Fast circuit switching transfer mode extends the concepts of circuit switching to sources with fluctuating and bursty nature. The resources in the network are reserved only during active transmission periods, and released when the source is idle. Services with different bit rates can be accomplished when the fast and multirate circuit switching transfer modes are combined. The resulting multirate fast circuit switching

transfer mode allows the use of different information rates efficiently. However, the complexity of designing and controlling such a system is high since it is required that the system must be able to set up and tear down connections in very short periods [40]. In *packet switching transfer mode*, user information is encapsulated in packets. These packets contain additional information used inside the network for routing, error correction and flow control. These packets have variable length and require a complex buffer management inside the network. This transfer mode has complex protocols performing error checking and flow control on every link of the connection because of the low-quality physical transmission medium available. The protocol complexity increases the processing requirements and switching delay inside the network since link-by-link error and flow control is required to guarantee an acceptable end-to-end performance on each link of the network [40].

Frame switching transfer mode is similar to packet switching transfer mode except it has less functionality such as multiplexing of logical channels. The functional reduction in the protocols increases the network throughput four times the speed of packet switching mode [40].

Frame relaying transfer mode is similar to frame switching transfer mode except that the protocols do not have error and flow control. Only CRC checking is performed to discard erroneous frames. The functional reduction in the protocols has increased the network throughput dramatically from 8 Mbps to 140 Mbps. However.

error corrections are performed between the source and destination nodes. This requires high-quality physical transmission medium [40].

Fast packet switching transfer mode is similar to packet switching mode with minimal functionality in the network. The main aim of this transfer mode is to transmit information efficiently at a very high-speed rate [40].

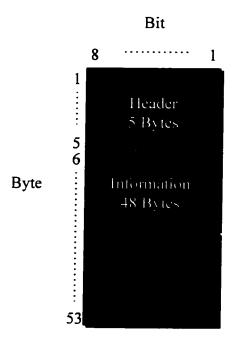

Asynchronous transfer mode is the same as the fast packet switching with fixedsize packets, referred to as ATM cells. The packet-oriented nature of ATM is well suited to applications with bursty traffic characteristics. The short fixed-size cells guarantee a jitter (the variance of the delay) compatible with the constraints imposed by voice or moving image transmission. These cells offer full bandwidth flexibility at high transmission rates. They also provide the basic framework for guaranteeing the quality of service requirements of applications with a wide range of performance metrics, while allowing statistical multiplexing where several variable-bit-rate connections can share a link with a capacity less than the sum of their peak bit rate requirements. Figure 2.2 illustrates the principle of the ATM technique. The ATM approach does not require a framed transmission system. The label contained in the cell's header identifies the connection. So that, a data unit (ATM cell) associated with a specific channel may occur at any position and several connections can be multiplexed on any link. ATM is an attempt to utilize the properties of both the packet-switch and circuit-switch networks in an integrated network as shown in Figure 2.3.

Figure 2.2 Asynchronous Transfer Mode.

Figure 2.3 ATM combines the flexibility of packet switching with the simplicity of circuit switching.

ATM combines the simplicity of circuit switching with the flexibility of packet switching where it does not check the fixed-size cell contents and it is a connection-oriented technique using virtual channels and high bit rate flexibility. In fact, it is a compromise that allows the integration of different services with different characteristics and requirements in the same network using a unique interface. ATM is a connection-oriented, packet switching and multiplexing technique to transfer information over a B-ISDN network where established end-to-end paths are required prior to the beginning of information transfer [38,40,53,54,65,73].

In general, the transfer mode of B-ISDN is envisaged to:

- support and integrate all existing networks as well as other future applications with unknown characteristics

- minimize switching complexity

- minimize the processing load per cell at intermediate switching nodes to support very high transmission speeds

- minimize the buffer requirements at the intermediate nodes to bound the delay and buffer management complexity

- provide the basis for guaranteeing quality of service requirements for each service in the network

ATM is an attempt to meet all the above objectives. It has various features that extend the capabilities of current packet-switching networks toward incorporating the

most desired features of circuit switching to support real-time traffic most efficiently [38,40,53,54].

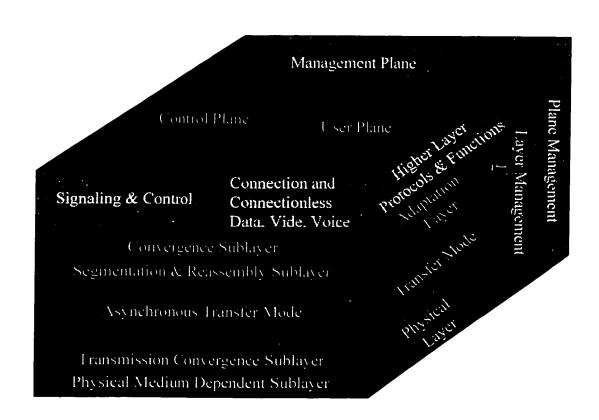

B-ISDN standards are being developed by a number of bodies around the world and are being finalized by ITU-T. The initial ITU-T recommendation on B-ISDN was published in 1988 [22]. There are thirteen ITU-T recommendations outlining the fundamental principles and initial specifications for B-ISDN approved in 1990. These recommendations include the B-ISDN Protocol Reference Model (PRM) as shown in Figure 2.4. The PRM consists of three planes: control, user and management. These planes use three layers: physical, ATM and ATM adaptation [38,40,53,54].