# Timing Driven Global Routing for Standard Cell Design

by

#### Amir Hashmi

A Thesis Presented to the

FACULTY OF THE COLLEGE OF GRADUATE STUDIES

KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

MASTER OF SCIENCE

In

**COMPUTER SCIENCE**

June, 1995

#### INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

UMI

| • |

|---|

|   |

|   |

|   |

# Timing Driven Global Routing for Standard Cell Design

ву Amir Hashmi

A Thesis Presented to the

FACULTY OF THE COLLEGE OF GRADUATE STUDIES

KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

# MASTER OF SCIENCE

**Computer Science**

**June 1995**

UMI Number: 1375127

UMI Microform 1375127 Copyright 1995, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

UMI

300 North Zeeb Road Ann Arbor, MI 48103

# KING FAHD UNIVERSITY OF PETROLEUM AND MINERALS DHAHRAN, SAUDI ARABIA COLLEGE OF GRADUATE STUDIES

This thesis, written by

#### **Amir Hashmi**

under the direction of his Thesis Advisor, and approved by his Thesis committee, has been presented to and accepted by the Dean, College of Graduate Studies, in partial fulfillment of the requirements for the degree of

### MASTER OF SCIENCE IN COMPUTER SCIENCE

|                                   | Thesis Committee :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                   | 2 SS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                   | Dr. Talal H. Maghrabi (Chairman)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                   | furful Wor. Habib Youssef (Co-Chairman)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                   | S 6/1.0/4,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 90/4/13                           | Dr. Mohammed Al-Suwaiyel (Member)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Dr. Muhammed Al-Mulhem            | Sadiq Sait. M.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Department Chairman               | Dr. Sadiq M. Sait (Member)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ali                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Dr. Ala H. Rabeh                  | and the same of th |

| Dean, College of Graduate Studies |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Date: 1 7 95                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

# Timing Driven Global Routing for Standard Cell Design

MS Thesis

Amir Hashmi

June, 1995

#### Dedicated to

my parents

&

my brother and sisters

whose prayers, guidance, and inspiration led to

this accomplishment

#### Acknowledgment

In the name of Allah, Most Gracious, Most Merciful. All praise to Allah, subhanahu-wa-ta'ala, the Almighty, for all his blessings on me. I feel priviledged to glorify His name in the sincerest way through this small accomplishment. I seek His mercy, favor, and forgiveness. And I ask Him to accept my little effort.

Acknowledgement is due to King Fahd University of Petroleum and Minerals for providing support to this research work.

I would like to express my deep gratitude to my thesis committee chairman, Dr. Talal H. Maghrabi for his assistance and support. I am indebted to my thesis co-chairman Dr. Habib Youssef for his time, guidance and suggestions. I am also grateful to my committee members Dr. Sadiq M. Sait and Dr. Mohammad Al-Suwaiyel for their sincere help and advice.

I am thankful to the chairman of department of Information and Computer Scdience, Dr. Muhammed Al-Mulhem and other faculty members for their cooperation.

I express my gratitude to my friends Shahid Tanvir, Tambi Baik and Khalid Al-Farra for their constant help, guidance and moral support during this work. I am thankful to my fellow graduate students and all my friends on the campus especially Asim, Nayyar and Shahid Ali who provided a wonderful company throughout my stay at KFUPM.

Special thanks go to my fellow and friend late Emad Amin Khan for his moral support and encouragement. May Allah bless his soul.

Last but not the least, thanks are due to the members of my family for their emotional and moral support throughout my academic career. This work is dedicated to my family for taking pains to fulfill my academic pursuits and building my personality.

# Contents

|   | List of Tables |                                               |      |  |  |

|---|----------------|-----------------------------------------------|------|--|--|

|   | List           | of Figures                                    | viii |  |  |

|   | Abs            | tract (English)                               | x    |  |  |

|   | Abs            | tract (Arabic)                                | хi   |  |  |

| 1 | 1 Introduction |                                               |      |  |  |

|   | 1.1            | Overview                                      | 1    |  |  |

|   | 1.2            | Standard Cell Design                          | 4    |  |  |

|   | 1.3            | Organization of the Thesis                    | 8    |  |  |

| 2 | Lite           | erature Review                                | 9    |  |  |

| 3 | Rec            | tilinear Steiner Tree Problem                 | 17   |  |  |

|   | 3.1            | Introduction                                  | 17   |  |  |

|   | 3.2            | Rectilinear Steiner Tree Problem: An Overview | 19   |  |  |

|   |     |        |                                                  | iv |

|---|-----|--------|--------------------------------------------------|----|

|   | 3.3 | Summa  | ary                                              | 24 |

| 1 | Tab | u Sear | ch and Simulated Annealing                       | 25 |

|   | 4.1 | Tabu S | Search                                           | 25 |

|   |     | 4.1.1  | Introduction                                     | 25 |

|   |     | 4.1.2  | Tabu Restrictions                                | 26 |

|   |     | 4.1.3  | Aspiration Criteria                              | 28 |

|   |     | 4.1.4  | Algorithmic Description                          | 29 |

|   | 4.2 | Simula | ated Annealing                                   | 32 |

|   |     | 4.2.1  | Introduction                                     | 32 |

|   |     | 4.2.2  | The Algorithm                                    | 33 |

|   | 4.3 | Summ   | ary                                              | 35 |

| 5 | Glo | bal Ro | uting for Standard-Cell Design                   | 36 |

|   | 5.1 | Introd | uction                                           | 36 |

|   | 5.2 | Globa  | l Routing                                        | 38 |

|   |     | 5.2.1  | Determination of Timing bounds on Nets           | 38 |

|   |     | 5.2.2  | Netlist Extraction                               | 40 |

|   |     | 5.2.3  | Placement of feed-throughs                       | 41 |

|   | 5.3 | Timin  | g-Driven Approach to Global Routing              | 42 |

|   |     | 5.3.1  | Delay Model                                      | 42 |

|   |     | 5.3.2  | Objective Function of the Initial Global Routing | 49 |

|   |      | 5.3.3   | Ordering of Nets                                      | 51 |

|---|------|---------|-------------------------------------------------------|----|

|   |      | 5.3.4   | Partitioning and Classification of nets               | 52 |

|   |      | 5.3.5   | Formation of Feed-through Zones                       | 54 |

|   |      | 5.3.6   | Routing Inside Zones                                  | 56 |

|   | 5.4  | Comp    | lexity of the Algorithm                               | 62 |

|   | 5.5  | Summ    | ary                                                   | 63 |

| 6 | Cha  | nnel I  | Density Optimization                                  | 64 |

|   | 6.1  | Introd  | uction                                                | 64 |

|   | 6.2  | Optim   | nization of channel density using Tabu Search         | 65 |

|   | 6.3  | Cost I  | Function                                              | 65 |

|   | 6.4  | Initial | , Current and Best Solutions                          | 68 |

|   | 6.5  | Gener   | ation of Moves                                        | 68 |

|   | 6.6  | Tabu    | List                                                  | 69 |

|   | 6.7  | Aspira  | ation Level Criteria                                  | 70 |

|   | 6.8  | Optin   | nization of channel density using Simulated Annealing | 72 |

|   | 6.9  | Resul   | ts and Discussion                                     | 74 |

|   | 6.10 | Sumn    | nary                                                  | 87 |

| 7 | Cor  | aclusio | on and Future Work                                    | 88 |

|   | 7.1  | Concl   | usion                                                 | 88 |

|   | 7.2  | Futur   | e work                                                | 91 |

|              | vi |

|--------------|----|

| Bibliography | 92 |

| Vita         | 99 |

.

# List of Tables

| 5.1 | Area and fringe capacitance values                                 | 46 |

|-----|--------------------------------------------------------------------|----|

| 5.2 | Sheet resistance values                                            | 46 |

| 6.1 | Test cases statistics                                              | 78 |

| 6.2 | Test cases zones' statistics                                       | 78 |

| 6.3 | Comparison of cost reduction and execution time between SA and TS. | 78 |

| 6.4 | Comparison of wire length between OASIS and TDR for metal1 and     |    |

|     | metal2                                                             | 79 |

| 6.5 | Percent increase/decrease of metal1 and metal2 obtained from TDR   |    |

|     | when compared with OASIS.                                          | 79 |

| 6.6 | Comparison between OASIS and TDR.                                  | 80 |

| 6.7 | Comparison between OASIS and TDR with and without net ordering.    | 80 |

# List of Figures

| 1.1 | Two possible paths connecting a pair of points. (a) The shortest path. |    |

|-----|------------------------------------------------------------------------|----|

|     | (b) A longer path with more bends [1]                                  | 3  |

| 1.2 | Standard cell layout model [2]                                         | 5  |

| 1.3 | A set of net segments [3]                                              | 7  |

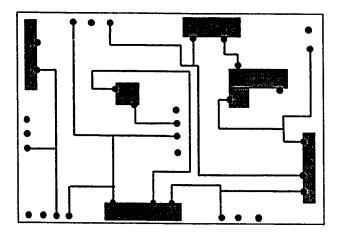

| 3.1 | A printed circuit board                                                | 18 |

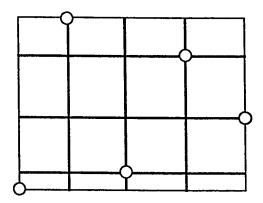

| 3.2 | Hanan's description of a grid graph [4].                               | 21 |

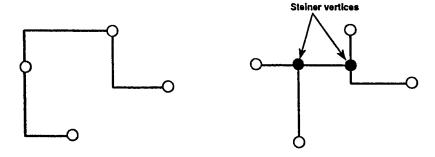

| 3.3 | MST (left) and MRST (Right) for the same four points                   | 22 |

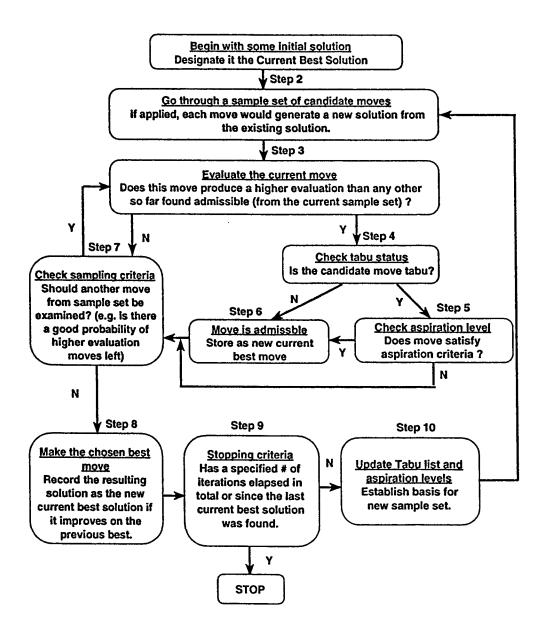

| 4.1 | Tabu search algorithm [5]                                              | 30 |

| 4.2 | Simulated annealing algorithm                                          | 34 |

| 4.3 | The accept function                                                    | 34 |

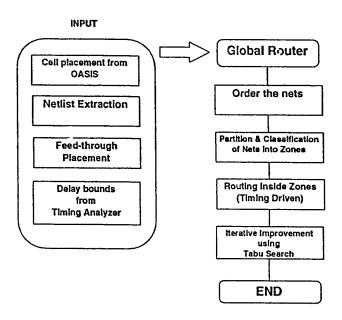

| 5.1 | Main steps of global router.                                           | 38 |

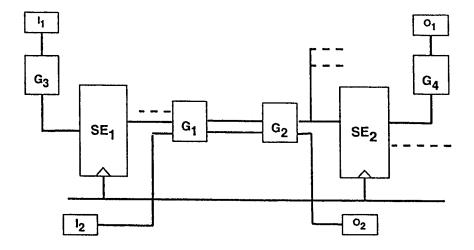

| 5.2 | Four types of paths                                                    | 39 |

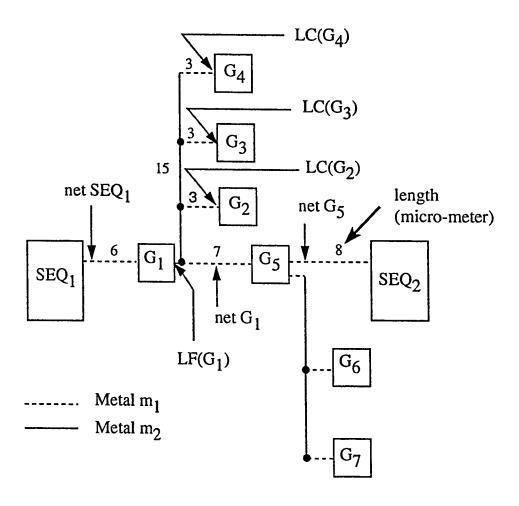

| 5.3 | Delay model used in this work                                          | 45 |

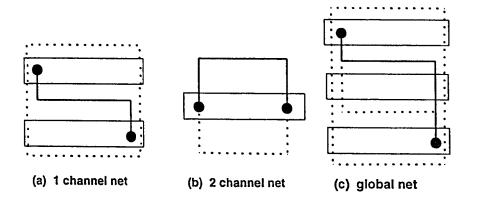

| 5.4 | A classification of nets                                               | 53 |

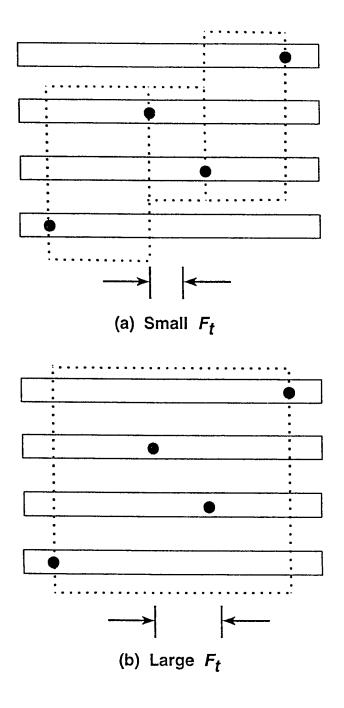

| 5.5 | Dependence of the size of feed-through zone on feed-through interval. | 55 |

|-----|-----------------------------------------------------------------------|----|

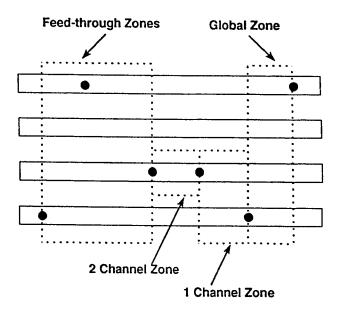

| 5.6 | Partition of a net into zones                                         | 56 |

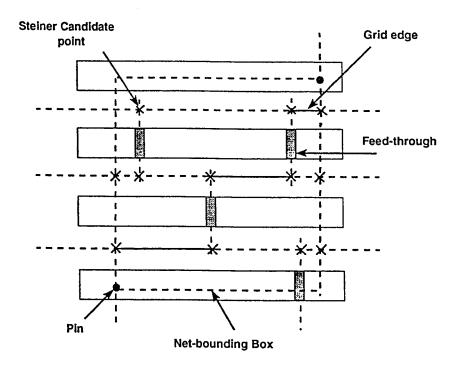

| 5.7 | Dijkstra's algorithm.                                                 | 58 |

| 5.8 | Routing inside 2-terminal global Zone                                 | 59 |

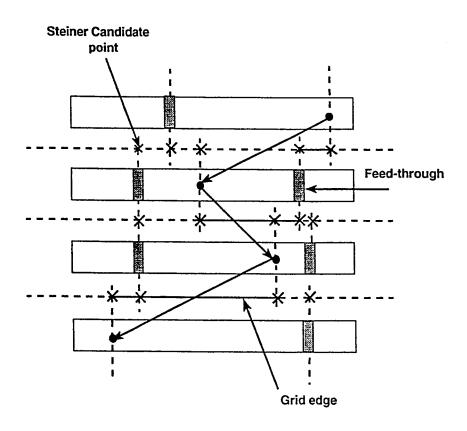

| 5.9 | Routing inside feed-through zone                                      | 61 |

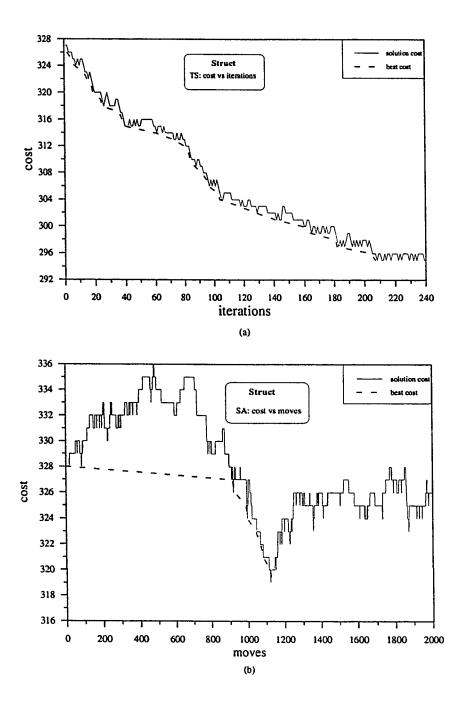

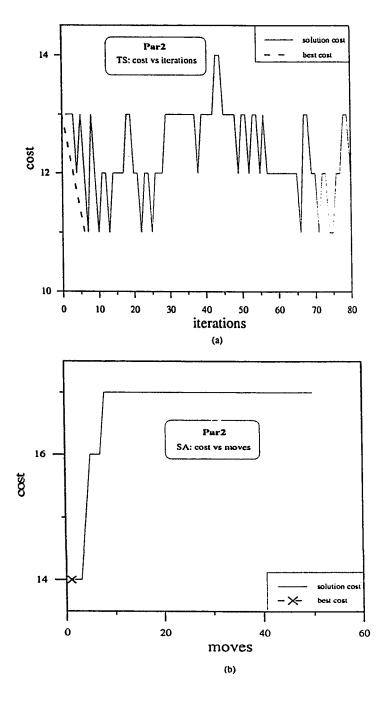

| 6.1 | Comparison of TS and SA for the Struct circuit                        | 81 |

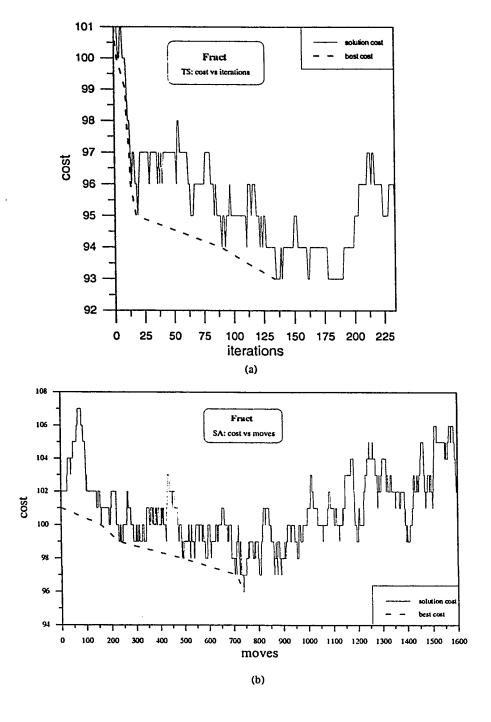

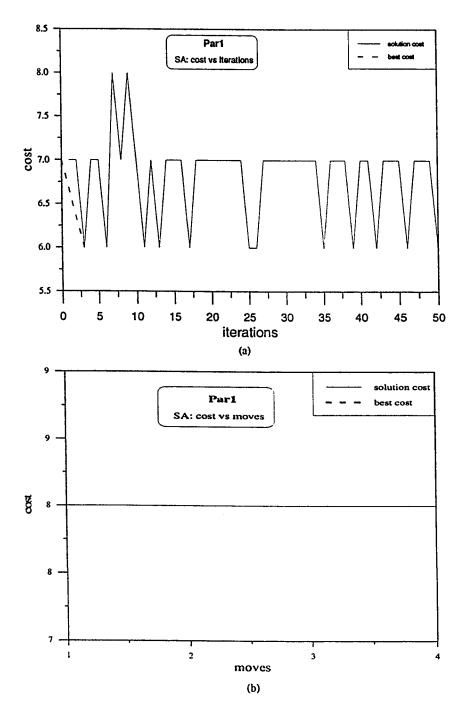

| 6.2 | Comparison of TS and SA for the Fract circuit                         | 82 |

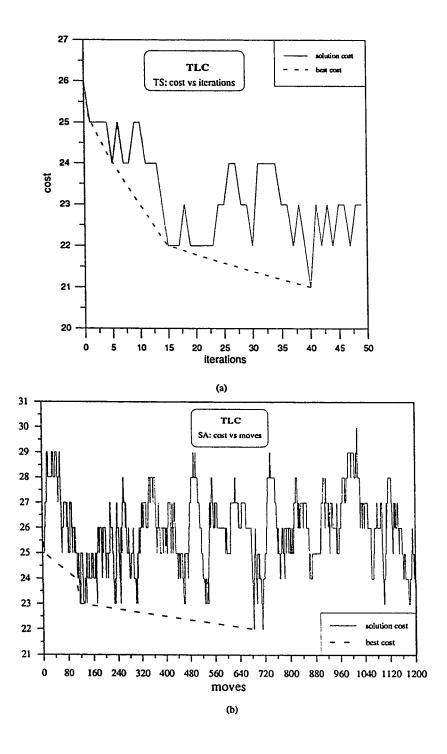

| 6.3 | Comparison of TS and SA for the TLC circuit                           | 83 |

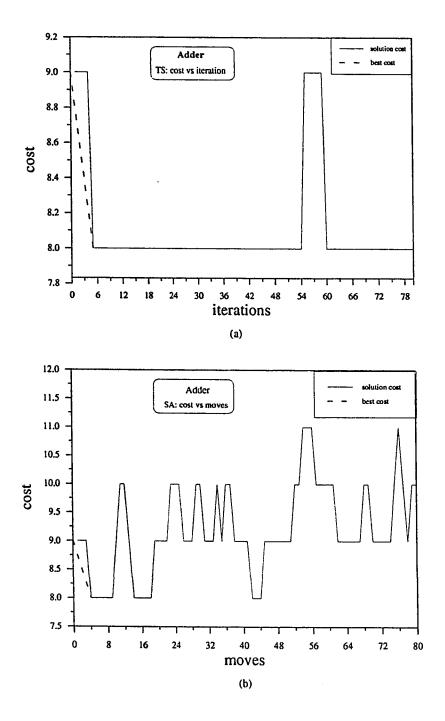

| 6.4 | Comparison of TS and SA for the Adder circuit                         | 84 |

| 6.5 | Comparison of TS and SA for the Par2 circuit                          | 85 |

| 6.6 | Comparison of TS and SA for the Parl circuit.                         | 26 |

#### Abstract

Name: Amir Hashmi

Title: Timing-driven Global Routing

for Standard Cell Design

Major Field: Computer Science

Date of Degree: June, 1995

In the VLSI design process, interconnect delays play an important role in determining the performance of the circuits as they can make it impossible to achieve the required clock rate. Nowadays, it is rare to find a placement program that does not take into consideration timing issues of the circuit. However, routing did not receive similar attention. We believe that timing of the layout can be further improved if timing critical nets are given preferential treatment during routing. Such an approach has been taken in this work. This thesis accomplishes the implementation of a timing-driven global router program for standard cell VLSI design. The solution quality has been measured in terms of path delays, interconnection length and layout area. An iterative improvement technique called Tabu Search has been used to improve the initial global routing solution. This technique has been compared with another technique called Simulated Annealing. Tabu search has resulted in better solutions with less execution times in all the test cases used.

Master of Science Degree

Department of Information and Computer Science

King Fahd University of Petroleum and Minerals

Dhahran, Saudi Arabia

June 1995

#### خلاصة الرسالة

الإسم : عامر هاشمي

عنوان الرسالة : تسليك الدوائر المحكوم بالزمن للتصاميم ذات الخلايا القياسية

التخصص : علوم الحاسب الآلي

تاريخ الشهادة : حزيران / يونيو ١٩٩٥ م

تلعب الإعاقات الزمنية بين التوصيلات المختلفة في عملية تصميم الدوائر المتكاملة ذات النطاق الواسع جدا دورا مهما في تحديد أداء الدوائر، اذ أنه من الممكن أن تؤدي هذه الإعاقات إلى استحالة الحصول على السرعة المطلوبة للساعة. و من النادر في عالمنا اليوم أن يوجد برنامج لتوضيع الدوائر لا يأخذ بعين الإعتبار عنصر الزمن للدوائر. ولكن الحال ليست كذلك بالنسبة لتسليك الدوائر. فنحن نعتقد بأن مزامنة مخطط ما للدوائر يمكن أن تتحسن إذا تم تسليك أسلاك الوصل الحرجة أولا. و لقد إتبع هذا الاسلوب في هذا العمل. في هذه الرسالة يتم تنفيذ برنامج تسليك للدوائر محكوم بالمزامنة لتصميم الدوائر المتكاملة ذات النطاق الواسع جدا وذات الخلايا القياسية. و يتم قياس نوعية الحل بواسطة مسارات الإعاقات الزمنية, طول التوصيلات, و مساهمة مخطط الدوائر. وقد إستخدم أسلوب تحسيني متكرر يسمى طريقة (Tabu Search) لتحسين الحل الأولى لعملية تسليك الدوائر. وقد قورن هذا الأسلوب المسلوب آخر يسمى طريقة (Simulated Annealing). وقد نتج عن طريقة (Search كالمناوب المتخدمة المنوب المتخدمة المناوب التي استخدمت.

#### درجة الماجستير في العلوم

جامعة الملك فهد للبترول و المعادن الظهر ان – المملكة العربية السعودية

حزيران / يونيو ١٩٩٥م

# Chapter 1

# Introduction

#### 1.1 Overview

In the automated design of VLSI circuits, the two principal design steps are placement and routing. The placement step involves the assignment of cells of the circuit

to fixed locations of the chip, while routing is the task of finding suitable paths to

interconnect the desired set of pins of the cells. A set of pins or terminals is called a

net with one terminal designated as a source and the rest as sinks. The term suitable

path is meant for those paths that minimize a given objective function, subject to

constraints. Constraints may include number of routing layers, minimum separation

between adjacent wires of different nets, minimum width of routing wires, timing,

etc. Objective functions include the reduction in the overall required wirelength and

avoidance of timing problem due to delays of interconnection.

Routing takes a major portion of design time (about 30%) and as much as 50% of layout area. In order to achieve routing for generally large number of interconnected cells, computer programs called *routers* are used which precisely define the electrical paths among the pins of the interconnected cells.

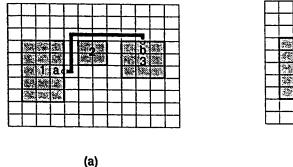

The prime objective of a routing algorithm is to achieve circuit interconnection in the minimum possible area, automatically, and, with minimum manual intervention. Thus most routers are meant to achieve complete automatic routing using the smallest possible wire length to satisfy the performance criteria. For instance, consider Figure 1.1(a) in which a shortest path is shown with length equal to the Manhattan distance or the rectilinear distance between a and b. Manhattan distance between two points p and q is given by

$$dist(p,q) = |p_x - q_x| + |p_y - q_y|$$

(1.1)

The path in Figure 1.1(b) has more bends and is longer. Thus a signal will take longer time to travel on this path.

The routing process basically includes two major steps: global routing and detailed routing. Global routing is performed first to achieve a routing plan for the nets such that they can be assigned to particular regions. Moreover, to optimize the routing plan some additional connection points are determined to get connection among various routing areas (channels). In detailed or channel routing, each routing region is picked up and nets are assigned to particular tracks in that region

Figure 1.1: Two possible paths connecting a pair of points. (a) The shortest path. (b) A longer path with more bends [1].

to achieve the complete routing of all the nets.

With the advancement in VLSI fabrication technology, the switching delays of gates have been reduced to the order of picoseconds, and thus interconnection delays are becoming increasingly important in determining the speed of the circuits. In the design of dense high performance circuits, the interconnection delays contribute as much as half of the clock cycle. Thus large interconnection delays can make it impossible to achieve the required clock rate.

In the past, characteristics like connectivity of modules (e.g. macro-cells or standard cells), routability of the nets with the available routing constraints like routing space and pins and pad locations, and layout area were the ones used to perform physical design without any special concern for timing. But this trend has changed. Now, timing is included as one of the most important factors guiding the design process. Performance-driven layout design has received considerable attention in the past several years. Work has been done mostly on the timing-driven placement

ن.

problem, where a number of methods have been developed for placing blocks or cells in timing critical paths close together. Only limited work has been done for the timing-driven interconnection problem. The objective of our work is to implement a timing-driven routing program for standard cell design methodology that will make use of the timing constraints assigned to each net to keep the maximum delay of any net minimum.

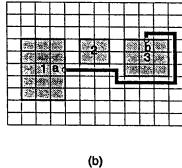

#### 1.2 Standard Cell Design

Standard cell design is the object of this research. In this design style, all cells (flip-flops or gates) have the same height but varying widths. The width of the cells are usually a multiple of some grid unit depending upon the technology. For  $2\mu$  MOSIS CMOS technology used in this work, the grid is 8 microns. Cells are placed in an array of horizontal rows, and all interconnections of signal nets are made by channel routing in the spaces between the adjacent rows. For each terminal on one side of a standard cell there is also an electrically common terminal on the opposite side, either of which can be selected for routing. The standard cell layout model is shown in Figure 1.2. The four blocks surrounding the cell rows on the top, bottom, right and left are the external I/O buffers. The rectangular areas in between the cell rows are the routing regions or channels. Feed-through cells are inserted within the cell rows in order to provide interchannel routing (or there may be feed-through

Figure 1.2: Standard cell layout model [2].

pins available within the cells themselves).

The process of routing a standard cell integrated circuit is broken down into two phases. In the first phase, called global routing, nets or net segments are assigned to specific routing channels. As a result of this phase, the interconnection pattern in each channel is defined and is independent of all other channels. In the second phase, called detailed routing, the interconnection pattern in each channel is implemented by assigning the net segments to tracks and columns in the channel.

The interconnection pattern is defined by the set of nets  $N = \{n_i\}$  where each net  $n_i$  is a set of terminals  $t_j^i$  which are to be interconnected. One terminal  $s \in n_i$  is a designated source and the remaining terminals are sinks.

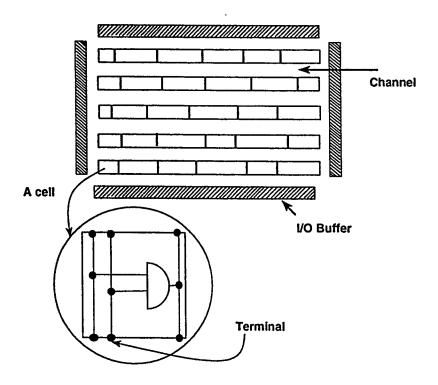

Each net can be modeled as a routing graph  $G(n_i) = (V_i, E_i)$ . Each vertex  $v_j \in V$  corresponds to a terminal  $t_j^i$  on  $n_i$ . A routing solution of a net  $n_i$  is a tree in  $G(n_i)$  which we call the routing tree of the net, connecting all terminals/nodes in  $n_i$ . Consider the example in Figure 1.3. Figure 1.3(a) shows the terminals of a single net as the vertical strips on a standard cell design, and Figure 1.3(b) shows the graph modeling this net. The vertices correspond to net segments and edges show the potential connectivity between the net segments. Figure 1.3(c) shows the final net segments based on a routing tree formed out of the routing graph. For the standard cell design style, the channels do not have prefixed capacities. Global routing consists of assigning nets to these channels so as to minimize channel densities and congestion, overall connection length, number of vias and feed-throughs. Vias

Figure 1.3: A set of net segments [3].

are the holes in the insulating layer that connect conductors of two metal layers generally used for routing. Global routing for standard cell presents two important problems: how many feed-throughs to use and where to place them [6]. Moreover, the more nets there are the more difficult it becomes to assign feed-throughs. For these reasons, a feed-through assignment optimization is needed which eases channel congestion, realizes minimum number of tracks and which does not depend on the routing order. In the same way, a larger via count introduced by a large number of bends in the net segments will result in longer timing delays and longer wire length and decrease in the performance of the circuit.

The objective of this thesis is to develop a timing-driven global routing program that can determine the routes of all nets of a given layout in such a way that a minimum chip area is obtained with minimum timing violation.

#### 1.3 Organization of the Thesis

The thesis is organized as follows: In Chapter 2 we present a thorough literature survey on the global routing problem for standard cell design. It also covers timing-driven approaches used for standard cell design. Chapter 3 discusses the Steiner tree problem which is an essential part of the routing problem. In Chapter 4 we describe an iterative improvement technique called *Tabu Search* which has been used in this thesis to improve the initial global routing solution. We also briefly discuss another iterative technique called *Simulated Annealing*. Chapter 5 describes in detail the global routing technique used in this research. Chapter 6 contains a complete description of the application of Tabu Search technique for improving the initial global routing result. Finally, Chapter 7 provides experimental results, conclusion and future directions for research.

## Chapter 2

### Literature Review

A very common technique for routing considers the layout as a maze. This technique may be used for both global and detailed routing. Finding a path to connect any two points belonging to the same net is similar to finding a path in the maze. The most widely used algorithm used for maze routing is Lee algorithm [7]. It attempts to find a path between two points on a grid that has obstacles (functional cells or already placed nets). The major characteristic of Lee algorithm is that if a path exists between two points, then it is definitely found. Furthermore, it is guaranteed to be the shortest available path. The running time of the algorithm is high i.e., if L is the length of the path to be found, then the processing time is  $O(L^2)$ . In addition, the memory requirement for an  $N \times N$  grid plane is  $O(N^2)$ . Some variations of Lee algorithm for speed improvement have been suggested by Hadlock [8] and Soukup [9].

Line Search Algorithms, first proposed by Mikami-Tabuchi [10] and Hightower [11], overcome the drawback of large memory requirements of Lee algorithm and its variations. Line search algorithms perform depth-first search in contrast to the breadth-first approach used by Lee algorithm and its variations. Due to this nature of line search algorithms, they do not guarantee finding the shortest path, and may need several backtrackings. They show completion rates similar to Lee algorithm, but with lesser execution time and memory requirement. The reason is that the entire routing space is not stored as a matrix as in the case of Lee algorithm, but the routing space and paths are presented by a set of line segments.

Global routing approaches fall into four general categories: (1) Sequential global routing approach, (2) mathematical programming approach, (3) stochastic iterative approach, and (4) hierarchical approach. A very detailed treatment of these approaches may be found in a recent book of Sait and Youssef [1].

Sequential global routing is a graph based approach. It is the simplest and most widely used approach. After the routing channels (regions) have been identified and the corresponding routing graph constructed, global routing proceeds as follows. Using the channel connectivity graph, we mark for each net those vertices of the graph in which the net has pins. Hence, routing the net is accomplished by finding a Steiner tree (preferably optimal) covering those marked vertices, where a Steiner tree is a tree of minimum total length, or depending on the context, an approximation to such a minimal tree. Two general approaches are possible in this case: (1)

the order dependent approach and (2) the order independent approach. When the available routing space is updated after the routing of each net, the approach is order dependent, otherwise it is order independent.

In the mathematical programming approach, global routing is performed as a 0-1 integer optimization program, where a 0-1 integer variable is assigned to each net and each possible routing tree of that net. The layout surface is modeled as a grid graph, where each grid or routing region is represented by a vertex. The arcs linking the vertices carry some weight which correspond to the capacity of the boundary between two nodes in terms of the number of tracks. We need to identify different possible routing trees for each net. We also associate an equation with each net such that only one of the many possible trees is selected. In spite of its elegance in finding a globally optimum assignment of the nets to routing regions, this technique has some major problems. These problems include the identification of a number of Steiner trees for each net, selection of the trees to guarantee the feasibility of the solution, and a large number of integer constraints.

In the stochastic iterative approach, the acceptable assignment of the nets is found by iteratively updating the current solution by ripping up and rerouting the nets. Following this approach, a simulated annealing (SA) application to global routing was first reported in 1983 [12]. The SA method is a stochastic sequential improvement method characterized by its ability to escape from local solutions and routing order. The SA method gradually reduces randomness in a system and

eventually arrives at the optimal solution. In the first reported application of SA, the authors have formulated the problem as an unconstrained integer program, where all edge capacities are equal to one. Nets with only two terminals and routes with just one bend are considered. The cost function used is a sum of the squares of the loads of all individual routing regions.

Another application of simulated annealing technique to global routing has been adopted in TimberWolf package [13]. TimberWolf package uses two metal layers for routing of standard-cell designs. After the initial placement phase, Timberwolf performs global routing in two stages. In the first stage, assignment of nets to the horizontal channels is done in order to minimize the overall channel densities. All nets that may be assigned to an adjacent channel (switchable nets) are identified in this stage. In the second stage, the aim is to reduce the overall channel densities by changing the channel assignments of the switchable nets. Refinement of the placement takes place after global routing. This is done by randomly interchanging neighboring cells. After each interchange, both stages of the global router are invoked to reroute the nets affected by the interchange. Simulated annealing is used only in the second stage of global routing (as well as the placement refinement phase).

Hierarchical approaches break down the overall global routing problem into subproblems such that the subproblems are solved individually. Solution of the original problem is obtained by combining the solutions of the subproblems. There are bottom-up and top-down approaches to hierarchical global routing. In the bottom-up approach, grid cells are combined into bigger cells until the entire chip is treated as a super cell. Global routing is performed at each level of the hierarchy for the individual cells considered for grouping. In contrast, for the top-down approach, a hierarchy is formed from super cell to cells, until each cell is an individual grid cell or a small group of individual grid cells. The design floorplan usually assists the top-down approach.

Among the several hierarchical formulation reported in the literature, the first one is due to Burstein and Pelavin [14]. Sadowska [15] and Lauther [16] have also proposed approaches similar to hierarchical global routing, and these were reported to produce better solutions than all other approaches.

Finding a Steiner tree for each net is an important problem in global as well as detailed routing. In one of the works [17] on this problem, a bottom-up hierarchical approach to building Steiner tree has been adopted. Based on a variation of a minimum spanning tree algorithm, a collection of partial steiner trees are formed at each level of the hierarchy. At a higher level of the hierarchy, these lower level Steiner trees are merged such that the duplicate edges are removed and cycles are avoided. Finally the tree corresponding to the top level of the hierarchy is the required Steiner tree for the current net.

A performance oriented rectilinear Steiner tree (POMRST) heuristic has been reported by Andrew Lim et.al. to solve the rectilinear Steiner tree problem [18]

which shows favorable results compared with existing techniques. The heuristic works iteratively by growing the Steiner tree one edge at a time. There are two stages during each iteration. In the first stage a spanning tree is constructed which is based on Prim's algorithm. In the second stage, the spanning tree edges are used to direct the selection of Steiner edges one at a time. The paper however does not provide much details about the delay model used to perform timing analysis.

In another approach [19], the idea of minimum spanning tree and Steiner tree algorithms has been used to formulate a routing tree with bounded radius and bounded interconnect delay.

Recently, a neural network technique has been used for global routing [20]. In this paper, the authors have suggested a two-layer neural network. The purpose of the first layer is to minimize net lengths and attain a uniform distribution of the nets over the routing channels. The second layer is meant to carry out effectively the channel capacity constraints.

With the advancement in VLSI technology, the interconnection delay has become significantly important in determining the circuit speed. Therefore, considerable focus has been given to performance-driven layout design during the past several years. Much of the efforts has been made in timing-driven placement problem, but limited progress has been reported for the timing-driven routing problem. The factors that lead to minimizing the interconnection delays are; the overall interconnection length, number of wiring bends, and other electrical characteristics like wire re-

sistance and capacitance. A recent approach [19] has formulated a global routing technique which minimizes the total interconnection length as well as maximum wiring delays. In another approach [21], timing analysis is used in global routing. While routing a connection, the slacks of the affected paths are updated at the corresponding path sinks. The maximized cost function is the slack of the longest path. The timing-driven global routing problem has also been formulated as a multiterminal, multicommodity flow problem with integer flows and additional timing constraints [22].

In the routing problem of physical design, the channel routing strategy is popular for its simplicity and efficiency. It is concerned with the actual interconnection of the nets after the initial routing plan has been established by the global router. The channel router takes each routing region and specifies for each net passing through that region particular tracks and wire segments that interconnect the net. Given sufficient routing space, channel router guarantees 100% completion of the routing. Due to this fact, a majority of modern IC (integrated circuit) routing systems adopt channel routing.

Numerous channel routing techniques are based on the left-edge algorithm, which route the channel one track at a time, and for which now exist many variations and extensions in the literature as can be seen in [23] and [24].

When the routing region is such that terminals lie on all the four sides of the region with no internal obstruction, then routing in such a region is called switchbox

routing. Switchbox routing is a harder problem than channel routing. An efficient algorithm has been reported by Luk [25] which is basically an extension and modification to the greedy heuristic of Rivest and Fiduccia [26].

## Chapter 3

## Rectilinear Steiner Tree Problem

#### 3.1 Introduction

The Steiner tree problem has been studied for the past three decades and has received considerable attention due to its involvement in a number of applications. Among these are planning problems in transportation networks, installing communication cables, building systems, printed circuit boards and VLSI design [4].

The Steiner problem comes in two different flavors: Euclidean Steiner problem and rectilinear Steiner problem. Consider two points i and j in the Euclidean plane and let their coordinates be  $(x_i, y_i)$  and  $(x_j, y_j)$ , respectively. We define the cost of the edge connecting the two points as the Euclidean distance  $\sqrt{(x_i - x_j)^2 + (y_i - y_j)^2}$  between i and j. Then, if V is a set of points in the plane, the Euclidean Steiner problem is the problem of connecting together the vertices in

Figure 3.1: A printed circuit board.

$V \cup S$  so as to minimize the total cost of the edges used, where S is the set of Steiner vertices, possibly empty. If |V| = 2 then the solution to this problem becomes a shortest-path calculation. Otherwise, the solution is a minimum cost spanning tree (MST) on some set of vertices  $V \cup S$ .

The rectilinear Steiner problem is the same as the Euclidean Steiner problem except that the cost of the edge connecting any two points i and j together is given by the Manhattan distance  $|x_i - x_j| + |y_i - y_j|$ . This problem is common in printed circuit board design and in VLSI design. In both, the wire length between components to be connected is minimized. Figure 3.1 shows an example.

Both of the above described problems are NP-hard [27]. They have received a fair amount of attention in the literature and many heuristic algorithms have been proposed.

A comprehensive survey of work relating to the Euclidean and rectilinear Steiner

problems has appeared in [4] and [28]. This chapter presents an overview of the rectilinear Steiner problem in general and its relation to the global routing problem in particular.

## 3.2 Rectilinear Steiner Tree Problem: An Overview

Since a comprehensive survey of work relating to Euclidean and rectilinear Steiner problems has recently been given by Hwang and Richards [4], we shall not give a complete literature survey here but instead concentrate on the application of rectilinear Steiner problem to the global routing problem in VLSI design.

Connecting n points of a net to make them electrically equivalent is a fundamental problem in a VLSI layout. The objective function that is usually considered is the least amount of wire in forming the connection. Due to a number of technological and engineering reasons, the segments are laid out in horizontal and vertical fashion. That is why the rectilinear distance function is used to calculate the length of segments. The tree that is formed is called a rectilinear Steiner tree constructed using the rectilinear metric.

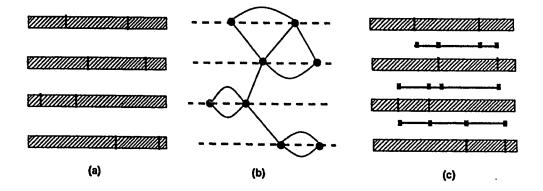

Finding a rectilinear minimum spanning tree (RMST) of the n given points is a possible approximate solution to the problem. Any "classical" minimum spanning tree (MST) algorithm can be used if the problem is considered as an instance of a complete graph with rectilinear distance edge weights. For instance, Prim's algorithm can be used if the problem is considered as an instance of a complete graph with rectilinear distance edge weights.

rithm can be implemented in  $O(n^2)$  time [29], i.e., quadratic time which is optimal for a complete graph. There are an infinite number of ways in which two points in an RMST can be connected using shortest rectilinear wires. Even if the wires are restricted to make just one bend there can still be two ways to place each wire. Therefore for a complete graph of n points, there are  $2^{n-1}$  possible placements of the n-1 wires which may have several segment overlaps. These segment overlaps must therefore be removed by the circuit designer.

Steiner trees usually provide shorter wirelength. A Steiner tree spans the n points but may contain additional points in the plane as vertices to provide additional internal branching. A Steiner tree refers to a tree of minimum total length or, depending on the context, an approximation to such a minimum cost tree. If overlaps are removed from a RMST, it effectively produces an (approximate) rectilinear Steiner tree (RST), though not necessarily minimal. There is no efficient procedure known for computing a minimum RST. Nonetheless, we formally define a minimum rectilinear Steiner tree problem in the plane as follows. Given a set S of n points in the plane, find a set S' of points that do not belong to S, called Steiner points, such that the spanning tree over  $S \cup S'$  is of minimum total length, with rectilinear distance edges that connect all the points in set S.

The minimum rectilinear Steiner tree (MRST) problem is a fundamental problem in global routing and wire estimation for VLSI circuit layout, where we are interested in connecting terminals of a net together. Several investigations of the

Figure 3.2: Hanan's description of a grid graph [4].

MRST problem have greatly influenced the research progress. Initially, Hanan [30] showed that if one extends horizontal and vertical grid lines through each of the n points in a set S, then there is an MRST whose Steiner points are all chosen from among the intersection points (the Steiner Candidate set) in the resulting grid. An example is given in Figure 3.2. Later, Gary and Johnson showed that despite this reduction on the solution space, the MRST problem is NP-complete [27]. This implies that an efficient optimal algorithm for the MRST problem is unlikely to be found. Thus, a number of heuristics have been proposed as surveyed in [28, 31]. In order to attack intractable problems, the basic goal is to formulate provably good heuristics, typically in the sense of having bounded worst-case error from optimal. Hwang [32] established that the rectilinear minimum spanning tree (MST) over S is a fairly good approximation to the MRST with a worst case performance ratio of 3/2; i.e., if c(T) represents the total cost of a tree T,  $c(MST)/c(MRST) \leq 3/2$ . Due

Figure 3.3: MST (left) and MRST (Right) for the same four points.

to immense time required to obtain the optimal solution for the MRST problem, all heuristics tabulate their performance by comparing themselves against this result. That is, any MST-based strategy which improves upon an initial MST topology (arrangement of points on the grid) and rearranges edges to induce Steiner points, will also have performance ratio of at most 3/2. Thus, a number of Steiner tree heuristics resemble classic MST construction and it remains an open question to find a heuristic method with performance ratio strictly less than 3/2. Figure 3.3 shows an MST and MRST for the same four-pin net.

An MST-based solution method may not be appropriate for VLSI routing applications. It has been shown in [33, 34] that the optimal Steiner tree, as well as heuristic MST-based rectilinear Steiner tree, will have a linear expected number of Steiner points. But having too many Steiner points is undesirable because each Steiner point is equivalent to introducing a via and vias are expensive in terms of delay and performance of the circuit. Thus, based on this fact, a more direct ap-

proach to adding Steiner points have been suggested by Kahng and Robbins [35]. Their iterated 1-Steiner heuristic repeatedly finds the next best possible Steiner point and adds it to the point set until no further improvement is possible. The performance ratio of this approximation algorithm is never as bad as 3/2 and it is proved to be not greater than 4/3 on the entire class of instances where the cost ratio C(MST)/C(MRST) is 3/2.

The Steiner tree algorithm is the fundamental part of a global routing algorithm in VLSI physical design. In the standard cell (objective of our work) and macro-cell layout styles, global routing is accomplished in a routing graph extracted from a given cell placement [36]. The graph edges correspond to routing channels, while some vertices correspond to intersections of channels and others correspond to interior points in the channels. A usual strategy for global routing consists of two phases [36]. A number of alternative routes are generated for each net in the first phase. The nets are independently treated one at a time with the objective of minimizing the total edge cost of the routing path in the graph. In the second phase, a specific route is selected for each net based on a criteria of channel capacity, overall chip area and/or total interconnection length.

Most existing Steiner tree algorithms of wire-mode or timing-driven global routers take the minimization of total wire length as the objective. Only a few consider the timing constraint during the construction of global routing tree.

## 3.3 Summary

This chapter provided an overview of the rectilinear Steiner tree problem and its relation to the global routing algorithms in VLSI design. In Chapter 5 we will present a timing-driven global routing scheme based on the technique of dividing a net into zones and thus reducing the complex problem of determining the routing tree of a net, into simpler smaller problems of routing net segments in different zones. An iterative improvement technique has been applied to improve the routing result in terms of delay bounds and channel densities.

# Chapter 4

# Tabu Search and Simulated

# Annealing

## 4.1 Tabu Search

#### 4.1.1 Introduction

Tabu search is a general iterative technique, that was originally proposed by Glover [37, 5, 38] for finding good solutions to combinatorial optimization problems. This simple and elegant technique is regarded as a higher-level method, or meta strategy for solving optimization problems. It has been successfully applied to a number of computationally hard problems like graph coloring [39], graph partitioning [40], VLSI placement [41], circuit partitioning [42], maximum independent set problem

[43], etc.

In general terms, tabu search is an iterative procedure that starts from some initial feasible solution and attempts to determine a better solution in the manner of a greatest-descent algorithm. It does not employ pure randomization like simulated annealing nor does it take the restrained approach that the proper rate of descent will make the final solution closer to a global optimum [40]. Instead of terminating upon reaching a point of local optimality, tabu search structures the operation of its embedded heuristic in a manner that permits it to continue. This is accomplished by forbidding moves with certain attributes (making them tabu), and choosing moves from those remaining to which the embedded heuristic assigns a highest evaluation. In this respect, tabu search employs a mechanism of control which constraints and frees the search process. This corresponds to tabu restrictions and aspiration criteria. Tabu search uses a flexible attribute-based memory structures to exploit historical search information more thoroughly than using rigid memory structures (such as branch and bound) or by memoryless systems (such as simulated annealing).

#### 4.1.2 Tabu Restrictions

As opposed to the randomness of the search in simulated annealing, tabu search uses a more systematic approach. Instead of choosing a neighboring solution (a solution reachable from the current solution by making a move) at random, tabu

search examines a number of neighbors and selects the best neighborhood solution by making a move among all candidate moves. This best candidate solution may not improve the current solution. Selecting the best neighborhood solution is unlike hill-climbing as it might make a down-hill move. Further, each solution in the solution space must be accessible to every other in a finite number of moves. This condition ensures that the neighborhoods cover every solution in such a way that it is possible to find the global optimum, given sufficient time.

With this approach, however, it is possible to reach a local optimum, ascend and then go back to local optimum, thus causing a cycle. Tabu restriction is a device to avoid such cycling by making selected attributes of these moves tabu (forbidden). Tabu list is a list containing forbidden moves. The tabu list is initially empty, constructed in the k first iterations and updated circularly in later iterations. The parameter k is the tabu list size. Normally the forbidden moves are the reverse of the k moves last performed. Thus, due to the tabu list, tabu search avoids returning to the solutions just visited, and since degrading moves are allowed, the algorithm has a chance of leaving a local minimum.

The most difficult part of applying tabu search is finding the right size of tabu list. No single rule gives good sizes for all classes of problems. If the tabu list size is too small the search will start cycling, and if it is too large the search might be too restrictive. Therefore, an appropriate list size can be determined by watching the occurrence of cycling when the size is too small and the quality of solution when the

size is too large. It is a question of finding the right compromise, typically depending on the specific problem investigated. However, good performance has been achieved with tabu list sizes from 5 to 12. In many applications the tabu list size of 7 seems to be quite effective.

### 4.1.3 Aspiration Criteria

This component of tabu search introduces diversification and intensification in the search by exploring new regions in the search space. It is a heuristic rule based on cost values, associated with feasible solutions, such that it temporarily overrides the tabu status if the move is sufficiently good. That is, we allow a move currently on the tabu list if it leads to a better solution than the current best solution. The purpose of aspiration criteria is to increase the flexibility of the algorithm while preserving the basic features that allows the algorithm to escape local optima and avoid cyclic behavior. At all times during the search procedure each cost c has an aspiration value that is the current lowest cost of all solutions arrived at from solutions with cost c. The actual aspiration rule is that, if the cost associated with a tabu solution is less than the aspiration value associated with the cost of the current solution, then the tabu status of the tabu solution is temporarily ignored and it is accepted as the next current solution. That is, although the tabu solution is not removed from the tabu list, its tabu status is overridden, and a move to the tabu solution may be made.

It is to be noted that like other optimization procedures, tabu search routine is ignorant of optimal cost values. this results in the procedure being unable to stop. Thus, a stopping criterion must be used, based on a maximum number of moves or a time limit.

### 4.1.4 Algorithmic Description

A complete description of tabu search is given in [44] which is shown in Figure 4.1. The functions performed by each of its steps are identified. A brief description of these steps is given below:

- 1. Start with an initial solution which can be generated by a number of ways, randomly or by a constructive process (our initial solution for global routing is generated constructively as explained in Chapter 5). The initial solution is also assumed to be the current best solution.

- 2. A set of moves is formed. Each move generates a trial solution. Hence we get a set of trial solutions. The number of moves to make depends upon the specific problem under consideration.

- Select the move which generates the best solution among a set of trial solutions.

Call this move a candidate move, that is, it is a candidate to be an admissible move.

Figure 4.1: Tabu search algorithm [5].

- 4. This step includes a key issue of the procedure, which is to establish a basis for deciding if a move being examined should be classified as tabu. It is checked that whether the candidate move is in the tabu list or not. As mentioned in the previous section, the tabu list records selected attributes of each move made. If the move is found to be tabu then go to step 5, otherwise go to step 6.

- 5. In step 4 if the candidate move is found to be tabu then check the aspiration criteria (as explained in Section 4.1.3). If the candidate move passes the aspiration criteria go to step 6 otherwise go to step 7.

- 6. The candidate move is considered admissible (i.e., either it is not tabu, step 4, or tabu but passes the aspiration criteria, step 5). Store this move as new current best move and go to step 8.

- 7. Select next best move from the sample set formed in step 2 or generate a new set of neighbor solutions and select the best among them and go back to step 3, otherwise go to step 8.

- 8. If the current best solution improves the previous best solution, store it as the best solution found so far.

- 9. Check for the stopping criterion. If the total number of iterations have been elapsed than stop, otherwise go to step 10.

10. Update tabu list and aspiration levels, that is, include the current best move into the tabu list and the objective function value as its aspiration value for the next iteration. Start new iteration by going back to step 2.

## 4.2 Simulated Annealing

#### 4.2.1 Introduction