## Timing Driven Floorplanning

by

Khalid Jawdat Kamel Al-Farra

A Thesis Presented to the

# FACULTY OF THE COLLEGE OF GRADUATE STUDIES

### KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

## DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

### **MASTER OF SCIENCE**

In

### **COMPUTER ENGINEERING**

June, 1995

#### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

A Bell & Howell Information Company 300 North Zeeb Road. Ann Arbor. MI 48106-1346 USA 313/761-4700 800/521-0600

.

. .

| <b>Timing Driven Floorplanning</b>                                                                                                                                                                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BY                                                                                                                                                                                                                                                                                                   |

| Khalid Jawdat Kamel Al-Farra                                                                                                                                                                                                                                                                         |

| A Thesis Presented to the                                                                                                                                                                                                                                                                            |

| FACULTY OF THE COLLEGE OF GRADUATE STUDIES                                                                                                                                                                                                                                                           |

| BY<br>Khalid Jawdat Kamel Al-Farra<br>A Thesis Presented to the<br>Kaculty OF THE COLLEGE OF GRADUATE STUDIES<br>KING FAHD UNIVERSITY OF PETROLEUM & MINERALS<br>DHAHRAN, SAUDI ARABIA<br>In Partial Fulfillment of the<br>Requirements for the Degree of<br>In<br>Computer Engineering<br>June 1995 |

| In Partial Fulfillment of the                                                                                                                                                                                                                                                                        |

| Requirements for the Degree of                                                                                                                                                                                                                                                                       |

| MASTER OF SCIENCE                                                                                                                                                                                                                                                                                    |

| In                                                                                                                                                                                                                                                                                                   |

| <b>Computer Engineering</b>                                                                                                                                                                                                                                                                          |

| June 1995                                                                                                                                                                                                                                                                                            |

UMI Number: 1375580

UMI Microform 1375580 Copyright 1995, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

## UMI

300 North Zeeb Road Ann Arbor, MI 48103

----

# KING FAHD UNIVERSITY OF PETROLEUM AND MINERALS DHAHRAN, SAUDI ARABIA COLLEGE OF GRADUATE STUDIES

This thesis, written by

### Khalid Jawdat Al-farra

under the direction of his Thesis Advisor, and approved by his Thesis committee, has been presented to and accepted by the Dean, College of Graduate Studies, in partial fulfillment of the requirements for the degree of

## **MASTER OF SCIENCE IN COMPUTER ENGINEERING**

Thesis Committee :

Dr. Habib Youssef (Chairman)

Dr. Sadiq Sail (Co-Chairman)

Dr. Mahammed S. T. Benten (Member)

Dr. Samir H. Abdul-Jauwad Department Chairman

Dr. Ala H. Rabeh Dean, College of Graduate Studies

6195 24 Date:

# **Timing Driven Floorplanning**

•

•

\_\_\_\_\_

MS Thesis

Khalid Jawdat Kamel Al-Farra

June, 1995

•

Dedicated to

My Parents,

whose prayers, guidance and inspiration

led to this accomplishment

•

----

الى من تعهدا هذا الغرس حتى أثمر ....

إهداء

إلى والدَيَّ العزيزين

#### Acknowledgment

First and foremost, all praise to the Almighty Allah Who gave me the courage and patience to carry out this work. I am happy to have had a chance to glorify His name in the sincerest way through this small accomplishment and ask Him to accept my efforts. May He guide us and the whole humanity to the right path. Peace and blessings of Allah be upon his prophet Muhammad.

Acknowledgement is due to King Fahd University of Petroleum and Minerals for providing support to this work.

My deep appreciation goes to my thesis committee chairman, Dr. Habib Youssef for his constant help, guidance and the countless hours of attention he devoted throughout the course of this work. He was always kind, understanding and sympathetic towards me. Working with him was indeed a wonderful and learning experience which I thoroughly enjoyed.

I am thankful to my thesis committee co-chairman, Dr. Sadiq M. Sait for his deep interest, and constructive criticism during the course of this work. I would also like to thank Dr. Muhammed S. T. Benten, Dean of CCSE and my thesis committee member for his consistent support.

•

I am also indebted to the department chairman, Dr. Samir Abdul-Jauwad and other faculty members for their support.

I am thankful to my fellow graduate students and my friends especially Mohammed Shahid Tanvir, Khalid Nassar, and Amir Hashmi for their cooperation.

Lastly, I am very grateful to my family members for their encouragement and moral support.

# Contents

•

**.** . .

|   | Acknowledgement            |       |          |      |    | i    |

|---|----------------------------|-------|----------|------|----|------|

|   | List of Tables             |       |          |      |    | vii  |

|   | List of Figures            |       |          |      |    | ix   |

|   | Abstract (English)         |       |          |      |    | xii  |

|   | Abstract (Arabic)          |       |          |      | 3  | ĸiii |

| 1 | Introduction               |       |          |      |    | 1    |

|   | 1.1 Overview of the System | ••••• | <br>•••• | <br> | •• | 7    |

|   |      |                                | iv |

|---|------|--------------------------------|----|

|   | 1.2  | Organization of the Thesis     | 12 |

|   | 1.3  | Conclusion                     | 14 |

| 2 | Lite | erature Review                 | 15 |

|   | 2.1  | Floorplanning Approaches       | 17 |

|   | 2.2  | Work on Floorplanning          | 20 |

|   | 2.3  | Work on Timing Driven Layout   | 24 |

|   | 2.4  | Conclusion                     | 27 |

| 3 | Ger  | neration of Timing Constraints | 28 |

|   | 3.1  | Introduction                   | 28 |

|   | 3.2  | Timing Analysis Concepts       | 30 |

|   |      | 3.2.1 Long Path Problem        | 31 |

|   |      | 3.2.2 Short Path Problem       | 32 |

|   | 3.3  | Delay Model                    | 33 |

.

|   | 3.4 | Graph Model                           |

|---|-----|---------------------------------------|

|   | 3.5 | Critical Path(s) Prediction           |

|   |     | 3.5.1 The $\alpha$ -Critical Approach |

|   | 3.6 | Calculation of Timing Bounds on Nets  |

|   |     | <b>3.6.1</b> <i>Minimax</i> Approach  |

|   |     | <b>3.6.2</b> Minimax-PERT             |

|   | 3.7 | Experimental Results                  |

|   | 3.8 | Conclusion                            |

| 4 | Tin | ning Driven Floorplanning 65          |

|   | 4.1 | Introduction                          |

|   | 4.2 | Preliminaries                         |

|   | 4.3 | Problem Definition                    |

|   | 4.4 | A Floorplanning Heuristic             |

v

|   |      | 4.4.1 Force Directed Topological Arrangement | 71          |

|---|------|----------------------------------------------|-------------|

|   |      | 4.4.2 Floorplan Sizing                       | 84          |

|   | 4.5  | Timing Verification                          | 99          |

|   | 4.6  | Discussion                                   | 101         |

|   | 4.7  | Experimental Results                         | 103         |

|   | 4.8  | Conclusion                                   | 110         |

| 5 | Con  | clusion 1                                    | 11          |

|   | Bib  | liography 1                                  | 14          |

|   | Vita | ae 1                                         | L <b>21</b> |

----

vi

# List of Tables

•

| 3.1 | Technology data for METAL-1 and METAL-2                      | 36 |

|-----|--------------------------------------------------------------|----|

| 3.2 | Net capacitance statistics.                                  | 43 |

| 3.3 | Results for Example 3.2                                      | 50 |

| 3.4 | Delay bounds computation for Figure 3.6.                     | 60 |

| 3.5 | Test cases statistics.                                       | 61 |

| 3.6 | Number of predicted paths as a function of $\alpha$          | 62 |

| 3.7 | Number of predicted paths for the 16-bit multiplier          | 62 |

| 3.8 | $\alpha^{max}$ values and delay and variance of longest path | 63 |

| 3.9 | Minimax_PERT test results                                    | 63 |

| 4.1 | Results of running Cluster Growth on Example 4.2 |

|-----|--------------------------------------------------|

| 4.2 | Dimensions for blocks in Example 4.3             |

| 4.3 | Results for Example 4.3                          |

| 4.4 | Data from the Traffic Controller                 |

| 4.5 | Data from the Fractional Multiplier              |

| 4.6 | Test cases statistics                            |

| 4.7 | Data from the adder circuit                      |

| 4.8 | Data from the 16-bit parity checker              |

| 4.9 | Data from the 8-bit parity checker               |

.

# List of Figures

.

- -

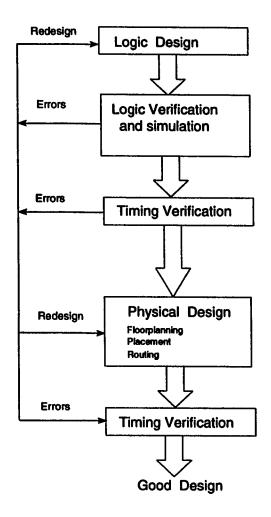

| 1.1 | Classic design process                           |

|-----|--------------------------------------------------|

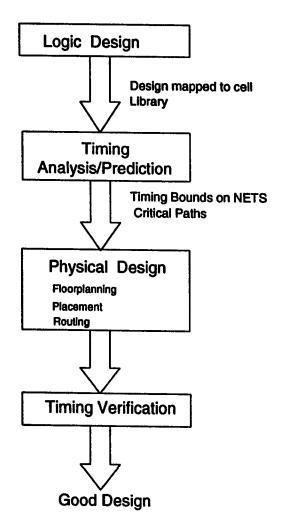

| 1.2 | Timing driven design process                     |

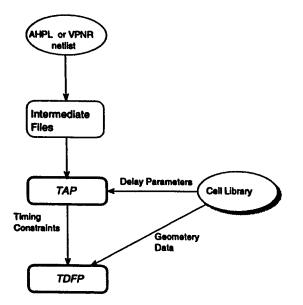

| 1.3 | Overview of the TAP_TDFP system                  |

| 1.4 | An AHPL netlist file                             |

| 1.5 | A VPNR input file                                |

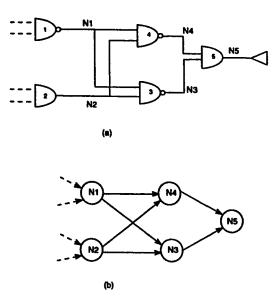

| 3.1 | A circuit example to illustrate the timing model |

| 3.2 | Graph representation of a VLSI circuit           |

| 3.3 | Critical Path Depth-First Trace with Pruning     |

| 3.4 | A circuit example to illustrate DFTP             |

|      |                                                                                                       | х  |

|------|-------------------------------------------------------------------------------------------------------|----|

| 3.5  | Minimax-PERT Algorithm                                                                                | 57 |

| 3.6  | A circuit example to illustrate Minimax-PERT.                                                         | 59 |

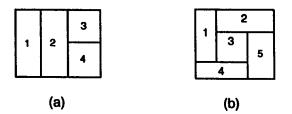

| 4.1  | (a) slicing floorplan; (b) nonslicing floorplan                                                       | 69 |

| 4.2  | Place_Block procedure.                                                                                | 74 |

| 4.3  | Cluster_Growth algorithm description.                                                                 | 75 |

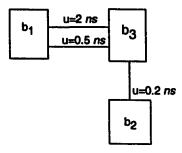

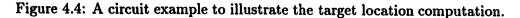

| 4.4  | A circuit example to illustrate the target location computation                                       | 78 |

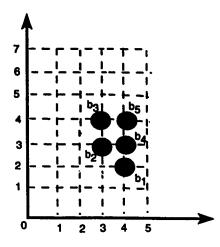

| 4.5  | Target location for $b_3$ : (a) at $(x_3^t, y_3^t)$ ; (b) at $(x_3^c, y_3^c)$ ; (c) at $(x_3, y_3)$ . | 79 |

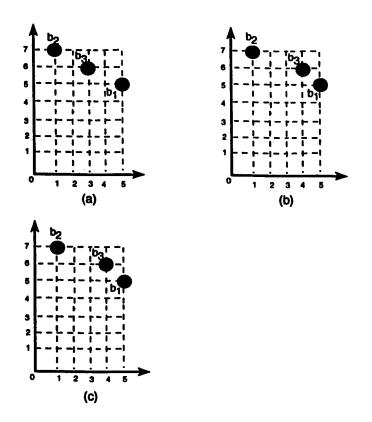

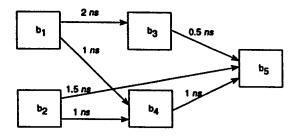

| 4.6  | Circuit for Example 4.2.                                                                              | 83 |

| 4.7  | Force-directed floorplan for Example 4.2.                                                             | 84 |

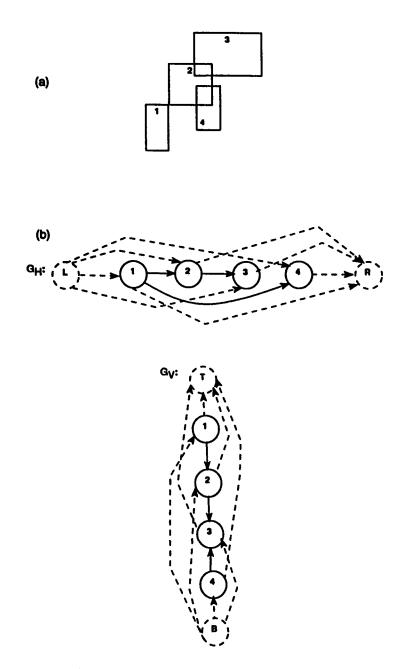

| 4.8  | (a) Illegal floorplan; (b) constraint graphs: $G_H, G_V$                                              | 87 |

| 4.9  | Sufficient_Constraint algorithm.                                                                      | 90 |

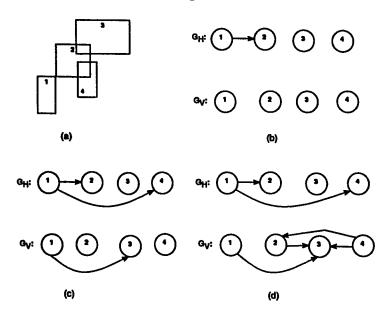

| 4.10 | (a) Overlapping floorplan; (b) edge (1,2) retained; (c) edges (1,4) and                               |    |

|      | (1,3) retained; (d) sufficiently constrained set: $G_H$ , $G_V$                                       | 91 |

| 4.11 | A possible floorplan for Example 4.3.                                                                 | 93 |

٠

•

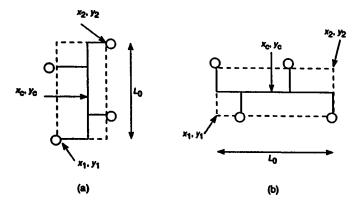

| 4.12 | Approximate Steiner tree. (a) $L_0 = y_2 - y_1$ ; (b) $L_0 = x_2 - x_1$ | 101 |

|------|-------------------------------------------------------------------------|-----|

| 4.13 | Growth in execution time                                                | 102 |

| 4.14 | A 7-block example: (a) topological assignment; (b) after sizing         | 104 |

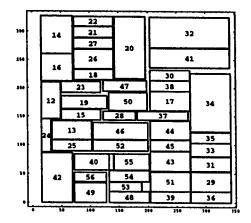

| 4.15 | A floorplan of the Traffic Controller.                                  | 106 |

۲

#### Abstract

Name:Khalid Jawdat Kamel Al-FarraTitle:Timing Driven FloorplanningMajor Field:Computer EngineeringDate of Degree:June 1995

Increase in chip density and decrease of feature size have made the performance of modern VLSI circuits dependent on signal propagation along signal nets rather than the switching delays of the cells. Consequently, physical design should be made timing driven. A timing driven physical design tool requires necessary timing data about the design and a strategy to use this data during physical design. In this work, we address both of these issues. We describe efficient algorithms for the prediction of interconnect delay requirement prior to layout. Next, we present a timing driven floorplanning methodology. Our floorplanning approach has two major stages. The first stage constructs a timing driven topological arrangement using a force directed technique. The second stage is floorplan. The execution time of the floorplanning algorithm grows linearly with the problem size.

> Master of Science Degree King Fahd University of Petroleum and Minerals Dhahran, Saudi Arabia

## خلاصة الرسالية

الإسم : خالد جونت الفرا عنوان الرسالة : خوارزمية تخطيط زمنية التخصص : هندسة الحاسب الآلي تاريخ الرسالة : يونيو ١٩٩٥

لقد أصبحت سرعة انتقال الإشارات الرقمية عبر الموصلات عاملاً اساسياً في تحديد سرعة المعالجة للدواتر عالية التكامل. وحيث أن طول الموصلات يتم تحديده انشاء مرحلة التصميم الفعلي ..فإن هذه المرحلة يجب أن تكون محفزة بسرعة المعالجة المطلوبة. و لكي تتمكن أداة التصميم الفعلي من تحقيق هذا الهدف يجب أن يوفّر لها معلومات دقيقة عن زمنية التصميم و خوارزمية لكيفية استخدام هذه المعلومات. و تسمى ادوات التصميم المحفزة بسرعة المعالجة بالخوارزميات الزمنية. في هذه الرسالة قمنا بعمل خوارزمية للحصول على المعلومات الزمنية اللازمة. و قمنا ايضاً بعمل خوارزمية زمنية زمنية تتعطيط الدوائر عالية التكامل. تتكون خوارزمية اللازمة. و قمنا ايضاً بعمل خوارزمية زمنية المعلومات. في المرحلة التصميم المحفزة بسرعة المعالجة بالخوارزميات الزمنية. في هذه الرسالة قمنا بعمل خرارزمية للحصول على المعلومات الزمنية اللازمة. و قمنا ايضاً بعمل خوارزمية زمنية التخطيط الدوائر عالية التكامل. تتكون خوارزمية التخطيط من مرحلتين. في المرحلة الأولى يتم ترتيب الخلايا المنطقية باستخدام مبدأ توازن القوى الفيزياتية. و يجري تحويل ترتيب الخلايا إلى مخطط صحيح هندسياً في المرحلة الثانية. و قد حصلنا على نتائج ايجابية جدا الثماه استخدام الخوارزمية الجديده في عمل بعض التصاميم .. ووجدنا أن سرعة تنفيذ الخوارزمية تتناسب خطياً مع حجم التصميم.

> درجة الماجستير في العلوم جامعة الملك فهد للبترول و المعادن الظهران – الملكة العربية السعودية يونيو ١٩٩٥

xiii

## Chapter 1

# Introduction

Very large scale integration (VLSI) has made it possible for the semiconductor industry to fabricate an integrated circuit consisting of thousands of components on a single silicon wafer. The VLSI design process spans a wide spectrum of branches in physics, chemistry, electronics and computer science. The complexity of the design process requires breaking it into a number of design steps. The hierarchical decomposition enables the designer to work at any time on a task of manageable complexity.

In most general terms, design can be viewed as a process of successive mappings or transformations of specifications from one abstraction level (or domain) into another. The VLSI design space can be divided into three areas: behavioral (functional), structural, and physical. The behavioral level defines the system outputs in terms of system inputs. The structural level represents the system as a network of logic modules that implements the behavioral level. At the lowest level lies the physical representation. The physical representation gives the required details that can be used by layout synthesis tools to fabricate the desired system.

The complexity of the design process and the variety of applications have lead to different design styles. These design styles can be classified into two general classes [SY94]:

- Full-custom layout.

- Semi-custom layout.

In the *full-custom* approach, the circuit is designed manually by an expert artwork designer. The circuit elements can be placed anywhere on the layout surface. The design cost for this approach is very high because of very long design time (usually years). Thus, only high-volume production can make the manufacturing process profitable. Because of the flexibility in logic and layout design, circuits (e.g., micro-processors) produced by this style can be highly optimized for area and performance.

The *semi-custom* approach constrains the layout elements to some structure in order to reduce the complexity of the design process and consequently the design

time. This reduces the design cost, and makes low-volume production profitable. The popular examples of this design style are gate array, standard cell, and general cell layout styles.

Gate array provides a large two dimensional array of prefabricated transistors on a silicon wafer. Gates, or basic cells, are designed and realized by the manufacturer. The basic cells and their interconnection patterns are kept in a library. All basic cells have equal dimensions. The interconnection of the basic cells is customized to the desired circuit. Routing space in gate array is fixed and limited. The routing regions are called *channels*. Sea-of-gates is a special case of gate array where over the cell routing is allowed and no routing channels are provided.

The *standard cell* layout offers more flexibility. A library of standard cells gives the cell name along with information about its geometry, structure, and delay characteristics. All the cells are of the same height, but with varying widths. The cells are laid out side by side into rows. Routing space is not fixed as in gate array.

The last approach is general cell layout. This style provides maximum flexibility in both logic and layout design. This approach is often referred to as macro-cell, or building block layout style. Macros are permitted to vary in height and width. Consequently, macros with different degrees of sophistication can be implemented. Examples of macros include registers, RAM, ROM, ALU, etc. This approach is similar to the full-custom approach.

The objective of the physical design steps is to map the structural representation of the design into a physical representation that can be used to produce the desired circuit. The major physical design steps are floorplanning, placement and routing. *Floorplanning* is a preparatory step to placement<sup>1</sup>. Usually at this step, it is assumed that the areas and connectivity information of modules are known, while topology of chip and exact dimensions of modules are yet to be defined. Such flexibility represents the designer's freedom in selecting among several possible floorplan configurations. *Placement* is concerned with finding geometric positions for the circuit modules on the layout surface. For placement, the module dimensions, shapes, and pin locations are fixed. Placement is followed by *routing* which interconnects the modules according to the netlist supplied by the structural level.

The feasible solution space for the three steps is very large. If the layout surface is unbounded the solution space is infinite. The floorplanning, placement, and routing problems are NP-Hard problems. By imposing constraints and defining objective functions for the search process, we can reduce the solution space and get superior solutions. However, this transforms the problem to an optimization problem which is much harder. As a result of this complexity, heuristic techniques are used to find sub-optimal solutions that satisfy the stated design objectives and constraints.

<sup>&</sup>lt;sup>1</sup>Floorplanning is sometimes referred to as global or loose placement.

Common objective functions in the layout design problem are chip area, total wire length, routability, timing, or a combination of these.

Once considered to be electrically negligible, interconnects (nets) are becoming a major concern in modern VLSI design because the capacitance and resistance of wires increase rapidly as chip density grows larger and minimum feature size is reduced. In recent years, performance driven layout has become a major issue in VLSI design [DUN84, BUR85, JAC89, YOU90, NAI89, MSL89, BRA90]. For this purpose, designers use various tools, generally called *timing analyzers*, to help them control and improve the temporal properties of circuits before committing them to hardware. The timing analyzer identifies a set of circuit paths called critical paths and possibly a set of critical nets. The physical design step then tries to place the modules belonging to the critical paths and nets in a topological proximity.

In conventional IC design methodology, layout is generated without any knowledge about performance (timing) requirements of the design. Timing verification is invoked after each step. If timing errors are detected, the higher design step(s) is (are) repeated (see Figure 1.1). The timing problems are caused by long interconnects generated by the layout tools. Such philosophy usually results in very unpredictable and expensive iterations of the design process. The lack of timing information on the nets and paths of the design prior to layout, the quality of these information, or the lack of integration between the layout and the timing analysis

Figure 1.1: Classic design process.

steps are major reasons of the iterative nature of this methodology [YOU90].

Due to recent advances in VLSI technology, the interconnect delays have become a major factor in the overall speed performance of the circuit. The need for timing driven layouts is increasing. It is thus necessary to consider the performance issue in the layout process. In other words, the layout steps such as floorplanning, placement etc., have to be made sensitive to the timing requirements.

In this work we adopt a design methodology that considers these issues. In this methodology, the timing analysis step is integrated with the physical design step. The timing analysis step is included after the logic design step where design has already been mapped into a specific cell library. The timing step performs two functions: (i) it computes delay constraints on all interconnects that are consistent with the required clock rate of the design, and (ii) it identifies the most critical paths in the circuit (Figure 1.2). For the timing step we implement algorithms similar to those proposed in [YOU90]. We then use the timing data to implement a timing driven floorplanning algorithm.

## 1.1 Overview of the System

The timing analysis algorithms are embodied in a program called *Timing Analysis/Prediction* (*TAP*). The *Timing Driven Floorplanning* is implemented in a program called *TDFP*. The structure of the *TAP\_TDFP* system is shown in Figure 1.3.

Two input formats are recognized by the system: AHPL [MS86] netlist or VPNR [MCN90] netlist. The AHPL netlist consists of two files: the gate list and the I/O

Figure 1.2: Timing driven design process.

----

Figure 1.3: Overview of the TAP\_TDFP system.

list. Each row in the gate list file corresponds to a single gate. The gate list gives the gate number, gate type, input link and the output link. Using either the input link or the output link along with the I/O list, the connectivity of the circuit can be derived. An example of AHPL netlist is given in Figure 1.4.

The VPNR netlist is of two types: placed and unplaced domains. The placed domain netlist specifies a complete standard-cell placement for the circuit. The netlist consists of a list of rows giving the cells in each row. The unplaced netlist consists of a single row. Figure 1.5 is a sample of an unplaced VPNR netlist. The reader is referred to [MCN90] for details of the VPNR format. Starting from a circuit description in AHPL or VPNR format, the description is compiled through a preprocessor into the TAP intermediate files. The cell's delay characteristics are

| GATE LI                              | ST                                            |                                       |                                      |

|--------------------------------------|-----------------------------------------------|---------------------------------------|--------------------------------------|

| GATE                                 | TYPE                                          | IN-LINK                               | OUT-LINK                             |

| 101                                  | 4018                                          | 0                                     | 2                                    |

| 102                                  | 4018                                          | Ō                                     | 4                                    |

| 103                                  | 4018                                          | 0                                     | 6                                    |

| 104                                  | 4018                                          | 0                                     | 8                                    |

| 107                                  | 4203                                          | 13                                    | 14                                   |

| 105                                  | 4203                                          | 9                                     | 10                                   |

| 106                                  | 4203                                          | 11                                    | 12                                   |

| 108                                  | 4203                                          | 15                                    | 16                                   |

| 109                                  | 4203                                          | 17                                    | 18                                   |

| 110                                  | 4018                                          | 19                                    | 0                                    |

| 111                                  | 4018                                          | 21                                    | 0                                    |

| 112                                  | 4018                                          | 0                                     | 23                                   |

| 113                                  | 4102                                          | 24                                    | <b>2</b> 5                           |

| 114                                  | 4018                                          | 26                                    | 0                                    |

| IOLIST                               |                                               |                                       |                                      |

| LINK                                 | GATE 1                                        | GATE 2                                | NEXT LINK                            |

| 2                                    | 105                                           | 0                                     | 0                                    |

| 4                                    |                                               |                                       |                                      |

| -                                    | 105                                           | 0                                     | 0                                    |

| 6                                    | 105<br>106                                    | 0<br>0                                |                                      |

|                                      |                                               |                                       | 0                                    |

| 6                                    | 106                                           | 0                                     | 0<br>0                               |

| 6<br>8                               | 106<br>106                                    | 0<br>0                                | 0<br>0<br>0                          |

| 6<br>8<br>10                         | 106<br>106<br>107                             | 0<br>0<br>108                         | 0<br>0<br>0<br>0                     |

| 6<br>8<br>10<br>12                   | 106<br>106<br>107<br>107                      | 0<br>0<br>108<br>109                  | 0<br>0<br>0<br>0<br>0                |

| 6<br>8<br>10<br>12<br>14             | 106<br>106<br>107<br>107<br>108               | 0<br>0<br>108<br>109<br>109           | 0<br>0<br>0<br>0<br>0<br>0           |

| 6<br>8<br>10<br>12<br>14<br>16       | 106<br>106<br>107<br>107<br>108<br>110        | 0<br>0<br>108<br>109<br>109<br>0      | 0<br>0<br>0<br>0<br>0<br>0<br>0      |

| 6<br>8<br>10<br>12<br>14<br>16<br>18 | 106<br>106<br>107<br>107<br>108<br>110<br>111 | 0<br>0<br>108<br>109<br>109<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 |

-----

Figure 1.4: An AHPL netlist file.

.

```

domain begin detect lib=scmos swap=0

profile top (0,0) (0,0);

profile bot (0,0) (0,0);

iolist

Seq_in T:(0,100) pintype=pi

Reset T:(0,100) pintype=reset

Phi1H T:(0,100) pintype=clock

Phi2H T:(0,100) pintype=clock

Phil_test T:(0,100) pintype=clock

Out_pls B:(0,100) pintype=po

;

row 1

dsr2s INSI14 (I9,I13,Reset,Phi1H,Phi1_test,Phi2H,I11,I8)

dsr2s INSI16 (I10,I15,Reset,Phi1H,Phi1_test,Phi2H,I12,Out_pls)

ai2s INSI21 (Seq_in,I8,I20)

ils INSI22 (Seq_in,I9)

ils INSI23 (I20,I10)

;

domain end detect

```

Figure 1.5: A VPNR input file.

extracted from the cell library. The TAP program requests the user to specify a clock period for the circuit, and a confidence level for critical path analysis (Chapter 3). The output from the TAP system is a list of timing critical paths sorted on their criticality, and maximal delay bounds for all the nets in the circuit. Additionally, the TAP program generates an efficient simple netlist description for the circuit. This description has been used successfully by a *timing driven genetic placer* [NAS94].

The input to TDFP is a TAP-netlist. The necessary geometry data are extracted from the cell library. The user is requested to specify a desired chip aspect ratio. The output generated by TDFP is a list of the blocks, along with their heights, widths, and positions of their lower-left corners on the layout surface.

## **1.2 Organization of the Thesis**

In this work, we are concerned with two issues: prediction of the timing requirements of a VLSI circuit, and the usage of these predictions to drive the floorplanning step.

Our goal is to tie the physical design stage to the timing analysis step. The timing analysis step performs two tasks:

• Prediction of the most timing critical paths.

• Computation of delay constraints on all signal nets.

This information is used to drive the physical design steps, so that layout will be free from timing related problems. We demonstrate the usage of the timing data in the physical design stage by describing a force-directed timing sensitive floorplanning approach for general cell design style.

In Chapter 2, we review several reported works on the *floorplanning* problem. The issues of critical paths prediction and the derivation of delay constraints on signal nets are discussed in Chapter 3. We describe a new strategy for predicting critical paths using statistical estimations. Next, we discuss a minimax algorithm proposed by Youssef [YOU90] for the derivation of maximal delay bounds on net delays, which are consistent with the path's timing constraints.

In Chapter 4, we present our timing driven floorplanning approach. Our approach consists of two major steps. The first step is concerned with constructing a timing driven topological assignment using a force directed technique. The output from this step is an overlapping floorplan satisfying all timing constraints. The second step is floorplan sizing. This step produces a legal floorplan that satisfies all geometric constraints.

Finally, in Chapter 5, we summarize our work and discuss possible future extensions.

## **1.3 Conclusion**

•

•

In this chapter, a brief introduction of VLSI design process and motivation behind timing driven design is given. An overview of the implemented system is described. Finally, an outline of the thesis is presented.

# Chapter 2

## Literature Review

The intractability of the floorplanning problem has led to a large number of heuristic solution techniques. It is difficult to compare the quality of floorplans generated by these techniques. This is due to the inherent differences in the solution methods, which is brought about by the multi-objective nature of the problem. Several objectives are considered in floorplan design. The traditional objectives include minimizing chip area, minimizing total wire length, ensuring routability, or a combination of these. Recently, circuit performance has become a popular objective. The classical approaches to floorplan design solve the problem in two steps. The first step generates a topological arrangement. The next step is sizing, where actual dimensions of modules, routing area estimation and total floorplan area are computed.

Floorplanning approaches can be classified into two general classes: constructive and iterative. Constructive algorithms adopt a cluster-growth strategy to build a complete solution. Some constructive algorithms require a partial placement as a starting condition. Examples of constructive approaches include dual graph method [LAI88], partitioning/slicing [LAP86], mathematical programming, and force directed methods. Iterative techniques on the other hand operate on complete solution and try to improve the quality of the floorplan. For iterative algorithms, the initial solution is generated randomly or by a constructive algorithm. The most widely used iterative improvement technique is Simulated Annealing (SA).

Another possible classification for floorplanning techniques is *deterministic* techniques and *probabilistic* techniques. Constructive algorithms that adopt an equation solving method or based on connectivity information are deterministic because they will always produce the same solution. Iterative techniques are usually probabilistic and generate a different solution for each run.

### 2.1 Floorplanning Approaches

There are many methods for solving the floorplanning problem. Among them are force-directed, simulated annealing, dual graph formulation and analytical techniques.

A common aspect of force-directed algorithms is the method of computing the location where a module should be positioned. This method is analogous to the computation of the *equilibrium location* (the *center of gravity*) problem in physics. The equilibrium location corresponds to a minimum energy state for the module.

Starting with Fisk et. al., 1967 [FCW67], many force-directed techniques are in existence today. There are two possible implementations of this approach: constructive and iterative. The constructive method adopts an equation solving method. The coordinates of each module are treated as variables. The equations are then solved simultaneously to get a minimum-energy state configuration. Iterative forcedirected relaxation techniques try to improve the quality of an existing solution. Two strategies are used. The first one tries to move each module to its equilibrium location or to the nearest possible if the target location is occupied. The second strategy randomly selects a pair of modules and interchanges their locations. If the interchange results in a cost reduction (usually wire length) the move is accepted, otherwise it is rejected [HWA76]. The force-directed approach adopts the point model for modeling the modules. In other words, the size and shape of modules are ignored in the computation of equilibrium location of each module. This makes it unsuitable for building block layout due to the irregular dimensions of the blocks. On the other hand, this technique works well for gate array and standard-cell layouts, where points in the plane can be easily mapped to the basic cells in each row of the layout surface. The force-directed approach is best used as an initial solution generator because of its superior execution speed and global view of the overall circuit connectivity. Further more, the solutions generated by force-directed techniques are not restricted to slicing floorplans [WL86](see Section 4.2).

The *simulated annealing* (SA) algorithm gets its name from the annealing process in metals. In this process, a clean crystal structure of a certain metal can be restored by heating it to a very high temperature, then cooling it very slowly. The first attempts of applying SA to VLSI-CAD problems were reported in [KGV83, JG83]. Since then, several works have used SA to solve the floorplanning problem [WL86, OG84, WT89].

The basic idea of SA is to perturb the current solution and to accept all perturbations that result in a reduction in cost. Moves that cause the cost to increase are accepted with a probability that decreases with increasing cost and temperature values. This prevents the algorithm from getting trapped at a local minimum. This process is repeated until a given stopping criterion is met. The quality of the solutions produced by SA is excellent. A major disadvantage of SA is that it is computing intensive.

In the *dual graph* technique a layout structure graph is first transformed into a planar graph by deleting a minimum number of edges and/or adding crossover vertices. Next, an optimal rectangular dual is found for the planar graph. The faces of the dual correspond to modules and the edges of the dual represent module adjacencies. It is not clear how this approach can be modified to take into account the various constraints imposed by practical applications. More details about this technique can be found in [SY94].

Floorplanning is an optimization problem. Thus, analytical techniques can be used to solve the problem. A feasible floorplan is formulated as a set of mathematical equations. Then, mathematical programming techniques are used to solve these equations. This approach is confronted with two main problems. The first problem is the number of equations describing a feasible floorplan is very large resulting in a very large mathematical program. To tackle this problem, a divide and conquer strategy is adopted. The second problem is the nonlinearity of the floorplanning problem leading to a nonlinear program. To overcome this problem, the nonlinear program is linearized using approximation techniques. However, approximation will impact the quality of the solution. A survey of the application of analytical techniques to placement is given in [SM91]. The reader is referred to Chapter 3 of [SY94] for a detailed description of floorplanning.

### 2.2 Work on Floorplanning

In this section, we review several other reported works on the floorplanning problem.

In [BRA90], a floorplanning algorithm and a global router that uses a sequence of gradient descent operations based on force-directed functions were presented. The best floorplan is selected and simulated annealing is then applied to remove cell overlaps. Circuit timing is considered among other objectives of the floorplan. The timing constraints are specified as critical net/path weights, maximum path length, and maximum net wire length.

In [WIM89], a branch and bound algorithm for selecting optimal aspect ratios of building blocks in non-slicing floorplans was proposed. Each block is assigned to a level of the enumeration tree. Each node in the tree corresponds to a partial floorplan and each "root to leaf" path is a complete floorplan.

In [DON89], an iterative improvement floorplan procedure using constrained graphs was described. The procedure has two steps. In the first step, the dimensions of all the blocks are iteratively computed based on the length of the longest path passing through the block in the constraint graph. In the second step, the blocks are placed according to the imposed constraints. If the resulting floorplan has overlaps additional constraints are introduced and the process is repeated. Such an iteration is repeated until an acceptable solution is achieved.

In [SUT90], a general floorplan design algorithm based on a linear mixed integer programming model was proposed. The objective is to minimize the overall area of the rectangle enclosing all the basic rectangles. Successive augmentation is used in order to avoid very large mathematical programs. Successive augmentation consists of constructing a complete floorplan by optimally adding a new set of modules to a partial floorplan until all modules are positioned. Each basic rectangle is inflated by an estimate of the routing space of the corresponding module.

In [VIJ91], an approach based on constraint reduction and block reshaping to find floorplans with optimal areas was employed. Two directed acyclic graphs  $(G_H, G_V)$ are used to represent the left-right and bottom-top relations between blocks. A complete topological constraint set is derived from a topological arrangement. A constraint set is complete if it contains at least one constraint for each pair of blocks. Then, redundant constraints (i.e., edges) are removed from the critical paths in either  $G_H$  or  $G_V$ . A constraint is redundant if it is present in both  $G_H$  and  $G_V$ . Flexible blocks are then reshaped in order to reduce floorplan area. For large designs, the derivation of a complete constraint set and its optimization by removing redundant constraints may require enormous amount of computation time.

In [YIN89], an analytical technique for floorplanning rectangular blocks is described where the objective is the minimization of the total interconnect length and total floorplan area. The approach consists of two phases. The first phase is a relative placement based on a potential energy model to layout the blocks such that interconnects and size of blocks requirements are satisfied. The second phase is a spacing phase to remove overlaps between blocks.

In [LA188], a graph theoretic approach to construct rectangular floorplans was presented. The key point in this work was the reduction of the rectangular dualization problem to a matching problem in bipartite graphs. The resulting floorplan was then optimized using a sequence of rectangular dual transformations while preserving the adjacency requirements implied by the original structure graph.

In [DAI87], a constructive hierarchical floorplanning approach combined with global routing was proposed. The approach consists of a clustering step based on the connectivity information. This is followed by a mapping of the clusters onto floorplan templates. Global routing is considered as a part of the floorplanning procedure. Each resulting floorplan is evaluated against an area goal and an I/O pad goal.

LaPotin et. al., [LAP86] proposed a floorplanning approach which combines min-

cut technique and slicing in order to reduce the complexity of the routing problem. Multiple floorplans can be obtained by traversing the slicing tree. Floorplans are evaluated in terms of area and overall wire length using a global router. Module dimensions are derived based on the global routing area.

In [UED85], a semi-automatic VLSI chip floorplanning algorithm was proposed. The algorithm has two stages: initial block placement, and block packing process. The target for the initial placement is to place highly connected blocks in close proximity, whereas weakly connected blocks are placed far from each other. The initial placement is generated by an attractive and repulsive force method (AR method). In the block packing process, overlaps between blocks or blocks and chip boundary are removed by gradually shifting and reshaping blocks with chip boundary shrinking. The block packing process is repeated until an acceptable layout is obtained. A disadvantage of the AR method is that it places weakly connected blocks far from each other. This may not be suitable for timing driven floorplanning because those weakly connected blocks could be part of a timing critical path; if the blocks are far apart, this path will most likely have a timing problem in the final layout.

### 2.3 Work on Timing Driven Layout

Numerous attempts have been reported on timing driven physical design. These attempts can be classified into three general approaches.

One approach to correct timing errors is to modify some of the logic on the critical paths [MIC86, KIC87].

Another approach relies on transistor re-sizing to reduce delays along the slow paths [JOU87, MIC86].

The third approach avoids any logic modification by imposing delay constraints on the interconnects and paths of the design. Then, the objective for the physical design step is to satisfy these constraints. The possibility of increasing the clock speed of a layout system by 5%-30% without making changes to the logic design makes this approach superior to the other two approaches. Representative works of this approach are reported in [DUN84, HAU87, NAI89, YOU92, SRI92, SUT93]. Our work adopts this approach.

Timing analysis is path oriented as opposed to layout tools which are net oriented. This suggests two approaches for timing driven design: (1) path oriented approach, and (2) net oriented approach. The path oriented approach predicts a set of paths called *critical paths*. This set is then used by the physical design step. On the other hand, the net oriented approach computes delay constraints for each net based on paths slacks [YOU90, HAU87]. Another net oriented approach assigns a level of criticality to each net [BUR85, DUN84]. A disadvantage of the latter approach is that minimizing the length of the critical nets often causes other nets to become excessively long.

In [DUN84], nets were assigned weights based on a delay analysis performed first with the assumption that net delays are function of their fanouts. The paths with maximum delays are considered as critical and nets covered by these paths are the critical nets. Critical nets are given higher weights which are used to bias the placement and routing steps. After a first layout, actual routing data are passed back to the timing analysis step. This process is repeated until the layout has no failing paths for the desired working clock.

In [BUR85], a preliminary timing analysis prior to layout is performed based on the assumption that all interconnects are equal to an average length. A net-slack for each net is defined to be the slack of the worst path traversing this net divided by the number of nets along that path. The computed net slacks are used to categorize nets into three classes: critical, admissible and regular. The value of the net slack determines its degree of criticality.

In [HAU87], delay bounds on all the nets are computed using a procedure called

Zero Slack Algorithm (ZSA). The computed bounds are transformed into length constraints on the nets and supplied to the physical design steps. Penalties (0, 1, 2) are raised when violations of these constraints occur. Higher penalties imply more attention is given to circuit timing.

In [JAC89], linear programming has been invoked at each stage of recursive partitioning to track path constraints dynamically during placement. Constraints on the physical and timing characteristics of the design are considered in formulating the linear program. Timing constraints on the paths are transformed into constraints on cell locations. Net length estimation is performed using the half-perimeter method. This method for net length estimation is very optimistic, which will hide all timing problems that the layout might have. Furthermore, solving a linear program at each stage slows down the system significantly.

In [FRA92], an algorithm, called the *limit-bumping* algorithm, for computing upper limits on interconnect delays is proposed. This algorithm is similar to the *lterative-Minimax* approach in [YOU90]. These upper limits are used to improve the layout performance. This is achieved by iteratively decrementing the upper limits on connection delays without violating the lower limits. Frankle shows the necessity for having lower limits on connection delays in order to get realistic upper limits; however, the derivation of such lower limits is not clear. The timing data has been used by a timing driven FPGA router. An average of 14% improvement

in system clock periods has been reported.

### 2.4 Conclusion

•

-----

In this chapter, we reviewed several approaches to floorplanning as reported in the literature. A classification of solution methods was given. Several timing driven design approaches were reviewed.

# Chapter 3

.

# **Generation of Timing Constraints**

### 3.1 Introduction

With advances in integrated electronics technology, the interconnect delays have become a significant factor in determining the timing characteristics. This situation makes it almost impossible to verify the required clock speed at the logic design step. It is no longer the case that timing verification can be done prior to physical design, and physical design itself should be governed by timing requirements. Timing driven layout has become a popular topic among researchers in the CAD area.

In order to produce layouts optimized for timing, the timing analysis/ prediction

step should guide the layout tool by supplying necessary and accurate information about the timing aspects of the design. This information may be supplied as maximal constraints on interconnect delays, or a list of the most critical paths in the design, or both.

In this chapter, we present a new approach to predict timing critical paths in a given VLSI design, which is a variation of one of the approaches reported in [YOU90]. The predicted critical paths' information has been successfully used by a *timing driven genetic* placer for standard cell design style. The critical paths enumerated after placement were a proper subset of the predicted paths. For details of this layout system, the reader is referred to [NAS94]. Next, the implementation of an algorithm due to [YOU90] for computing delay upper bounds on all the nets will be presented. The net bounds are functions of the nets' electrical characteristics.

The rest of the chapter is organized as follows. In Section 3.2 we present some basic timing analysis concepts. Section 3.3 discusses the delay model adopted in this work. In Sections 3.4 to 3.6, we focus on the development of timing information about the design at hand. Experimental results are presented in Section 3.7. We conclude in Section 3.8.

### **3.2 Timing Analysis Concepts**

Timing simulation<sup>1</sup> and timing analysis are two popular approaches to verify the timing behavior of a digital circuit. By exercising the circuit for a large set of input signals, the simulator checks the functional and timing behavior of the design. Timing analysis, on the other hand, ignores the logic properties of the circuit elements and checks only the timing behavior of the circuit. This fact makes timing analysis very time efficient compared to simulation. Ignoring the functionality of the circuit elements is however, responsible for the main difficulty in timing analysis: the *false path problem*. This problem can be eliminated by using a path sensitization criterion to determine whether a path is sensitizable or not [CD93].

Nowadays, timing analysis is replacing simulation for VLSI circuits. Simulation is used only for testing the functionality of the circuit.

Timing analysis tools can be classified into two classes: transistor/switch level analyzers, and gate/macro level analyzers. Switch level analysis is usually more accurate than gate level analysis; however, it is suitable only after physical design (placement and routing) has been completed. Switch level analyzers are very demanding in terms of computing resources. Gate level analysis can be done before or after physical design. Post-layout gate level analysis includes interconnect delay

<sup>&</sup>lt;sup>1</sup>Simulation is sometimes referred to as dynamic timing analysis.

in the verification process. The accuracy of gate level analysis is contingent on the quality of the gate (also block, or cell) delay model. In this work, we perform timing analysis at the cell level.

In general, timing analysis of VLSI designs is concerned with checking for long and short path problems. A *path* is an alternating sequence of circuit elements and signal nets. The first element of the path is called the *source*, and the last element is the *sink*. Input pads and outputs of storage elements are sources. Output pads and input pins of storage elements are sinks. In this work, storage elements are assumed to be *flipflops*. Both the source and sink of a path are controlled by the same clock.

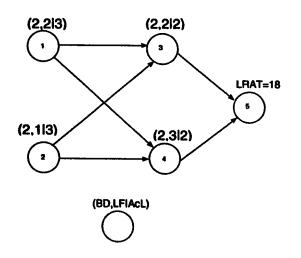

#### **3.2.1 Long Path Problem**

The long-path slack of a path  $\pi$  is defined as

$$SLACK_{\pi} = LRAT_{\pi} - T_{\pi} \tag{3.1}$$

where  $LRAT_{\pi}$  and  $T_{\pi}$  are the "latest required arrival time" and the "actual arrival time" of the signal at the path sink, respectively. A design has a long path problem if for some path, the long-path slack is negative. A negative slack indicates that the signal will fail to propagate through the path within the required time. For flipflops,  $LRAT_{\pi}$  is given by

$$LRAT_{\pi} = CP - T_{cs} - T_{stp} \tag{3.2}$$

where,

CP is the clock period in nanoseconds,

$T_{cs}$  is the maximum clock skew, and

$T_{stp}$  is the setup time at the path sink.

#### 3.2.2 Short Path Problem

The short-path slack of a path  $\pi$  is defined as

$$SLACK_{\pi} = ERAT_{\pi} - T_{\pi} \tag{3.3}$$

where  $ERAT_{\pi}$  is the earliest required arrival time.

A design is said to have a short path problem if  $SLACK_{\pi}$  is positive. A positive short slack indicates that the signal is arriving earlier than what is required and hence will cause a premature gating. For flipflops,  $ERAT_{\pi}$  is given by,

$$ERAT_{\pi} = T_{cs} + T_{hold} \tag{3.4}$$

where,

$T_{hold}$  is the hold time.

Now the challenge for performance driven layout tools is to produce designs such that the total path delay for any path is greater than its earliest required arrival time and less than its latest required arrival time. While short path problems can be detected and corrected during logic design, long path problems are most difficult to avoid. The maximum clock period for a given circuit is determined by the total delay of its longest path. In this thesis, we concentrate on the long path problem and ignore the short path problem. Short paths are easier to eliminate and are less likely to occur in VLSI designs.

For the timing analysis/predictions to be of any value, a suitable delay model should be adopted. The delay model must accurately abstract the essential electrical properties of the circuit elements.

### **3.3 Delay Model**

Timing analysis at any level strongly depends on the *delay model* used to abstract the timing behavior of circuit elements. The model should accurately illustrate the temporal properties of the components of the design. Approximations should be avoided as much as possible as this will dramatically affect the quality of the analysis and hence the quality of the final layout.

A suitable delay model should consider the following essential characteristics:

• The switching delay of a cell consists of two components: the base (intrinsic)

delay of the cell and the loading delay.

- Unateness (polarity) information. Some cells invert the incoming data signal (e.g., NAND); others do not (e.g., AND).

- Differences between rising and falling delays can be order of magnitude apart.

In this work, a linear cell delay model which considers these characteristics has been adopted. With this model, the time needed to charge the capacitances at the loading pins of a given net is the same. Using this model, the total switching delay of a given cell v is given by

$$CD_v = BD_v + LF_v \times AcL_v \tag{3.5}$$

where,

$BD_v$  is the base (intrinsic) delay of cell v in nanoseconds.

$LF_v$  is the load factor in Kilo $\Omega$ s. It is the resistance as seen at the cell output pin. AcL<sub>v</sub> is the input capacitance on the loading pins.

For ease of explanation, the unateness of cells as well as differences between rising and falling delays are ignored (but not in the actual calculations of the *Timing Analysis Program (TAP)* system).

Using the lumped RC model, the total delay seen by the output pin of cell v is

expressed as follows:

$$TD_v = CD_v + ID_v \tag{3.6}$$

where,

.

$ID_v$  is the interconnect delay of the net driven by cell v output pin, and is expressed as follows,

$$ID_{v} = LF_{v} \times C_{v} + R_{v} \times (AcL_{v} + C_{v})$$

$$(3.7)$$

where,

$C_v$  is the total interconnect capacitance (area + fringe) of the net driven by cell v output pin.

$R_v$  is the total interconnect resistance of the net driven by cell v output pin.

Based on this delay model, the interconnect delay is a function of three parameters: the load factor of the driving cell which is layout independent, the interconnect capacitance,  $C_v$ , which is layout dependent, and the interconnect resistance which is also layout dependent. As will be demonstrated with an example, for metallic wires the contribution of the resistance parameter to the interconnect delay is negligible compared to the capacitance parameter. In most timing analysis tools, when nets are included in the verification process, only their capacitive effect is considered while their resistive effect is ignored, or at best lumped with the estimated resistance of the driver.

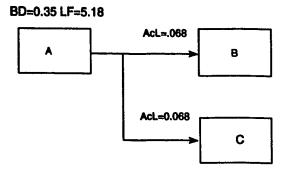

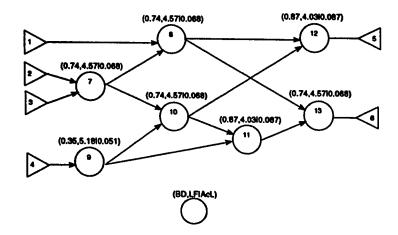

Figure 3.1: A circuit example to illustrate the timing model.

| METAL | Sheet_Resistance<br>Ω/□ | Area_Capacitance $10^{-4} pF/\mu^2$ | $Fringe\_Capacitance$<br>$10^{-4}pF/\mu$ |

|-------|-------------------------|-------------------------------------|------------------------------------------|

| 1     | 0.06                    | 0.26                                | 0.82                                     |

| 2     | 0.033                   | 0.15                                | 0.85                                     |

Table 3.1: Technology data for METAL-1 and METAL-2.

**Example 3.1** Consider the circuit depicted in Figure 3.1 where cell A is driving cells B and C. The switching delay of A is given by  $0.35+5.18 \times (0.068+0.068) = 1.054ns$ .

To compute the interconnect delay for the net in Figure 3.1, assume that the vertical connection is in METAL-1 and its height and width are  $1000\mu$ ,  $3\mu$  respectively. The horizontal connection is implemented in METAL-2 with  $1000\mu$  height and  $3\mu$ width. Table 3.1 gives the worst case values of sheet resistance and capacitance (area and fringe) for METAL-1 and METAL-2 as provided by Orbit Semiconductor [Orb92]. The interconnect capacitance consists of two components: the area (surface) and the fringe capacitances. Let  $C_{M1}$  be the interconnect capacitance due to METAL-1 and  $C_{M2}$  be the interconnect capacitance for METAL-2. Then, using the technology data in Table 3.1 and the dimensions for METAL-1 and METAL-2 given above,  $C_{M1}$  is computed as follows:

$$C_{M1}$$

= area\_capacitance + fringe\_capacitance

= 1000 × 3 × 0.26 × 10<sup>-4</sup> + 2 × (1000 + 3) × 0.82 × 10<sup>-4</sup>

= 0.24249pF

Similarly, we get  $C_{M2} = 0.21551 \, pF$ . The total interconnect capacitance is  $C_{int} = C_{M1} + C_{M2} = 0.458 \, pF$ .

The total resistance is given by

.

$$R_{int} = R_{M1} + R_{M2}$$

= 0.06 ×  $\frac{1000}{3}$  + .033 ×  $\frac{1000}{3}$

= 0.033K $\Omega$

$ID_A$ , the total interconnect delay seen by cell A output pin is therefore,

$$ID_A = LF_A \times C_{int} + R_{int} \times (AcL_A + C_{int})$$

= 5.18 × 0.458 + 0.033 × (0.136 + 0.458)

= 2.392 ns

Observe that the contribution of the delay due to resistance  $R_{int}$  is only 0.0196 ns. Thus, interconnect delay is dominated by its capacitance. This value of  $ID_A$  is more than double the delay seen by the signal when the interconnect delay is ignored (1.054 ns). These values are for  $2\mu$  technology. This ratio of interconnect delay to cell delay is expected to increase as feature size continues to decrease.

In the subsequent discussions, we shall ignore the resistance effect in interconnect delay computations. Thus, Equation 3.7 can be simplified as,

$$ID_v = LF_v \times C_v \tag{3.8}$$

A timing driven physical design tool expects necessary timing information. This information may consist of either or both of the following: (i) a list of the most critical paths, (ii) timing constraints on all the nets. Before we describe the algorithms used to derive such information, we shall first describe a graph model for representing a VLSI circuit.

#### 3.4 Graph Model

The netlist information is transformed into an acyclic directed graph G = (V, E), where V is the set of vertices representing the signal nets, and E is the set of edges representing adjacency relations between signal nets. Vertices with zero in-degree are called *source vertices* (e.g., input pads, output pins of flipflops), and vertices with zero out-degree are *sink vertices* (e.g., output pads, input pins of flipflops). All other vertices are called the *internal vertices*. We shall denote the source vertex set, the sink vertex set, and the internal vertex set by  $V_s$ ,  $V_t$ , and  $V_n$ , respectively. We shall use the symbol  $\pi$  to refer to a path in G. A path is a sequence of vertices. A path is a complete path if it starts at a source vertex and terminates at a sink vertex, otherwise it is a partial path. Figure 3.2 illustrates this graph representation. The

Figure 3.2: Graph representation of a VLSI circuit.

timing information related to the logic cells (i.e., *BD*, *LF*, *AcL*) are stored in the *net-vertices*. Therefore, we do not need to include the logic cell in the graph model. This will significantly reduce the memory space required by the model.

### **3.5** Critical Path(s) Prediction

Since the total number of paths in a VLSI design may grow exponentially with the size of the design, it is impractical to enumerate and monitor every path in the circuit. However, usually a small subset of these paths are timing critical. A path  $\pi$  is critical if its total delay,  $T_{\pi}$ , is very close to its latest required arrival time  $LRAT_{\pi}$ . If  $T_{\pi}$  exceeds  $LRAT_{\pi}$ , path  $\pi$  becomes a long path. The task of the timing tool is to predict those critical paths. The accuracy of this prediction has a direct impact on the temporal performance of the final layout.

One approach to path prediction is to report the most critical path in the design. This approach is also referred to as the *Block Oriented Approach*. Representative examples of this approach are reported in [HIT82, KIRK66]. Reporting the most critical path is not sufficient to correct/prevent timing errors for the whole layout. The second approach reports all the paths which are greater than or less than a given *threshold*. A variation of this technique is to report the K most critical paths [YEN89]. In these approaches the criticality of a given path is measured based on the **path slack**. The smaller the slack, the more critical the path is. For very dense designs, the slack metric may not lead to a good prediction.

The third approach is based on the notion of *categorization* [YOU90]. In this approach, a score is computed for each enumerated path. The score is a function

of parameters that are correlated with the total path delay. Examples of these parameters include: load factors, number of nets on the path, slack, etc. The K paths with worst scores are the K most critical. As in the second approach K could be fixed or a function of a given *threshold*.

For path enumeration, all the above mentioned strategies are based on a depth first search (DFS) with/without pruning, breadth first search (BFS), or PERTlike trace [KIRK66]. The time complexity of these algorithms is proportional to the reported number of paths. The path enumeration phase is always preceded by a graph construction phase. Next, we present a new strategy for critical path prediction.

#### 3.5.1 The $\alpha$ -Critical Approach

As stated earlier, for VLSI designs, the interconnect delay is a major part of the overall path delay. It is then of prime importance, for pre-layout timing analysis, to predict the interconnect delay requirements.

Youssef [YOU90] experimented with the *linear regression* approach to predict interconnect delays at the net level as well as at the path level. In *net-level* point prediction, data about delays of individual nets were collected and used to build a regressional model. The model is then used to predict the response for new cases. On the other hand, in *path-level* prediction, data about total path's interconnect delay along with other path related parameters (e.g., number of nets on the path, sum of load factors, etc.,) are used to build the predictor (model). The following lines are extracted from [YOU90]:

regressional approaches to point prediction of the interconnect delay of paths, and especially of nets, for the purpose of predicting before layout all paths with tight timing requirements, do not produce desirable results.

The deficiency of this approach is due to the low prediction power (i.e., large prediction errors) of the model. The situation is not as bad as it seems. Net-level prediction can still provide the desired accuracy. That depends on the design size, design density, and the variability in net length compared to the overall path interconnection length. We wish to have the *variances* on net lengths much smaller than the total path interconnect length. The  $\alpha$ -critical approach is a variation of the above mentioned approach. A description of this approach follows.

The total path delay consists of two components: the total switching delays of logic cells which is known prior to layout and the total interconnect delay which is unknown. As demonstrated in Example 3.1, the interconnect capacitance is a key element in the total interconnect delay. The average and standard deviation of net length for different types of nets (2-pin, 3-pin, ..., k-pin) are collected from past

designs of similar complexity. These are transformed into interconnect capacitances. These statistics are shown in Table 3.2. Nets are classified according to the number of pins they are connecting. For example, a 2-pin net has an average capacitance of  $0.0496613614 \, pF$ , and a standard deviation of  $0.0381922414 \, pF$ .

| Pins | Mean $(pF)$  | Standard Deviation $(p\bar{F})$ |

|------|--------------|---------------------------------|

| 2    | 0.0496613614 | 0.0381922414                    |

| 3    | 0.0642885151 | 0.0269860004                    |

| 4    | 0.1045077916 | 0.0474687684                    |

| 5    | 0.1239954827 | 0.0564270349                    |

| 6    | 0.1325196250 | 0.0574357545                    |

| 7    | 0.1486822222 | 0.0440815179                    |

Table 3.2: Net capacitance statistics.

Let  $\pi = \{v_1, v_2, \dots, v_k\}$  be a path in the circuit graph, where  $v_1$  is the source and  $v_k$  is the sink. The total delay on  $\pi$  is given by,

$$T_{\pi} = \sum_{i=1}^{k-1} (CD_{v_i} + ID_{v_i})$$

(3.9)

where,

$CD_{v_i}$  is the switching delay of net vertex  $v_i$  as defined by Equation 3.5, and

$ID_{v_i}$  is the interconnect delay of net  $v_i$  as defined by Equation 3.8.

But,  $C_{v_i}$ , the total interconnect capacitance of net  $v_i$ , in Equation 3.8 is unknown prior to layout because it is a function of the net length. Therefore, we characterize each net vertex v by two elements: 1. an average capacitance  $\overline{c_v}$  , and

2. a standard deviation  $s_v$ .

•

٠

The expected delay on net v,  $\overline{ID_v}$ , is computed as,

$$\overline{ID_v} = LF_v \times \overline{c_v} \tag{3.10}$$

The delay variance on net v is computed as

$$S_v^2 = LF_v^2 \times s_v^2 \tag{3.11}$$

Assume that the nets are statistically independent. Thus the expected delay on any path  $\pi$  can be expressed as,

$$T_{\pi} = \sum_{i=1}^{k-1} (BD_{v_i} + LF_{v_i} \times (AcL_{v_i} + \overline{c_v}))$$

(3.12)

The delay variance on path  $\pi$  is defined as the sum of the delay variances of its nets. Using the already introduced notation, the delay variance of path  $\pi$  is expressed as follows,

$$S_{\pi}^{2} = \sum_{i=1}^{k-1} S_{v_{i}}^{2}$$

(3.13)

Let  $T_{max}$  be the expected delay of the longest path in the circuit.  $T_{max}$  can be expressed as follows,

$$T_{max} = \max_{\pi \in \Pi} (T_{\pi}) \tag{3.14}$$

where  $\Pi$  is the set of all paths in the circuit graph G.

**Definition 1** A path  $\pi$  is  $\alpha$ -critical iff:

$$T_{\pi} + \alpha \sqrt{S_{\pi}^2} \ge T_{max} \tag{3.15}$$

The parameter  $\alpha$  (interpreted as a confidence level) is a user supplied input.  $T_{\pi} + \alpha \sqrt{S_{\pi}^2}$  means that we are  $\alpha \sqrt{S_{\pi}^2} ns$  confident that path  $\pi$  is critical. The higher  $\alpha$  is, the larger the number of reported paths will be, and the higher is the probability of capturing all the critical paths. Reasonable values of  $\alpha \sqrt{S_{\pi}^2}$  are  $\leq 4 ns$ .

Lemma 1 The confidence level that will cause full path enumeration is given by,

$$\alpha_{max} = \frac{T_{max} - T_{min}}{\sqrt{S_{min}^2}} \tag{3.16}$$

where  $T_{min}$  is the delay of the path with minimum  $T_{\pi}$  and  $S_{min}^2$  is its delay variance.

The algorithm used to extract paths according to Definition 1 is a variation of the algorithm in [AS85]. Figure 3.3 gives a formal description of this algorithm. We call this algorithm *Depth\_First\_Trace\_with\_Pruning* (*DFTP*). An informal description of this algorithm follows.

Let  $\pi = \{s, v_1, v_2, \dots, v_k, v\}$  be a partial path starting at source s and terminating at v;  $T_{\pi}$  and  $S_{\pi}^2$  are the expected delay and variance along that partial path. When

#### ALGORITHM DEPTH\_FIRST\_TRACE\_WITH\_PRUNING NOTATION

$\Gamma(v)$  : all successors of vertex v

```

T_{max} : delay of longest path

```

: delay of path  $\pi$  (i.e.  $\sum t_v$ )  $T_{\pi}$

$MDS_v$ : Maximum delay to sink of vertex v

$MVS_v$ : Maximum variance to sink of vertex v

- : delay of v including estimated interconnect capacitance tv

- $S^2_{\pi}$  $S^2_{v}$ : Variance of path  $\pi$

- : Variance of the net driven by cell v

```

INITIALIZE

```

```

FOREACH v \in (V_s \cup V_n)

COMPUTE S_v^2 = LF_v^2 \times s_v^2;

ENDFOREACH

GENERAL STEP DFTP

BEGIN

step 1: Backward Trace

1

2

FOREACH v \in (V_n \cup V_s) DO

3

MDS_v \leftarrow t_v + \max_{u \in \Gamma(v)}(MDS_u);

MVS_v \leftarrow S_v^2 + \max_{u \in \Gamma(v)}(MVS_u);

4

5

ENDFOREACH

6

step 2: Forward Trace

7

FOREACH v \in V_{s}

8

PUSH(v);

9

ENDFOREACH

10 step3: Path Trace

11

\pi \leftarrow []; K \leftarrow 0;

12

WHILE (stack is not EMPTY) DO

13

BEGIN

14

v \leftarrow \text{TOP(stack)};

15

IF (v \in V_t) THEN

16

BEGIN

17

SavePath([\pi!, v]); K \leftarrow K + 1;

18

POP(stack);

19

END

```

| 20             | ELSEIF (v is mai                 | wed) THEN                                                                              |

|----------------|----------------------------------|----------------------------------------------------------------------------------------|

| 20<br>21       | BEGIN                            | acu) illein                                                                            |

| 22             | DEGIN                            | POP(stack);                                                                            |

| 23             |                                  | REMOVE v from $\pi$ ;                                                                  |

| 24             |                                  | $T_{\pi} \leftarrow T_{\pi} - t_{\nu};$                                                |

| 24             |                                  | $S_{\tau}^{2} \leftarrow S_{\tau}^{2} - S_{\tau}^{2}$                                  |

| 25             | END                              | $D_{\pi} \leftarrow D_{\pi} = D_{\psi},$                                               |

| 26             |                                  | $(T_{\pi} + MDS_{v} + \alpha \times \sqrt{(S_{\pi}^{2} + MVS_{v})} \ge T_{max})$ THEN  |

| 20<br>27       | ELSER                            | $\frac{(I_{\pi} + MDS_{v} + C \times V(S_{\pi} + MVS_{v}) \ge I_{max})}{\text{BEGIN}}$ |

| 28             |                                  |                                                                                        |

| 20<br>29       |                                  | MARK(v);                                                                               |

| 29<br>30       |                                  | FOREACH $u \in \Gamma(v)$ DO                                                           |