# Component Selection and Pipelining using Stochastic Evolution

by

#### Mohammad Farook

A Thesis Presented to the

FACULTY OF THE COLLEGE OF GRADUATE STUDIES

KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

**MASTER OF SCIENCE**

In

**COMPUTER SCIENCE**

June, 1996

**INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI

films the text directly from the original or copy submitted. Thus, some

thesis and dissertation copies are in typewriter face, while others may be

from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the

copy submitted. Broken or indistinct print, colored or poor quality

illustrations and photographs, print bleedthrough, substandard margins,

and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete

manuscript and there are missing pages, these will be noted. Also, if

unauthorized copyright material had to be removed, a note will indicate

the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by

sectioning the original, beginning at the upper left-hand corner and

continuing from left to right in equal sections with small overlaps. Each

original is also photographed in one exposure and is included in reduced

form at the back of the book.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white

photographic prints are available for any photographs or illustrations

appearing in this copy for an additional charge. Contact UMI directly to

order.

UMI

A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor MI 48106-1346 USA 313/761-4700 800/521-0600

| <br> |  | · |

|------|--|---|

# COMPONENT SELECTION AND PIPELINING USING STOCHASTIC EVOLUTION

BY

### MOHAMMAD FAROOK

A Thesis Presented to the

FACULTY OF THE COLLEGE OF GRADUATE STUDIES

KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

# MASTER OF SCIENCE

**COMPUTER SCIENCE**

**JUNE 1996**

UMI Number: 1380769

UMI Microform 1380769 Copyright 1996, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

300 North Zeeb Road Ann Arbor, MI 48103

## KING FAHD UNIVERSITY OF PETROLEUM AND MINERALS DHAHRAN, SAUDI ARABIA

#### COLLEGE OF GRADUATE STUDIES

This thesis, written by MOHAMMAD FAROOK under the direction of his Thesis Advisor and approved by his Thesis Committee, has been presented to and accepted by the Dean of the College of Graduate Studies, in partial fulfillment of the requirements for the degree of MASTER OF SCIENCE in COMPUTER SCIENCE.

| THESIS | COM | MTTTE | Ð |

|--------|-----|-------|---|

|        |     |       |   |

Dr. Talal H. Maghrabi (Chairman)

Jadiy Sait. M.

Dr. Sadiq M. Sait (Co-Chairman)

Dr. Khalid Al-Tawil (Member)

Dr. Jarallah Al-Ghamdi (Member)

Department Chairman

Dean, College of Graduate Studies

Date: 24.7.96

The same of the sa

### Dedicated to

My Parents and Brothers

### Acknowledgments

First and foremost I thank Almighty Allah who gave me the opportunity, courage and patience to carry out this work.

Acknowledgement is due to King Fahd University of Petroleum & Minerals for providing support to this work.

I am indebted to my thesis chairman, Dr. Talal H. Maghrabi and Co-chairman Dr. Sadiq M. Sait for their help and advice. I acknowledge them for their encouragement and support. I would like also to place on record my appreciation for the cooperation and guidance extended by my committee members, Dr. Khalid Al-Tawil and Dr. Jarallah Al-Ghamdi. I am also thankful to the department chairman, Dr. Mulhem and other faculty members and staff for their cooperation.

I wish to express my gratitude to my parents, brothers, sisters-in-law, niece and nephews for their support, encouragement and motivation.

To all my friends, who have made my stay at KFUPM a memorable one, I thank you for your wonderful company and for being there when I needed the most.

### Contents

|   | Ack  | nowled  | lgements              | iv   |

|---|------|---------|-----------------------|------|

|   | List | of Fig  | ures v                | ⁄iii |

|   | List | of Tal  | oles                  | x    |

|   | Abs  | tract ( | English)              | _xi  |

|   | Abs  | tract ( | Arabic)               | xii  |

| 1 | Int  | roduct  | ion                   | 1    |

|   | 1.1  | Proble  | em Definition         | 7    |

|   | 1.2  | Litera  | ture Survey           | 10   |

|   |      | 1.2.1   | Allocation techniques | 14   |

|   |      | 1.2.2   | Scheduling techniques | 16   |

|   |      | 1.2.3   | Pipelining            | 21   |

|   | 1.3  | Soluti  | on techniques         | 24   |

|   |      | 1.3.1   | Iterative techniques  | 24   |

|   |     | 1.3.2 Constructive techniques                                 | 26 |

|---|-----|---------------------------------------------------------------|----|

|   | 1.4 | Summary                                                       | 28 |

| 2 | Sto | chastic Evolution and Simulated Annealing 2                   | 9  |

|   | 2.1 | Stochastic Evolution                                          | 30 |

|   |     | 2.1.1 Algorithm                                               | 30 |

|   |     | 2.1.2 PERTURB                                                 | 33 |

|   |     | 2.1.3 UPDATE 3                                                | }4 |

|   |     | 2.1.4 Issues Concerning Stochastic Evolution Algorithm        | 35 |

|   | 2.2 | Simulated Annealing                                           | 36 |

|   |     | 2.2.1 Background                                              | 37 |

|   | 2.3 | Algorithm                                                     | 10 |

|   | 2.4 | Problem-specific decisions                                    | 42 |

|   | 2.5 | Summary                                                       | 43 |

| 3 | Cor | nponent Selection and Pipelining using Stochastic Evolution 4 | 14 |

|   | 3.1 | Initial Solution Representation                               | 45 |

|   | 3.2 | Cost Function                                                 | 48 |

|   | 3.3 | PERTURB Strategy                                              | 49 |

|   |     | 3.3.1 Random Moves                                            | 49 |

|   |     | 3.3.2 Fixed Random Moves                                      | 50 |

|   |     | 3.3.3 Top-Down Strategy                                       | 52 |

|   |     | 3.3.4 Bottom-up strategy                                      | 54 |

|   |     | 3.3.5 Perturb Function                                        | 50 |

|   |     |                                                            | vii |

|---|-----|------------------------------------------------------------|-----|

|   | 3.4 | Post Processing                                            | 59  |

|   | 3.5 | Update Function                                            | 60  |

|   | 3.6 | Parallelizing Stochastic Evolution Algorithm               | 61  |

|   | 3.7 | Summary                                                    | 64  |

| 4 | Cor | nponent Selection and Pipelining using Simulated Annealing | 65  |

|   | 4.1 | Initial, Current and Best Solution                         | 66  |

|   | 4.2 | Cost Function                                              | 66  |

|   | 4.3 | Generation of Moves                                        | 66  |

|   | 4.4 | Metropolis Function                                        | 67  |

|   | 4.5 | Tuning of Parameters                                       | 69  |

|   | 4.6 | Parallelizing simulated annealing                          | 70  |

|   | 4.7 | Summary                                                    | 72  |

| 5 | Exp | perimental Results                                         | 73  |

| 6 | Coı | nclusions and Future work                                  | 84  |

|   | 6.1 | Conclusions                                                | 84  |

|   | 6.2 | Future Work                                                | 85  |

|   | Bib | diography                                                  | 86  |

|   | Vit | a                                                          |     |

### List of Figures

| 1.1  | Relationship of HLS with logic and layout synthesis      | 3   |

|------|----------------------------------------------------------|-----|

| 1.2  | HLS in design hierarchy.                                 | 4   |

| 1.3  | Steps involved in HLS                                    | 6   |

| 1.4  | A sample data flow graph                                 | 9   |

| 1.5  | One possible solution to the example shown in Figure 1.4 | 11  |

| 1.6  | Another solution for the example shown in Figure 1.4     | .11 |

| 1.7  | Different states of the solution space                   | 13  |

| 1.8  | Example of ASAP scheduling [4]                           | 18  |

| 1.9  | Example of list scheduling [4]                           | i8  |

| 1.10 | Example of FDS [4]                                       | 20  |

| 2.1  | HLS system                                               | 31  |

| 2.2  | Stochastic Evolution algorithm.                          | 32  |

| 2.3  | PERTURB Function                                         | 34  |

| 2.4  | UPDATE procedure                                         | 35  |

| 2.5  | Simulated Annealing algorithm.                           | 39  |

| 2.6  | Metropolis Procedure                                     | 41  |

| 3.1 | Random move strategy                                                  | 51  |

|-----|-----------------------------------------------------------------------|-----|

| 3.2 | Fixed random moves                                                    | 52  |

| 3.3 | Top-Down strategy                                                     | 53  |

| 3.4 | Bottom-Up Strategy                                                    | 55  |

| 3.5 | PERTURB algorithm                                                     | 57  |

| 3.6 | PERTURB with post processing.                                         | 60  |

| 4.1 | The Metropolis Algorithm                                              | 68  |

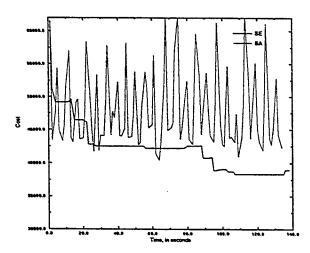

| 5.1 | Plot showing the comparison between SA and MSE during the initial     |     |

|     | stages                                                                | 77  |

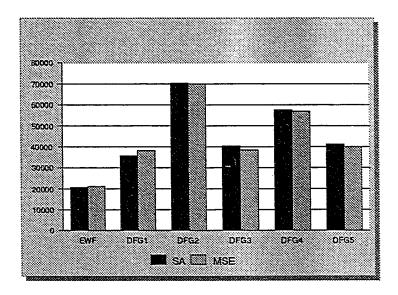

| 5.2 | Barchart showing the results of SA and MSE during the initial stages. | 78  |

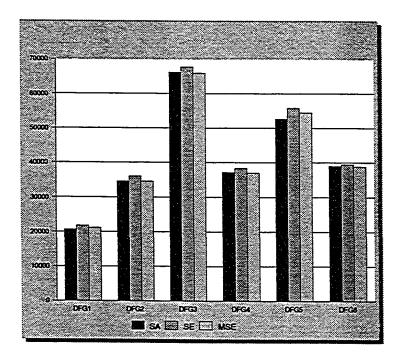

| 5.3 | A barchart showing the comparisons between SA, SE and MSE (post-      |     |

|     | processing)                                                           | -79 |

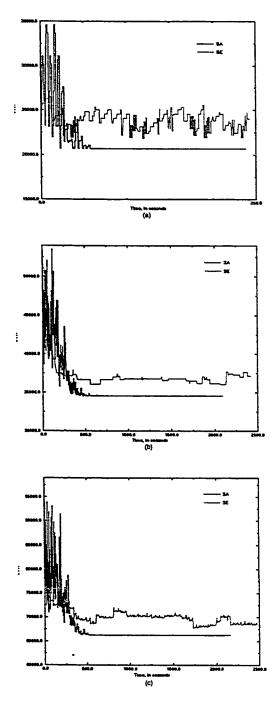

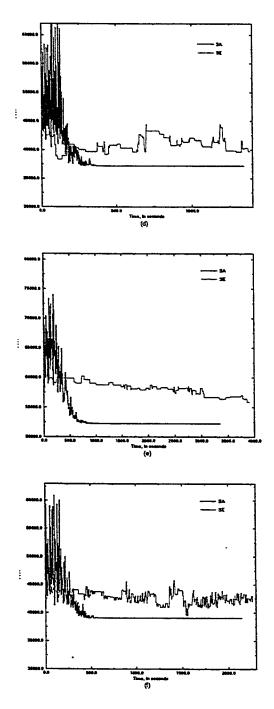

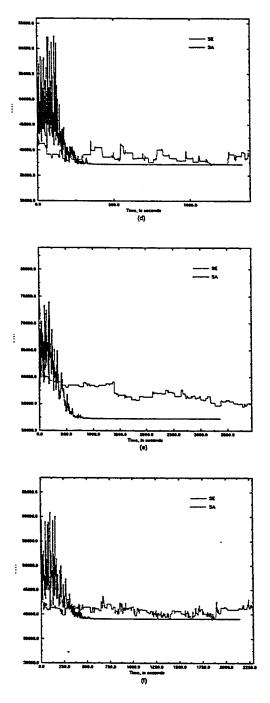

| 5.4 | Plots for different DFG's using SA and SE techniques: (a) EWF, (b)    |     |

|     | Graph 1, and (c) Graph 2 (contd)                                      | 80  |

| 5.5 | Plots for different DFG's using SA and SE techniques: (d) Graph 3,    |     |

|     | (e) Graph 4, and (f) Graph 5                                          | 81  |

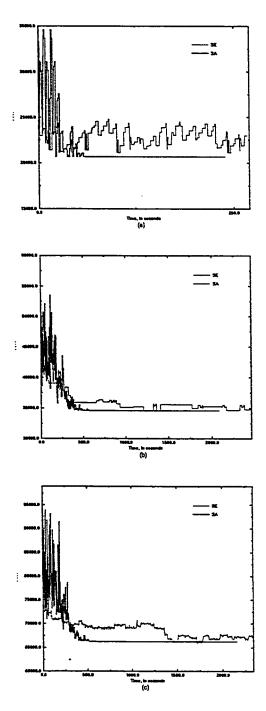

| 5.6 | Plots for different DFG's using SA and MSE (post-processing) tech-    |     |

|     | niques: (a) EWF, (b) Graph 1, and (c) Graph 2 (contd)                 | 82  |

| 5.7 | Plots for different DFG's using SA and MSE (post-processing) tech-    |     |

|     | niques: (d) Graph 3, (e) Graph 4, and (f) Graph 5                     | 83  |

### List of Tables

| 1.1 | Example of a component library.                                   | 10 |

|-----|-------------------------------------------------------------------|----|

| 3.1 | Component Library.                                                | 47 |

| 5.1 | Characteristic of input graphs                                    | 74 |

| 5.2 | Stochastic Evolution results                                      | 75 |

| 5.3 | Stochastic Evolution and Simulated Annealing results              | 76 |

| 5.4 | Modified Stochastic Evolution (post-processing) and Simulated An- |    |

|     | nealing results.                                                  | 76 |

| 5.5 | Comparisons between SA, SE and MSE (post-processing)              | 79 |

#### ABSTRACT

Name:

Mohammad Farook

Title:

Component Selection and Pipelining

by stochastic evolution:

Degree:

Master of Science

Major Field:

Information & Computer Science

Date of Degree: June 1996

High-level synthesis is the process of translating a high-level program like specification of the behavior of a digital circuit into a structural design in terms of interconnected set of Register-Transfer level components. Component selection and pipelining is one of the important problems in HLS. We investigate the application of Stochastic Evolution (SE) for solving component selection and pipelining and compare it with Simulated Annealing (SA) for the same computation time. The inputs are a Data Flow Graph (DFG), a realistic component library with multiple implementations of operators and Latency and Pipe stage delay constraints. Component selection involves replacing components of the DFG by slower components to minimize the cost. The cost function is the sum of costs (in gates) of all the components of the DFG and the pipeline registers. Pipelining is done based on the constraints of latency and pipe stage delay specified. A new method of improving the results in SE, called post-processing is proposed. This is called Modified Stochastic Evolution (MSE) technique. In post-processing, after obtaining a valid state the DFG is scanned to see if there is a possibility of replacing one or more components by slower components of the same type without violating the constraints. Experiments were carried out on different types of DFGs. The performance of SA is better than SE without postprocessing, while SE performs better than SA in some cases when post-processing is introduced.

Master of Science Degree King Fahd University of Petroleum and Minerals, Dhahran. June 1996

### خلاصة الرسالة

الاسم : محمد فاروق

عنوان الرسالة : اختيار المكونات و خط التوصيل التسلسل العشواتي

التخصص علم الحاسب و المعلومات

تاريخ الشهادة : يونيو ١٩٩٦م

التصميم عالي المستوى هو عملية ترجمة برنامج عالي المستوى مثل تحديد وصف دائرة رقمية ألى تصميم هيكلى باستعمال مجموعة متصلة من المكونات ذات مستوى المسجل الناقل، اختيار المكونات و خط التوصيل من المواضيع المهمة فى تصميم عالي المستوى. نبحث استخدام انتسلسل العشوائي لحل اختيار المكونات و خط التوصيل و منه ثم نقارنة مع محاكاة التلدية لنفس وقت التحسيب. والمدخلات هي رسم تدفعة المعلومات و مكتبة مكونات واقعية تحوى تنفيذات متعددة العوامل شروط تاخير, مرحلة التوصيل و وقت الانتظار الختيار المكونات تشمل تبديل بعض مكونات رسم تدفعة المعلومات بأخرى أيطاً لتقليل التكلفة. أن دالة التكلفة هي مجموع تكاليف جميع المكونات رسم تدفعة المعلومات و مسجلات خط التوصيل. خطوط الاتصال تبنى اعتمادا على وقت الانتظار و تاخير مرحلة التوصيل. و في هذا البحث نفتوح طريقة تسلسل العشوائي معدلة و ذلك باعادة النظر في امكانية تبديل أحد المكونات أو أكثر بمكونات ابطاً من نفس النوع دون مخالفة الشروط. وقد تم تنفيذ تجارب على أنواع مختلفة من رسوم تدفعة المعلومات. أن أدا محاكاة التندية أفضل من التسلسل العشوائي ولكن التسلسل العشوائي ولكن التسلسل العشوائي المعدل يودى أفضل من محاكاة التلدية في بعض الحالات عند الخال مرحلة ما بعد التنقذ.

درجة ماجستير علوم جامعة الملك فهد للبترول و المعادن الظهران ، المملكة العربية السعودية

### Chapter 1

### Introduction

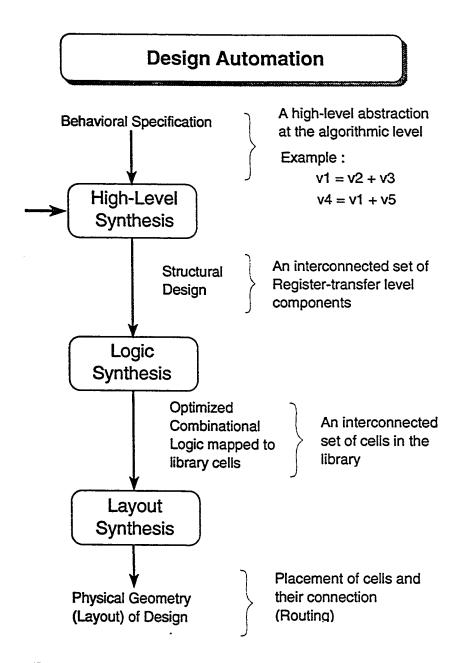

Design automation is the automatic synthesis of a physical design from some higherlevel behavioral specification [1]. Automatic synthesis is much faster than manual design as it reduces the design cycle considerably. It also gives the designer a scope for experimentation. Synthesis is used for commercial implementations of systems which are widely used for production-level design of digital circuits. Synthesis can be divided into the following main categories.

- High-level synthesis converts a high-level program-like specification of the behavior of a circuit into a structural design in terms of an interconnected set of Register-Transfer (RT) level components, such as ALUs, registers and multiplexors.

- Logic synthesis converts a structural design, an interconnected set of RT level components, into optimized combinatorial logic, and maps that logic onto the library of available cells.

Layout synthesis converts an interconnected set of cells, which describes the structure of a design, into the exact physical geometry (layout) of the design.

It involves both, the placement of the cells as well as their connection (routing).

Figure 1.1 shows the relationship of high-level synthesis with the logic synthesis and layout synthesis in design automation.

High-level synthesis raises the level of abstraction to the algorithmic level, allowing a more behavioral style specification. Behavioral specification aims at describing only the functionality of a circuit representing the way the system or it's components interact with the environment. Structure refers to the set of interconnected components that make up the system. Usually there are different structures that can be used to realize a given behavior.

The place of HLS in design hierarchy is illustrated in Figure 1.2. The level of detail increases from left to right in Figure 1.2. Also, five levels of abstraction shown in synthesis can take place, namely system, algorithmic, register-transfer, logic and circuit levels. Going from the algorithmic behavior to register-transfer level structure is HLS as shown in Figure 1.2. High-level synthesis bridges the gap between behavioral specifications and their hardware structure, automatically generating circuit descriptions that can be used for logic synthesis [2]. As opposed to logic synthesis which optimizes any combinational logic, high-level synthesis also deals with the memory elements, the interconnection structure (buses and multiplexors), and the sequential aspects of the design.

High-level synthesis is a formidable task. Although the main problems have been addressed, further optimizations involving area, cycle time, and sequential behav-

Figure 1.1: Relationship of HLS with logic and layout synthesis.

| LEVEL                 | DOMAINS                 |                                    |                         |

|-----------------------|-------------------------|------------------------------------|-------------------------|

|                       | Behavior                | Structure                          | Physical                |

| System                | Communicating processes | Processors<br>Memories<br>Switches | Cabinets<br>Cables      |

| Algorithmic           | Input-Output            | Memory, Ports<br>Processors        | Board<br>Floorplan      |

| Register-<br>Transfer | Register<br>Transfers   | ALUs, REGs,<br>Muxes, Buses        | ICs<br>Macro Cells      |

| Logic                 | Logic<br>Equations      | Gates<br>Flip flops                | Standard Cell<br>Layout |

| Circuit               | Network<br>Equations    | Transistors,<br>Connections        | Transistor<br>Layout    |

Figure 1.2: HLS in design hierarchy.

ior are necessary to obtain high quality designs. It is also difficult to describe the hardware problem in terms of behavioral models. This makes it necessary to develop synthesis systems that allow specifications at various levels. There is a lack of effective high-level verification techniques that makes the application of high-level synthesis difficult. Since correctness by construction cannot be expected from a software system with several hundred lines of code, verification methods are necessary.

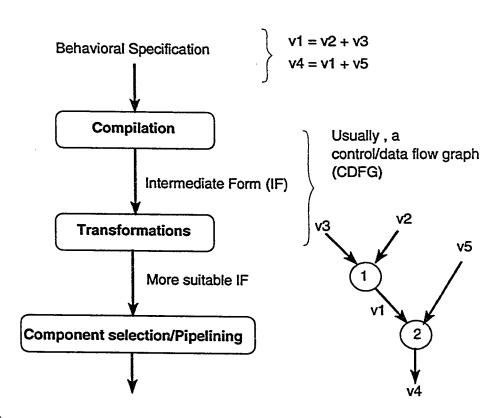

The main steps involved in high level synthesis are:

- Compilation of the HDL (High level description language is a sequential language similar to a programming language) source into an internal representation, usually a data flow graph and/or a control data flow graph.

- Transformations of the internal representation into a form more suitable for high-level synthesis. These transformations involve both compiler like and hardware-specific transformations.

- Scheduling, involves assigning each operation to a time step. It is also called

control synthesis or control step scheduling.

- Allocation, which involves assigning each operation to a piece of hardware.

It consists of selection of the type of hardware modules from a library and mapping each operation to the selected hardware. Allocation is also referred to as data path synthesis or data path allocation.

- Partitioning, which consists of dividing the design into smaller pieces. Partitioning can aim at obtaining a collection of concurrent hardware modules, or

can simply be used to generate smaller hardware pieces that may be easier to synthesize further.

Output generation which produces the design is passed to logic synthesis and finite state machine synthesis.

Figure 1.3: Steps involved in HLS.

The steps involved in high-level synthesis are illustrated in Figure 1.3. In order to extract the structure, the algorithmic specifications are first converted to an intermediate form such as Control/Data Flow Graphs (CDFGs), in which nodes correspond to operations (for example addition, multiplication, etc.,) and edges correspond to data values (for example variables and constants) and control flow dependencies.

Some compiler like high-level transformations (such as dead-code elimination, common subexpression elimination, etc.,) are applied to optimize the behavior of the design resulting in a more suitable intermediate form. This intermediate form is then used for allocation and pipelining.

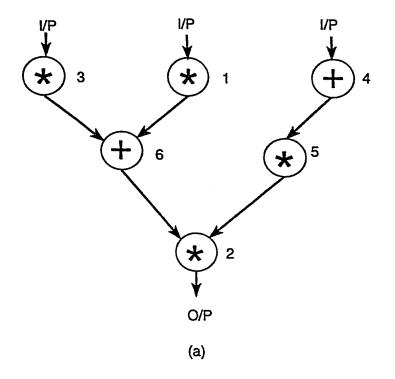

Component selection and pipelining are some of the important steps in the synthesis of circuits from behavioral descriptions [3]. Component selection involves determining the best selection of components from a realistic library containing many different implementations per operator, and pipelining involves providing pipeline registers in the circuit such that the delay of each pipe stage is as close as possible to the given constraints [4].

### 1.1 Problem Definition

An important factor in obtaining cost effective designs is the ability to use multiple operator implementations in the datapath. Delay paths can then be balanced by using slow components where possible and using faster components only when necessary. For high performance applications it is necessary to combine pipelining with the use of a multiple-implementation library to satisfy performance requirements at a reasonable cost while satisfying certain constraints.

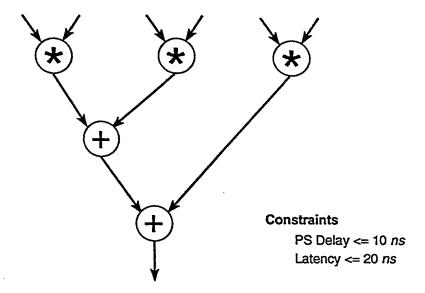

Given a data flow graph DFG(V, E) where V represents a set of vertices, and  $E \subseteq V * V$ , a set of directed edges, a component library CL consisting of a set of three tuples ( $Component\_type$ , Area, Delay), and constraints on pipe stage (PS) delay and latency, find an assignment of vertices to components and a partition so as to minimize the cost (given by the sum of the area of the datapath components).

The terms PS delay, Assignment and Partition are defined as follows:

- PS delay: Is the sample inter-arrival delay, that is, the delay between the

arrival of two consecutive input samples. This is also the clock cycle of the

design. Throughput, which is often the prime constraint on DSP systems, is

the inverse of the PS delay.

- Assignment: If we associate a type (such as \*, ÷, +, -) called Vertex\_type(v), with every vertex v then an assignment is defined as a function from V → CL such that if Assignment(v) = c then Vertex\_type(v) = Component\_Type(c). This states that vertices can only be mapped to components of the same type.

- Partition: A Partition is a collection of subset of vertices, such that the union

of all subsets is the complete vertex set V, and the intersection of any two

subsets is the empty set.

Partitioning in the problem of component selection and pipelining refers to the pipeline stages in the DFG.

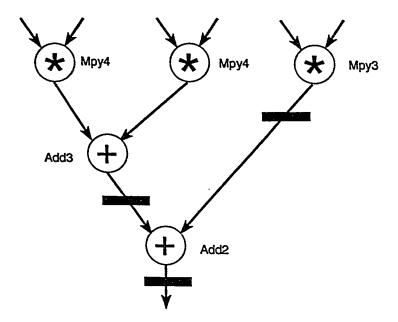

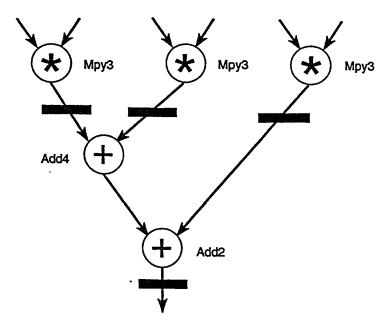

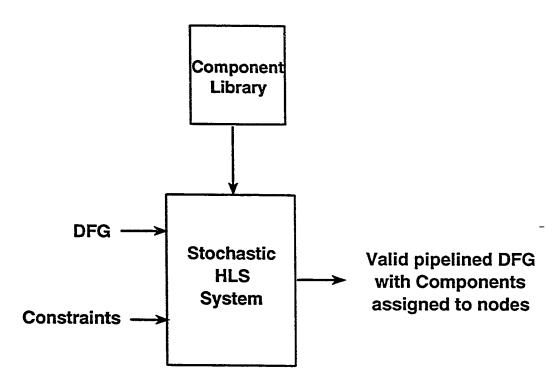

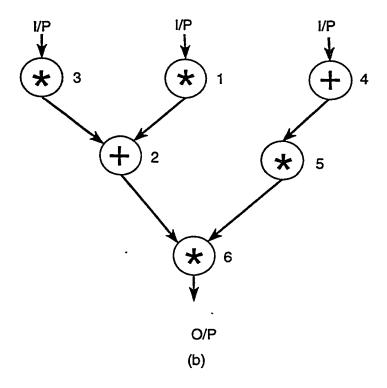

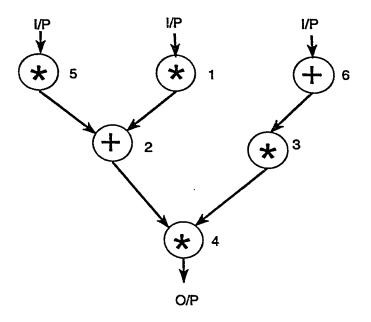

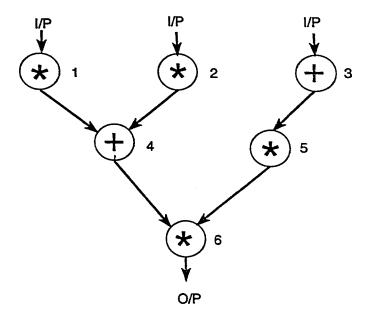

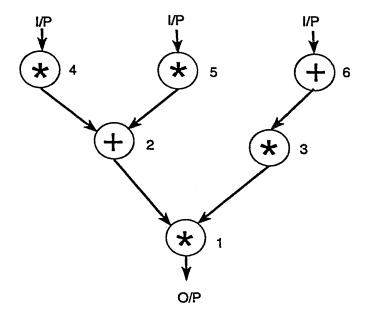

The DFG shown in Figure 1.4 along with the constraints is an example of the problem. The DFG consists of three multipliers and two adders. The PS delay constraint is 10 ns and Latency is 20 ns. The DFG consists of vertices which correspond to different operators depending on the circuit and directed edges that determine the interconnections between vertices and also the flow of operations between the input and output stages. The objective is to map the components from the multiple component library, shown in Table 1.1, onto the vertices to obtain a cost-optimal solution. Cost-optimal solution for this problem is obtained by minimizing the area

Figure 1.4: A sample data flow graph.

occupied in terms of the number of gates without violating the constraints and also pipelining the DFG. Pipelining is done by traversing the DFG from the inputs towards the output. When the sum of all the delays in the path exceeds the specified PS delay constraint then a register is placed. This is done for all the branches until the entire DFG satisfies the PS delay constraint.

The multiple component library shows different types of operators along with the area and delay of each of the operators. The availability of a large number of operators of each type is assumed.

A cost-optimal solution is obtained by an appropriate mapping of components from the component library onto the vertices of the DFG. Different types of iterative/constructive techniques may be used to obtain a cost-optimal solution. Figure 1.5 shows one possible solution. This consists of two multipliers of type Mpy4,

| Component | Component | Area  | Delay |

|-----------|-----------|-------|-------|

| Type      | Name      | Gates | ns    |

| *         | Mpy1      | 100   | 30    |

| *         | Mpy2      | 200   | 20    |

| *         | Mpy3      | 250   | 10    |

| *         | Mpy4      | 300   | 5     |

| +         | Add1      | 50    | 20    |

| +         | Add2      | 70    | 8     |

| +         | Add3      | 80    | 5     |

| +         | Add4      | 100   | 2     |

| Register  | Reg       | 50    |       |

Table 1.1: Example of a component library.

one multiplier of type Mpy3 and two adders of type Add3 and Add2 respectively. This solution requires three registers. The total cost is 1150 gates. Figure 1.6 shows another solution. In this figure three multipliers of type Mpy3 and two adders of type Add2 and Add4 are used. This solution requires a total of four registers and it's total cost is 1120 gates. Both the solutions satisfy the PS delay and the latency constraints.

### 1.2 Literature Survey

The existing optimization techniques [5] can be classified into two types: iterative/constructive and global. Iterative/constructive techniques assign elements to vertices which represents the behavior of the circuit (operations, values or data transfers), one at a time, while global techniques find simultaneous solutions to a number of assignments at a time. More specifically, iterative/constructive techniques select

Figure 1.5: One possible solution to the example shown in Figure 1.4.

Figure 1.6: Another solution for the example shown in Figure 1.4.

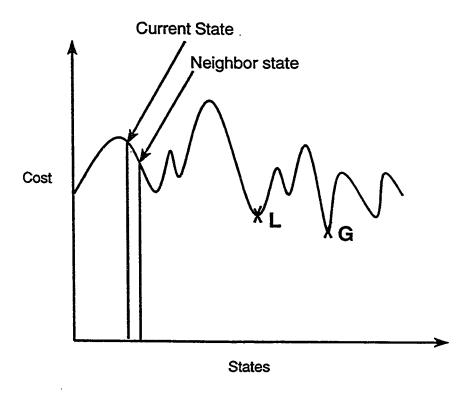

an operation, value or interconnection to be assigned, make the assignment, and then iterate until all the assignments are made. These techniques generally look at a restricted window in the search space than global techniques, therefore are more time efficient, but are less likely to find optimal solutions. The optimization techniques are used in order to obtain cost-effective solutions within a limited time period. The size of the solution space for component selection and pipelining can be calculated as follows. If there are n number of vertices, m number of edges in the DFG, and k are the number of components in the component library, then the number of possible solutions are  $k^n * 2^m$ . A number of iterative/constructive techniques have been developed for solving problems having a large solution space. Some of these iterative techniques uses the hill-climbing approach. The hill climbing approach is to accept both solutions having higher and lower costs. Figure 1.7 shows the different states in the solution space. This figure shows a plot of cost versus states. The label L represents a local minima while G represents the global minima. The state G is reached by moving from the current state to the state at point Gthrough a number of intermediate states. A new state is obtained by disturbing one or more components of the current state. It is seen that from the local minima L, we accept both costs that are higher than those that are present at L and and those that are lesser than it. Finally we reach a point G, the global minima.

Examples of systems using iterative/constructive techniques are found in [6, 7]. Scheduling and allocation are two important phases in the synthesis of circuits from behavioral descriptions. Component selection and pipelining are also important steps in HLS. These are described in detail in the following sections.

Figure 1.7: Different states of the solution space.

#### 1.2.1 Allocation techniques

Allocation assigns each operation, variable and communication path to a piece of hardware. It naturally falls into three parts: Functional unit (FU) allocation, register allocation, and connection allocation. In high-level synthesis, the main aim in allocation is to share hardware units, i.e., operations can share functional units (ALUs, adders, etc.), variables can be mapped onto common registers and memories can share buses and multiplexors. The goal of allocation is to optimize the overall hardware.

A problem closely related to allocation is module assignment. Whenever there is more than one type of functional unit to perform a particular operation, that operation has to be assigned to one specific functional unit type. Such problems are solved using heuristic techniques. The different types of allocation algorithms that can be used are:

- 1. Heuristic allocation, e.g., greedy and sequential allocation.

- 2. Linear programming approaches.

- 3. Graph-based algorithms.

Heuristic approaches usually select one element (operation or variable) at a time to allocate and assign it to the hardware, with the selection done according to different criteria. Heuristic approaches yield reasonable results, are fast and have the potential to mix FU, register and communication path allocation.

Linear programming (LP) approaches formulate allocation (or allocation and scheduling) as a linear programming problem. In the past, however, since linear

programming required extensive computational resources, it could only be used for small examples. Recently, the method has reappeared, among other reasons because modern large LP systems can solve problems with tens of thousands of variables.

The third group of algorithms formulate allocation as clique covering (or partitioning) of a compatibility graph or node coloring.

Global allocation techniques include graph theoretic formulations, Branch and Bound algorithms and mathematical programming techniques. Trickey [8] used a graph theoretic approach in which the elements to be assigned to hardware, whether they are operations, values or interconnections, are represented by nodes, and there is an arc between two nodes if and only if the corresponding elements can share the same hardware. The problem then becomes one of finding sets of nodes in the graph, all of whose members are connected to one another, since all the elements in such a set can share the same hardware without conflict. An example of a system using Branch and Bound technique is SPLICER [9]. Formulations of allocation and component selection as a mathematical programming problem involves creating a variable for each possible assignment of an operation, variable or interconnection to a hardware element. The variable is one if the assignment is made and zero if it is not. Constraints must be formulated which guarantee that each operation must be assigned to one and only one hardware element, and so on. The objective is to find a valid solution that minimizes some cost function. STAR allocation system [10] uses an iterative improvement technique. It uses a rip-up reconstruct approach to the allocation problem. The data path is refined globally by evaluating the binding quality of each object, probabilistically selecting a cluster of heavily correlated objects (which may consist of variables, operations, and data transfers), and rebinding them to form a better design or determine that there can be no more cost improvement.

Several optimization problems are computationally intractable, i.e., their decision versions are NP complete. There have been several deterministic heuristics suggested in the past for solving specific NP-complete problems. However most of these heuristics are essentially descent algorithms with respect to the cost function, hence they are unable to escape the local minima with respect to the underlying neighborhood structure. The simulated annealing (SA) algorithm introduced by Kirkpatrick et al., [11] is an iterative stochastic procedure for solving combinatorial optimization problems. Proofs of convergence to a global minima and successful experimental implementations have led to the widespread use of SA and it's acceptance as a viable general method for combinatorial optimization. However in general SA suffers from two major drawbacks. The first one being that an actual implementation of SA requires careful tuning of some of it's parameters to achieve good results. The second one is that it uses excessive computation time and it's often less effective when compared with some well designed deterministic heuristics for the specific problem being solved.

### 1.2.2 Scheduling techniques

Scheduling assigns each operation in the behavior to a point in time. In synchronous systems, time is measured in control steps. Scheduling aims at optimizing the number of control steps needed for completion of a function, given certain limits on hardware resources and cycle time. A scheduling algorithm must take into account the

control constructs, such as loops and conditional branching, the data dependencies expressed in the data flow graph, and constraints on the hardware. In synchronous hardware the basic constraints are that every unit of the hardware can be used only once during the control step, i.e., registers can be loaded only once, combinational logic may evaluate once (feedback is forbidden) and buses may carry only a single value. Other constraints on a design may restrict the size, the delay, and the power.

The first approach to scheduling in high-level synthesis was probably the exhaustive search. Since then, many scheduling algorithms have been proposed for high-level synthesis have been proposed, some relying on methods known from microprogram optimization. Davidson et. al., [12] discuss an exhaustive search using branch-and-bound techniques, as-soon-as-possible (ASAP) scheduling and scheduling the critical path first.

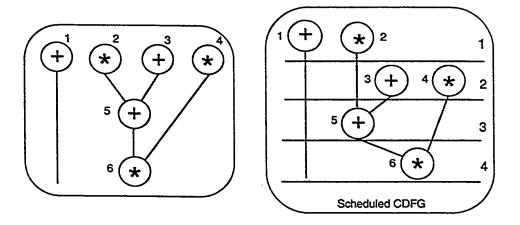

In an ASAP schedule, all operations are assigned to the earliest possible control step, corresponding to a topological sort of the graph in the depth-first order. An example of CDFG with its ASAP schedule under the constraint of one adder and one multiplier is shown in Figure 1.8 [5].

List Scheduling schedules operations into control steps, one control step at a time. For the current control step, a list of data ready operators is constructed, containing those operators whose inputs are produced in earlier control steps and that do not violate any resource constraints. This list is then sorted according to some priority function, the highest-priority operator is placed into current control step, the list is updated, and the process continues until no more operators can be placed into the control step. This process is then repeated on the next control step, until the entire design is scheduled. List scheduling is illustrated in Figure 1.9 [5].

Figure 1.8: Example of ASAP scheduling [4].

The priority function is the path length from the node to the end of the block which is shown in Figure 1.9a and the list schedule is shown in Figure 1.9b. Variations of list scheduling are used in many high-level synthesis systems, for example, CMU's System Architect's Workbench [13].

Figure 1.9: Example of list scheduling [4].

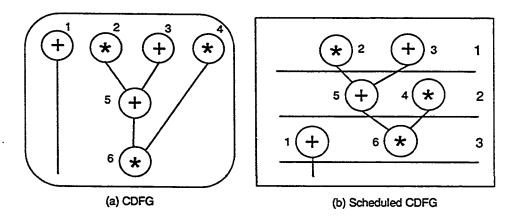

A more complex scheduling method is force – directed scheduling [14], which uses a global criterion that indicates how crowded a control step is compared with

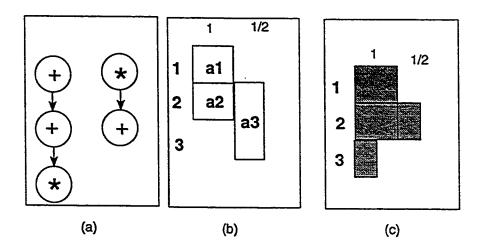

others to decide where to schedule an operation. The probability of operations being in a given control step can be calculated by using mobility which is the difference between the ASAP and the as-late-as-possible (ALAP) schedules. For example, if an operation can be scheduled in three steps, it has a mobility of 3. Thus, the probability of the operation to be scheduled in each of these steps is 1/3. Adding all the probabilities of any control step gives a measure of how crowded that control step is. This measure is called the distribution because it tells how much hardware will be required. After determining the distribution for all control steps, the effect for each possible assignment of an operation v to a control step s can be calculated. Then the operation/control-step pair can be scheduled to minimize the distribution differences among control steps. The quantitative measure of scheduling v in s is calculated on the distribution using an equation that is analogous to the force in a spring (spring constant times displacement, where the constant is the original distribution for a control step and the displacement is the change in the distribution value). Thus, this scheduling algorithm is called forced-directed scheduling (FDS). FDS is illustrated in Figure 1.10 [5]. A CDFG with three add operations labeled as a1, a2 and a3 is shown in Figure 1.10a. Figure 1.10b shows time frames for add operations, that is the probability of each operation being in a given control step. Distribution is shown in Figure 1.10c. Calculation of force involved in assigning a3 to control step 2 is shown in Figure 1.10. As we see in Figure 1.10c the control step 2 is heavily loaded, and thus the positive force indicates that a3 should not go into control step 2.

All of the above scheduling techniques, except exhaustive search and branch and bound techniques come under iterative/constructive techniques. Another approach

Force involved in assigning a3 to step 2:

Figure 1.10: Example of FDS [4].

to scheduling by transformation is to use heuristics to guide the process. Starting with an initial schedule, transformations that promise to move the design closer to the given constraints or to optimize the objective are chosen. In the former, we first assign each operation to a separate control step and then merge control steps iteratively without violating any constraints. In the latter, we first assign all operations to a single control step and then divide this control step until we have no constraint violations.

#### 1.2.3 Pipelining

Pipelining is a common technique to enhance the circuit performance. In a pipelined implementation, the circuit is divided into stages. Each stage executes concurrently and feeds it's results to the following stage.

Pipelining has been applied to instruction set to support efficient execution of different instruction streams and to signal/image processors. Conversely pipelined digital signal processing (DSP) design may be simpler, because often the processor is dedicated to an application.

Few techniques for synthesizing pipelined data paths have been proposed under some limiting assumptions such as constant data rates. Unfortunately efficient instruction set processor design requires handling variable data rates as well as a variety of other issues, such as stage bypasses, hazard analysis and support for controlling the pipeline by allowing stalling and flushing. As a result, present synthesis techniques are not yet applicable to the design of competitive instruction set processors, although they have been applied successfully to some DSP designs. To achieve pipelining, the input task (process) must be subdivided into a sequence of subtasks. each of which can be executed by a specialized hardware stage that operates concurrently with other stages in the pipeline. Consecutive tasks are initiated at an interval which is the integer multiple of a clock cycle and is shorter than pipeline latency. Some ad hoc representation paradigms have been developed for pipelined circuits. For example, pipelined circuits can be specified by modeling each stage independently as well as the stage interfaces and the synchronization mechanisms. This corresponds to providing a mixed structural/behavioral circuit model that may preclude architectural optimization of the circuit as a whole. In particular, the number of stages is prescribed. Circuits are modeled by pipelining sequencing graphs where the source vertex is fixed at the throughput rate. The time interval between two successive inputs is called the data introduction interval. Generally the data introduction interval is smaller than latency. If the data introduction interval equals latency, then the operations are performed without using any pipeline registers. If the latency is greater than the data introduction interval then pipelining can be introduced at different intervals in the circuit, so that delay between consecutive pipeline registers is less than or equal to the data introduction interval.

The design objectives of pipelined circuits are four: area, latency, cycle — time and throughput. Architectural exploration and optimization relate to determining the tradeoff points in the corresponding four-dimensional space. Most approaches consider the sequence of problems derived by choosing particular values of the data introduction interval and of the cycle-time (hence determining implicitly the throughput) and a search for optimal (area, latency) tradeoff points. Several optimization techniques can be used to obtain a cost-optimal solution. Some of them are

stochastic evolution, simulated annealing, genetic algorithm and integer programming.

A scheduling and hardware sharing (allocation) algorithm for synthesizing both pipelined and non-pipelined data paths is presented in [15]. In this the scheduling algorithm tries to distribute operations equally among partitions to maximize hardware sharing. Multiplexer delays are explicitly considered to produce a more accurate scheduling. In hardware sharing the structural parameters such as the size of the multiplexers, interconnect overhead, the size of smallest sharable operator etc., are employed to control the amount of sharing globally and produce a heuristically optimized RTL structure. The scheduling algorithm is iterated until a satisfactory structure is obtained. This algorithm could also be used for synthesizing pipelined data path from a graphics process description that contains about 1000 components.

Jun and Hwang [16] describe the SODAS-DSP system, a pipelined datapath synthesis system targeted for application-specific DSP chip design. Through facilitated user interaction, the design space of pipelined datapaths for given design descriptions are explored to produce an optimal design. Taking a signal flow graph as the input SODAS-DSP generates pipelined datapaths through scheduling and module allocation processes. New scheduling and module allocation algorithms have been proposed for efficient synthesis of pipelined hardwares. The proposed scheduling algorithm is of iterative/constructive nature, where the measure of equidistribution of operations among pipeline partitions is adopted as the objective function. This DSP system generates efficient pipelined datapaths compared to Sehwa [17].

A method for pipelining VLSI/ULSI systems for effective communication is proposed in [18]. Propagation delays of data signals have been known to severely impair

performance of VLSI/ULSI interconnection networks. A simple but effective way has been proposed to increase the performance. The basic idea of the technique relies on the fragmentation of the wires and in reconnecting them with a special device called a repeater in order to form a bidirectional pipeline. By employing this technique the transmission speed is improved by 150% for 32-byte messages when a 10 cm 8-bit bus is used. It is seen that the improvement increases for longer messages and for larger skews.

## 1.3 Solution techniques

Iterative and constructive techniques have been used to solve a wide range of problems. The iterative techniques such as tabu search, simulated annealing, simulated evolution, genetic algorithm, stochastic evolution etc., have been used.

## 1.3.1 Iterative techniques

Amellal and Kamenska [19] have proposed one such iterative technique that describes a tabu search synthesis system for functional synthesis. The functional synthesis of a digital system is the realization of a register-transfer level description from the functional specification of the system. Synthesizing a digital system from a functional description is a complex process requiring the solution of various different problems. A control and data flow graph for representation is developed and this model generates a single graph representing both the data and the control flow of a VHDL behavioral description. The use of conditional dependency edges in the graph gives a better implementation of the control constructs. A new mathematical

formulation of the scheduling problem using a approach based on penalty weights is developed. Penalty weights include the real costs of the hardware units available in a given technology. The penalty weights take into consideration different area parameters of the design to be generated. The number of functional and storage units as well as the number of interconnections is optimized by the minimization of an objective function including penalty weights.

Sait et. al., [20, 21] solve the problem of scheduling and allocation using two iterative techniques namely genetic algorithm (GA) and tabu search. The problems of allocation and scheduling are formulated as an optimization problem. A new chromosomal representation for scheduling and allocation is proposed using GA technique. Apart from this, two new crossover operators to generate legal schedules has been developed. The problem of scheduling and allocation has been implemented using the tabu search technique. Using this technique a good initial solution, a neighborhood generation strategy, formulation and maintenance of tabu lists, a proper aspiration level criteria and a good tabu list size has been developed.

The related research based on pipelining and component selection can be categorized into two classes. The first class consists of tools like Sehwa [17], the tools from the GS Corporation R&D laboratories [15], and PLS a pipelined scheduler [22]. These tools pipeline a given DFG so as to optimize area and performance for given constraints, usually on the throughput or latency of the design. However they all assume a single implementation for functional units which force them to use the same component on non-critical and critical paths, resulting in designs that are inefficient and costly. SLIMOS [23] and MOSP [24] differ slightly from the above approach - they start from a multiple implementation library and then select one

single implementation per operator. Hence their final design also contains single implementations, leading to the same design inefficiencies.

The second category contains algorithms such as Tabu search (TBS) [4] and the module selection algorithm in [25]. Though these tools use unrestricted libraries that allow multiple physical implementations for the same operator, they combine component selection with non-pipeline scheduling, rather than pipelined scheduling.

Stochastic evolution (SE) is an iterative technique that has been applied to problems of certain complexities like network bisection and traveling salesman problems. We wanted to investigate the application of SE to problems whose complexities are similar to those of component selection and pipelining. This problem was also solved by simulated annealing (SA) and the two techniques were compared. The reason for comparing SE with SA is due to the similarities between the two techniques. Both the techniques are stochastic in nature, both accept downhill moves and they have control parameters that govern the probability of accepting the uphill moves. The basic difference between these two techniques is in the determination of the range of magnitude of the negative gains and in their method of acceptance.

## 1.3.2 Constructive techniques

Constructive techniques search a small part of the solution space. The heuristics employed by these techniques generally do not produce a optimal solution, but these produce effective results within a short duration. Many constructive techniques have been implemented in HLS systems. Sait et. al., [26] describes a loop-based scheduling algorithm. In this algorithm a subset of some high-level programming

language is used to describe the behavior of the intended design. An intermediate form is generated by using the programming language compiler in the transformation process. The use of the compiler results in optimization and avoids restricting the language to certain data types or control constructs. In order to eliminate machine dependency and complexity the intermediate form is converted into another form which is machine independent and has simpler syntax and semantics, called Pseudo Assembly language (PAL). PAL descriptions are used by the system components to produce the intended hardware in an RTL description language. Scheduling in this HLS system is done in a constructive manner using Loop Based Scheduling (LBS). In LBS the control flow graph is partitioned into subgraphs, then each of the subgraphs are scheduled individually and finally the individual schedules of all the subgraphs are combined.

A constructive heuristic has been used to solve the problem of component selection and pipelining [3]. The objective is to maximize the use of slow components and minimize the use of faster components while satisfying the constraints of PS delay and latency. The components are selected from a realistic component library that contains multiple implementations of operators. The key to the constructive heuristic lies in judiciously selecting vertices to be slowed down in each iteration, since slowing dow one vertex may prevent slowing down others due to graph dependencies. Thus, the desirability of slowing down a vertex is evaluated with respect to all the vertices that would be affected by it's slow down. With every vertex is associated a value, called vertex weight which gives a measure of it's desirability or priority in the selection process. The vertex with the highest weight is one that is selected to slow down. This heuristic gives cost-effective results within a small

period of time.

# 1.4 Summary

The chapter described the various iterative techniques for solving combinatorial optimization problems in HLS and their role in design automation. The problem of component selection is one such problem in HLS. The following chapter describes the SE and SA techniques. The solution strategies and the algorithms of SE and SA that were used in solving the problem of component selection and pipelining are described in chapters 3 and 4 respectively. The experimental results are presented in chapter 5 and the conclusions and future work are presented in chapter 6.

# Chapter 2

# Stochastic Evolution and Simulated Annealing

Stochastic Evolution (SE) and Simulated Annealing (SA) are two techniques that can be used to solve a wide range of combinatorial optimization problems. The SA algorithm introduced by Kirkpatrick et al. [11] is an iterative improvement technique for solving combinatorial optimization problems. SE resolves the two main drawbacks of SA. They are:

- An actual implementation of SA requires a careful tuning of some of it's control

parameters to achieve good results and it uses excessive computation time.

- It does not have a suitable stopping criteria [27].

An important factor in obtaining cost-effective designs is the ability to use multiple operator implementations in the data path. Delay paths can then be balanced by using slow components where possible and the faster components only when necessary. For high performance applications such as Digital signal processing (DSP) systems, designers often combine pipelining with the use of a multiple-implementation library so as to satisfy performance requirements at a reasonable cost. In this research SA and SE techniques were used to solve the problems of component selection and pipelining of a DFG to give a cost-effective solution. This chapter gives an introduction to these two techniques.

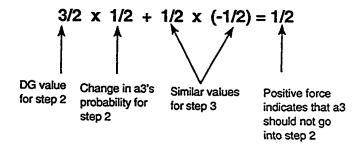

#### 2.1 Stochastic Evolution

The inputs for component selection and pipelining are a set of constraints, a component library, and a DFG. The output is a valid pipelined DFG with components assigned to the nodes and the constraints being satisfied. The relationship of these elements with the stochastic system is shown in Figure 2.1. The stochastic system in our problem is the SE or the SA algorithm. Stochastic evolution is based on the concept of state model [27]. A state model is described as a finite set M of movable elements, a finite set L of locations and the state is defined as  $M \to L$  satisfying certain constraints. The idea behind the SE algorithm is that the suitability of each movable element  $m \in M$  in it's current location S(m) leads to a lower cost of the state S. SE algorithm is a special instance of a more general class of adaptive heuristics by Nahar et. al. [28].

### 2.1.1 Algorithm

The input to SE is an initial state  $S_0$ , an initial value of the control parameter  $p_0$ , and parameter R used in the stopping criterion. The initial state  $S_0$  is a valid

Figure 2.1: HLS system.

#### AIGORITHM SE

```

S = S_0

/* initial state */

S_{Best} = S

/* save initial state */

p=p_0

/* initialize control parameter */

\rho = 0

/* initialize counter */

REPEAT

C_{pre} = COST(S)

S = PERTURB(S, p)

C_{cur} = COST(S)

UPDATE(p, C_{pre}, C_{cur})

IF (COST(S) < COST(S_{Best})) THEN

S_{Best} = S

/* save best state */

\rho = \rho - R

/* decrement counter by R */

ELSE

\rho = \rho + 1

/* increment counter */

ENDIF

UNTIL \rho > R

/* stopping criteria */

RETURN (S_{Best})

/* report best state */

```

Figure 2.2: Stochastic Evolution algorithm.

state satisfying all the constraints specified by the problem under consideration. The initial state is assumed to be the best state on invocation of the algorithm. This algorithm is shown in Figure 2.2. The cost function depends on the type of the problem being solved. In a network bisection problem, cost is the number of hyperedges cut, where as in a traveling salesman problem, it is the sum of the distances covering all the cities.

The SE algorithm retains the state of lowest cost among those produced by the function PERTURB. Each time a state is found which has a lower cost than the best state so far, SE decrements the counter by R. The UPDATE procedure is used to update the control parameter p.

The iteration bound R acts as the expected number of iterations the SE algorithm needs until  $C_{cur} < COST(S_{best})$ , i.e., an improvement in cost takes place. If such an improvement occurs at p < R iterations, then the remaining R - p iterations are added to the next R iterations to be performed. Therefore, if I is the total number of iterations performed by the algorithm, then I/R is the number of improvements encountered. Consequently the quality of the final state obtained increases with the running time of the SE algorithm. If R is set too large, then SE algorithm wastes time during the last set of iterations because it cannot find better states. However if R is chosen too small, the SE algorithm might not have enough time to improve the initial state.

#### 2.1.2 PERTURB

During each call to *PERTURB* the elements are scanned in a particular order. The choice of this ordering is problem specific. The *PERTURB* function is shown in Figure 2.3.

Let  $S: M \to L$  be the existing function that may or may not satisfy the constraints of a state and assume that the cost function has been defined. Let element  $m \in M$ . If a unique move is associated with m from S then it generates a new function  $S': M \to L$  such that  $S'(m) \neq S(m)$ . The move associated with m could itself be a simple move or a compound move depending upon the problem being solved. The gain is calculated as GAIN(m) = COST(S) - COST(S') which gives the change in costs after the move is performed. The function PERTURB stochastically decides whether or not to accept the move associated with the element m

####

Figure 2.3: PERTURB Function.

being scanned with the help of a non-negative control parameter p.

The value of GAIN(m) is compared to an integer r randomly generated in the interval [-p, 0]. If GAIN(m) > r, then the move to S' is accepted, otherwise it-is rejected. If  $r \leq 0$ , moves with positive gains are always accepted. The algorithm then goes on to scan the next element in M. After scanning all the elements of M, the final state is accepted if it satisfies all the constraints. If the state S does not satisfy the constraints then the latest moves are retraced backwards until a state is obtained which satisfies the constraints.

#### 2.1.3 **UPDATE**

The UPDATE function shown in Figure 2.4 is mainly responsible for updating the value of the control parameter p. p is used to determine the range of the negative gains that are to be accepted. This has to be selected carefully. Initially p is set to a non-negative value close to zero. Such a choice for p means that only moves

Procedure UPDATE(p,  $C_{pre}$ ,  $C_{cur}$ )

IF  $(C_{pre} = C_{cur})$  THEN p = f(p)ELSE  $p = p_0$ ENDIF

Figure 2.4: UPDATE procedure.

with small negative gains are accepted. The value of p is increased only when costs for two consecutive iterations are the same. If both the costs are same, then p is increased to a new value  $f(p) \geq p$ . f(p) is obtained by increasing p by a certain positive value. The value that is added to p depends on the type of the problem being solved. The value is chosen such that a cost effective solution is obtained. Otherwise p is reset to it's initial value. The parameter p is increased to give the algorithm a chance to escape a local minimum via an uphill climb. Depending on the problem more than one control parameter may be used.

# 2.1.4 Issues Concerning Stochastic Evolution Algorithm

The successful implementation of SE to achieve cost-effective results is based on four factors.

- 1. An appropriate modeling of the state of the problem.

- 2. The notion of the move to be associated with the "movable" elements of the state has to be carefully designed.

- 3. An initial value of the control parameter p and a method for updating it has to be devised.

- 4. A value for the stopping criterion parameter R.

The above issues are interrelated and depend on the problem as well. The basic requirement is a good representation of the given problem. This enables in designing effective and efficient strategies. The move strategy inturn depends on the problem. The choice of parameter p and it's update method depends on the moves adopted. The choice of stopping criteria depends on the second, third and the fourth choices. In the state model, if the moves and the control parameter p are appropriately chosen then a near optimal solution could be obtained.

# 2.2 Simulated Annealing

Simulated annealing is a technique for solving combinatorial optimization problems [11, 28, 29]. It is not an algorithm with a prescribed sequence of operations to solve a problem but a paradigm for constructing algorithms to solve optimization problems of a particular character. It belongs to a class of iterative improvement schemes. It has been applied to several combinatorial optimization problems from various fields like traveling salesman problem, graph partitioning, quadratic assignment, matching, linear arrangement and scheduling [30]. Resource constraint problems [31] have also been solved using SA. In the areas of engineering, simulated annealing has been applied to VLSI design [1] (placement [32, 33], routing [34]), image processing, code design, facilities layout, network topology design etc.

#### 2.2.1 Background

Simulated annealing was derived using an analogy between the physical annealing process of the solids and combinatorial problems. The term annealing refers to heating a solid to a very high temperature and then slowly cooling the molten material in a controlled manner until it crystallizes [1, 35].

A combinatorial optimization problem is one in which we seek to find some configuration of parameters  $\bar{X} = (X_1, X_2, X_3, \dots, X_n)$  that minimizes some function  $f(\bar{X})$ . This function is usually referred to as the cost or objective function. The objective function is a measure of goodness of a particular configuration of parameters. Realistic design problems may require many parameters and a complex cost function. Consider for example, deciding the placement of components on a surface of an integrated circuit in an optimal way. We may seek to maximize the ability to route wires to interconnect these components [34, 36], minimize the overall chip area, minimize the manufacturing yield of the chip, minimize the deviation from specified timing constraints and so forth. The cost function for such a problem may be very sophisticated with a large number of parameters.

Iterative strategies attempt to perturb some existing suboptimal solution in the direction of a better, lower cost solution. An obvious approach is to explore easily reachable neighboring configurations and to select the one with the least cost, i.e., the one giving the most improvement. In practice the current solution is randomly perturbed. This process is continued until no further improvements are obtained, at which point the process terminates. In such iterative techniques improvement is only downhill and the solution gets stuck in a local minima [35]. In order to overcome this,

random initial configurations can be tried, improving each one of them and using the best answer. However, for very large problems, the computational expense is high, the number of random starts needed to adequately sample the cost surface is unreasonable, and still there is no guarantee of finding a good solution.

Simulated annealing offers a strategy very similar to iterative improvement, with one major difference that annealing allows perturbations to move uphill in a controlled fashion. Because each move can transform one configuration into a worse configuration, it is possible to jump out of a local minima and potentially fall into a downhill path. Designing an annealing algorithm for a problem consists of five major parts:

- 1. Configuration Space: The set of allowed configurations of the system must facilitate easy representation of each state and easy generation of perturbations.

- 2. Move Set: The set of feasible moves (eg., pair swaps) must be rich enough so that all reasonable solutions can be found by applying a sequence of moves from this set. In addition, these moves must be relatively inexpensive to compute, since a large number of moves will be used.

- 3. Cost Metric: The metric must be incrementally computable so that the time to evaluate each move is minimal.

- 4. Annealing Schedule: The manner in which the temperature T is lowered during annealing, also known as the temperature schedule is crucial. Starting too cold, stopping too hot, or cooling too quickly all produce suboptimal

```

Algorithm Simulated_annealing(S_0, T_0, \alpha, \beta, M, Maxtime)

/* S_0 is the initial solution */

/*T_0 is the initial temperature */

/* \alpha is the cooling rate (a constant) */

/* \beta a constant */

/* M represents the time until the next parameter is updated */

/* Maxtime is the total allowed time for the annealing process */

BEGIN

T=T_0

S_c = S_0

Time = 0

REPEAT

Call Metropolis(S_c, T, M)

Time = Time + M

T = \alpha * T

M = \beta * M

UNTIL (Time \geq Maxtime)

Output best solution

END

```

Figure 2.5: Simulated Annealing algorithm.

solutions. Starting too hot or cooling too slowly wastes CPU time [1].

5. Data Structures: The ability to propose and evaluate moves efficiently hinges on a good representation for the basic objects in the problem.

Although the simulated annealing framework is conceptually straightforward, design of a successful annealing-based algorithm involves considerable engineering judgement in the process of designing the five components described.

# 2.3 Algorithm

The core of the simulated annealing algorithm shown in Figure 2.5 is the *Metropolis* procedure, which simulates the annealing process at a given temperature T [37]. The procedure *Metropolis* is named after the scientist who devised a similar scheme to simulate a collection of atoms in equilibrium at a given temperature.

Simulated annealing procedure starts with a initial solution  $S_0$ , initial temperature  $T_0$ , cooling rate  $\alpha$ , a constant  $\beta$  which controls the time spent in annealing at a particular temperature, and *Maxtime* which is the total time allowed for the annealing process and M that represents the time until the next parameter is updated.

The Metropolis procedure shown in Figure 2.6 receives as input the current temperature T, and the current solution  $S_c$  which it improves through local search. Metropolis is also provided with the value M, which is the amount of time for which annealing must be applied at a temperature T. The procedure simulated annealing simply invokes Metropolis at decreasing temperatures. Temperature is initialized to a value  $T_0$  at the beginning of the procedure, and is slowly reduced in a geometric progression; the parameter  $\alpha$  is used to achieve cooling. The amount of time spent in annealing at a temperature is gradually increased as temperature is lowered [11]. This is done using the parameter  $\beta > 1$ . The variable Time keeps track of the time being expended in each call to the Metropolis. The annealing procedure halts when Time exceeds the allowed time.

In simulated annealing the current state is disturbed to obtain a neighboring state. The neighboring state may be obtained by performing a random perturbation,

```

Algorithm Metropolis(S_c, T, M)

BEGIN

REPEAT

S_n = \text{neighbor}(S_c)

\Delta c = (cost(S_n) - cost(S_c))

IF ((\Delta c < 0) \text{ or } (random < e^{-\Delta c/T})) THEN

S_c = S_n; /* accept the solution */

M = M - 1

UNTIL (M = 0)

```

Figure 2.6: Metropolis Procedure.

such as moving a component or part to a new location or replacing a component or a part by another one. After obtaining a new state the cost of the state is computed. If the cost of the new solution  $S_n$  is better then the cost of the current solution  $S_c$ , then the new solution is accepted and  $S_c$  is set to  $S_n$ . If the new solution has a higher cost in comparison to the original solution  $S_c$ , Metropolis will accept the new solution on a probabilistic basis. This is to accept uphill moves. At higher temperatures the probability of large uphill moves is high and at lower temperatures the probability is small. If this random number is smaller than  $e^{-\Delta c/T}$ , where  $\Delta c$  is the difference in costs,  $(\Delta c = c(S_n) - c(S_c))$ , and T is the temperature, the uphill solution is accepted. The probability that an inferior solution is accepted is given by  $P(random < e^{-\Delta c/T})$ . The random number generation is assumed to follow a uniform distribution. At very high temperatures, (when  $T \to \infty$ ),  $e^{-\Delta c/T} = 1$ , and hence the above probability approaches 1. When  $T \to 0$ , the probability  $e^{-\Delta c/T}$  falls to zero [1].

# 2.4 Problem-specific decisions

The problem-specific decisions are concerned with the neighborhood structure and the cost function. These have a significant effect on the success of an annealing algorithm. As with generic decisions, it is not always possible to set down a series of rules which will define the best choices for a given problem. However, it is possible to outline some properties which are desirable. In making decisions about these factors, two important objectives have to be considered.

- The validity of the algorithm is to be maintained.

- The computation time should be used effectively for as many iterations as possible.

If the available computing time is to be used efficiently, it is vital that frequently used routines should be as fast as possible. Generations of the neighborhood solutions must be done in an efficient manner such that it does not consume much time. It is sometimes complex if the neighborhood is large or if the solution space is constrained by stringent feasibility conditions. As the cost function has to be calculated between two states after every iteration, it is important that the cost function and the neighborhood structure be chosen in such a way that this calculation can be carried out quickly and efficiently. It is often the case that it does not necessitate recalculation of the complete cost function for the new solution, and such shortcuts should be considered when deciding on the forms of the costs and the neighborhood.

If the number of iterations are to be kept reasonably low, it is necessary to avoid neighborhoods which give rise to a spiky topography over the solution space. The

number of iterations that have to be carried out to obtain an optimal solution also depends on the size of the solution space. If the solution space is smaller, optimal solution can be obtained in lesser number of iterations. If the solution space is large, it is necessary to reduce the size of the solution space by eliminating part of the solution space based on certain criteria. This in turn is specific to a given problem. In addition to keeping the solution space small, it is also useful to aim for reasonably small neighborhoods. This enables a neighborhood to be searched adequately in fewer iterations, but conversely means that there is less opportunity for dramatic improvements to occur in a single move. But all the conditions cannot be satisfied for a given problem, therefore compromises have to be made.

# 2.5 Summary

This chapter described the SE and the SA techniques. The various strategies that were used to perturb the states have been described. The acceptance criteria for both the techniques has also been discussed. The next chapter describes the application of SE technique for component selection and pipelining.

# Chapter 3

# Component Selection and

# Pipelining using Stochastic

# **Evolution**

This chapter describes the application of Stochastic Evolution (SE) technique for component selection and pipelining. The inputs for this problem are a Data Flow graph (DFG), a multiple-component library and constraints. A DFG consists of vertices that represents operators and edges that show the interrelationship between the vertices. Each DFG consists of a set of inputs and a set of outputs. Mapping components from a realistic component library (CL) on to the vertices of the DFG is component selection. Pipelining involves placing registers on the DFG such that PS delay constraint is satisfied, i.e., delay between any two consecutive registers in the DFG should not exceed the specified PS delay. To design the problem of component selection and pipelining using the SE technique the following issues have

#### to be addressed:

- Designing an initial representation of the solution.

- Determining the cost function.

- Designing appropriate perturb strategies.

- Defining appropriate acceptance criteria.

A careful design of these critical parts results in obtaining a cost-optimal solution. This chapter describes the various design issues that were considered and the effect of each one of them.

## 3.1 Initial Solution Representation

A DFG(V, E) consists of a set of vertices V, and a set of directed edges E. Each of the vertices are connected to one or more vertices through edges. In order to keep track of the edges that are coming into a particular vertex and going out of the vertex, i.e., the sum of the indegree and outdegree of the vertex, all the possible paths between the inputs and the outputs were stored. This type of representation of the DFG keeps track of the successors and the predecessors of all the vertices in the DFG. This design method helps in calculating the cost easily and efficiently and also determines whether the current state satisfies the PS delay and latency constraints which is explained in detail in later sections.

Each of the vertices is assigned a unique number. If the DFG consists of n vertices then the vertices are labeled 1 through n. Apart from containing the unique

ID number each vertex also stores the information about the component type, component name, delay, and the cost in terms of the number of gates. The realistic CL that is considered is shown in Table 3.1. The CL consists of eight different types of multipliers and six different types of adders and subtractors. The various fields of each component of the CL includes component type, component name, delay in ns and cost in terms of the number of gates.

PS delay and latency are also given as inputs along with the DFG. Any initial representation of the solution should be a valid initial solution. A solution is said to be valid if its latency of the initial solution is less than or equal to the given latency and the delay of each of the components mapped onto the DFG is less than or equal to the specified PS delay. It is necessary to start with a valid initial solution because in the worst case, when repeated perturbations of the current state does not produce a valid solution, then, the initial solution will be the best solution. If an invalid initial solution is used then the final solution that is obtained may not be a valid solution. The initial solution consisted of mapping the fastest components onto the DFG. In this method components with the smallest delays were mapped onto the DFG. The multipliers corresponding to the Mpy8 and adders/subtractors corresponding to Add6/Sub6 of the CL shown in Table 3.1 were used. As the components with the smallest delays have the highest cost (in terms of number of gates), the initial solution will start with the highest cost and lowest latency. The advantage of using this method is that we always start with a valid initial solution satisfying the constraints of PS delay and the latency. The initial solution also consists of pipelining the DFG. This is done by traversing the DFG from the inputs towards the output. The delays of each of the components is accumulated. At the

| Commonant | C                  | D.1   | <u> </u> |

|-----------|--------------------|-------|----------|

| Component | Component          | Delay | Cost     |

| types     | Name               | (ns)  | (Gates)  |

| *         | Mpy1               | 57.97 | 2368     |

|           |                    |       |          |

| *         | Mpy2               | 44.21 | 2400     |

|           | • • · ·            |       |          |

| *         | Mpy3               | 36.21 | 2600     |

| -         | 2.225              | 00.51 | 2000     |

| *         | Mpy4               | 32.98 | 2710     |

| *         | Mpy4               | 32.30 | 2110     |

|           | 36                 | 00 57 | 0070     |

| *         | Mpy5               | 28.57 | 2978     |

|           |                    |       |          |

| *         | Mpy6               | 25.00 | 3500     |

|           |                    |       |          |

| *         | Mpy7               | 22.00 | 4000     |

|           | l '                |       |          |

| *         | Mpy8               | 20.50 | 4500     |

| +/-       | Add1/Sub1          | 25.80 | 62       |

| i         | <i>'</i>           |       |          |

| +/-       | Add2/Sub2          | 20.00 | 125      |

| .,        |                    | -0.00 |          |

| +/-       | Add3/Sub3          | 13.50 | 187      |

| 17-       | Addoysubo          | 13.50 | 101      |

| ,,        | A 3 3 4 / C - 1- 4 | 10.00 | 950      |

| +/-       | Add4/Sub4          | 10.00 | 250      |

|           | 1                  |       |          |

| +/-       | Add5/Sub5          | 5.50  | 375      |

|           |                    |       |          |

| +/-       | Add6/Sub6          | 3.00  | 500      |

| Register  | Reg                |       | 200      |

Table 3.1: Component Library.

point where the accumulated cost exceeds the specified *PS* delay a register is placed. Therefore the combined delay of the components between two successive registers is less than or equal to the *PS* delay.