## Architectures for Arithmetic Operations in Galois Fields $GF(2^m)$

by

#### Mohamed Ahsan

A Thesis Presented to the

FACULTY OF THE COLLEGE OF GRADUATE STUDIES

KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

**MASTER OF SCIENCE**

In

**ELECTRICAL ENGINEERING**

June, 1995

**INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI

films the text directly from the original or copy submitted. Thus, some

thesis and dissertation copies are in typewriter face, while others may be

from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the

copy submitted. Broken or indistinct print, colored or poor quality

illustrations and photographs, print bleedthrough, substandard margins,

and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete

manuscript and there are missing pages, these will be noted. Also, if

unauthorized copyright material had to be removed, a note will indicate

the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by

sectioning the original, beginning at the upper left-hand corner and

continuing from left to right in equal sections with small overlaps. Each

original is also photographed in one exposure and is included in reduced

form at the back of the book.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white

photographic prints are available for any photographs or illustrations

appearing in this copy for an additional charge. Contact UMI directly to

order.

IIMI

A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor MI 48106-1346 USA 313/761-4700 800/521-0600

# Architectures for Arithmetic Operations in Galois Fields $GF(2^m)$

Mohamed Ahsan

A Thesis Presented to the FACULTY OF THE COLLEGE OF GRADUATE STUDIES

KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARAB!A

In Partial Fulfillment of the Requirements for the Degree of

MASTER OF SCIENCE In

**Electrical Engineering**

June 1995

UMI Number: 1378712

UMI Microform 1378712 Copyright 1996, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

300 North Zeeb Road Ann Arbor, MI 48103

## ARCHITECTURES FOR ARITHMETIC OPERATIONS IN GALOIS FIELDS $GF(2^m)$

MS Thesis

$\mathbf{B}\mathbf{y}$

Mohamed Ahsan

June, 1995

## KING FAHD UNIVERSITY OF PETROLEUM AND MINERALS DHAHRAN, SAUDI ARABIA **COLLEGE OF GRADUATE STUDIES**

This thesis, written by

#### Mohamed Ahsan

under the direction of his Thesis Advisor, and approved by his Thesis committee, has been presented to and accepted by the Dean, College of Graduate Studies, in partial fulfillment of the requirements for the degree of

## MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

Thesis Committee:

Dr. Gerhard F. Beckhoff (Chairman)

Dr. Khalid Hussain Biyari (Member)

Dr. Essam E. M. Hassan (Member)

Dr. Baher Hussein (Member)

Dr. S. Z. Al-Akhdhar (Member)

Dr. Abdallah M . Al-Shehri Department Chairman

Dr. Ala H. Rabeh

Dean, College of Graduate Studies

30-10-1

Date:

#### Dedicated to

my Parents and

my Wife

$whose\ prayers,\ inspiration\ and\ love\ led\ to\ this$  accomplishment

#### Acknowledgment

I would like to express my sincere appreciation to the following, whose support has been invaluable in the completion of this work

To Dr. G. F. Beckhoff, my thesis advisor; his very presence has been like the proverbial sun, and the constant encouragement and able guidance right through the course of this work has been tremendous, for which I am extremely indebted.

For having spared the time and effort in critically reviewing this work, I thank my committee members, Dr. Khalid Hussain Biyari, Dr. Baher Hussein, Dr. Essam Hassan and Dr. S. Z. Al-Akhdhar.

To all my friends and colleagues at KFUPM: their support and company made my stay infinitely enjoyable, which is gratefully acknowledged.

And lastly a word of grateful thanks to my parents, my wife, my sisters and my brother-in-law who never shackled my freedom and have always allowed me the ultimate discretion in pursuing my options.

## Contents

|   | List | of Tal  | oles                      | V  |

|---|------|---------|---------------------------|----|

|   | List | of Fig  | gures                     | vi |

|   | Abs  | tract ( | English)                  | ix |

|   | Abs  | tract ( | Arabic)                   | х  |

| 1 | Intr | oducti  | on                        | 1  |

|   | 1.1  | Binary  | Extension Fields          | 1  |

|   | 1.2  | Bases   | of $GF(2^m)$ over $GF(2)$ | 9  |

|   |      | 1.2.1   | Standard Basis            | Ç  |

|   |      | 1.2.2   | Normal Basis              | 1( |

|   | 1.3  | Systol  | ic Arrays                 | 10 |

|   |      | 1.3.1   | Parallelism               | 11 |

|   |      | 1.3.2   | The Locality Principle    | 11 |

|   |      | 1.3.3   | The Systolic Model        | 12 |

|   | 1.4 | Literat | ture Review                                                  | 14 |

|---|-----|---------|--------------------------------------------------------------|----|

| 2 | Arc | hitectu | res Using Linear Shift Register Circuits                     | 17 |

|   | 2.1 | Linear  | Switching Circuits                                           | 17 |

|   | 2.2 | Adder   | s for $GF(2^m)$                                              | 19 |

|   | 2.3 | Multip  | oliers for $GF(2^m)$                                         | 21 |

|   |     | 2.3.1   | Multiplication of a Field Element by a Fixed Field Element . | 21 |

|   |     | 2.3.2   | Multiplication of any Polynomial by a Fixed Polynomial       | 23 |

|   |     | 2.3.3   | Two Input Multiplier                                         | 27 |

|   |     | 2.3.4   | Proposed Serial Modified Massey-Omura Multiplier             | 29 |

|   | 2.4 | Divide  | ers for $GF(2^m)$                                            | 43 |

|   | 2.5 | Applio  | cations: Recd-Solomon (RS) Codes                             | 48 |

|   |     | 2.5.1   | Preliminaries                                                | 48 |

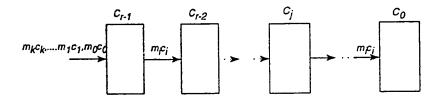

|   |     | 2.5.2   | Systematic Encoding of RS Codes                              | 49 |

|   |     | 2.5.3   | Decoding of RS Codes                                         | 53 |

| 3 | Arc | hitect  | ures Using Systolic Arrays                                   | 63 |

|   | 3.1 | Multi   | pliers for $GF(2^m)$                                         | 63 |

|   |     | 3.1.1   | Parallel-In-Parallel-Out Systolic (PIPOS) Array              | 64 |

|   |     | 3.1.2   | Serial-In Serial-Out Systolic (SISOS) Array                  | 67 |

|   |     | 3.1.3   | Conclusions                                                  | 69 |

|   | 3.2 | Stand   | ard Basis Inversion and Division                             | 69 |

|     | 3.2.1   | An Algorithm for Computing $A^{-1}$ and $B\cdot A^{-1}$ in $GF(2^m)$ | 69 |  |

|-----|---------|----------------------------------------------------------------------|----|--|

|     | 3.2.2   | The Gauss-Jordan Algorithm                                           | 72 |  |

|     | 3.2.3   | Systolic Array Implementation of the Gauss-Jordon Algorithm          |    |  |

|     |         | over $GF(2^m)$                                                       | 75 |  |

| 3.3 | Applio  | cation: Encoding of Reed-Solomon Codes                               | 79 |  |

|     | 3.3.1   | Nonsystematic Encoder                                                | 79 |  |

|     | 3.3.2   | Systematic Encoder                                                   | 81 |  |

|     | 3.3.3   | Conclusions                                                          | 96 |  |

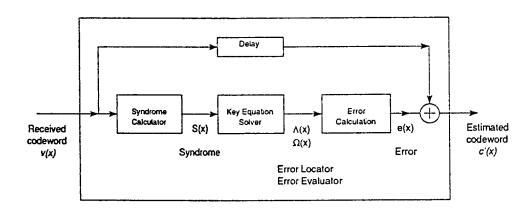

| 3.4 | Applie  | cation: Decoding of Reed-Solomon Codes                               | 96 |  |

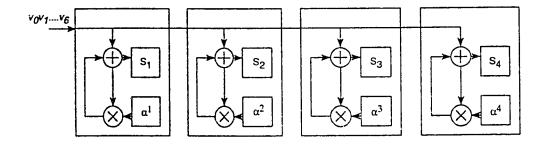

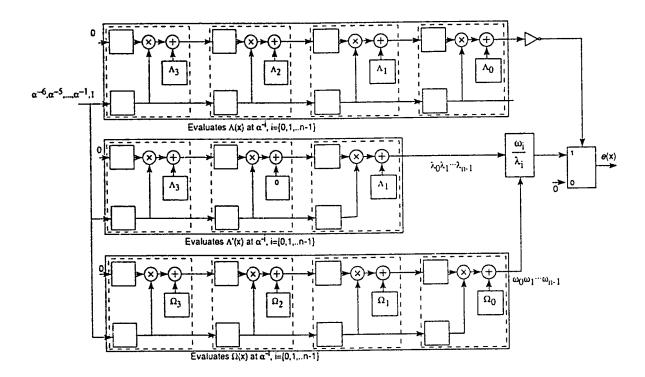

|     | 3.4.1   | Syndrome Calculation                                                 | 98 |  |

|     | 3.4.2   | Key Equation Solver                                                  | 00 |  |

|     | 3.4.3   | Error Calculation                                                    | 08 |  |

|     | 3.4.4   | Error Correction                                                     | 14 |  |

|     | 3.4.5   | Exceptional Errors                                                   | 14 |  |

|     | 3.4.6   | Conclusions                                                          | 15 |  |

| Bib | oliogra | phy 1                                                                | 15 |  |

| Αp  | pendix  | 1                                                                    | 21 |  |

| Vit | ae      | Vitae 121                                                            |    |  |

## List of Tables

| 1.1 | Representation of elements of $GF(2^3)$                             | 5  |

|-----|---------------------------------------------------------------------|----|

| 1.2 | Examples of $m$                                                     | 8  |

| 2.1 | Comparison of Normal basis multipliers generated by the irreducible |    |

|     | AOP of degree $m$                                                   | 39 |

| 2.2 | Parameters of the proposed serial multiplier                        | 44 |

| 2.3 | Error Trapping Example                                              | 62 |

| 3.1 | Operating modes of the main array cell                              | 77 |

## List of Figures

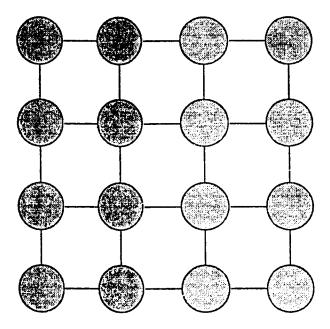

| 1.1  | Locally connected network of processors                                       | 13 |

|------|-------------------------------------------------------------------------------|----|

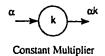

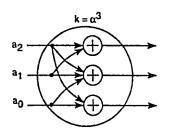

| 2.1  | The building blocks for linear switching circuits                             | 18 |

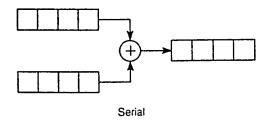

| 2.2  | Addition of two field elements of $GF(2^4)$                                   | 20 |

| 2.3  | Serial multiplication implementation of $\alpha \cdot \beta$                  | 22 |

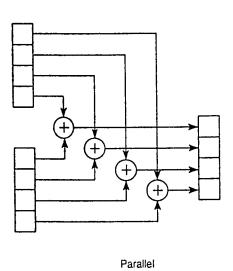

| 2.4  | Parallel multiplication implementation of $\alpha \cdot \beta$                | 24 |

| 2.5  | Parallel multiplication implementation of $\alpha^3 \cdot \beta$              | 25 |

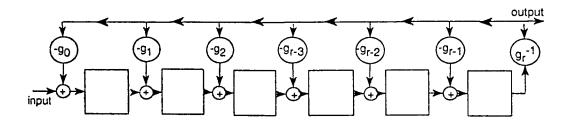

| 2.6  | Shift Register Circuits for multiplying polynomials                           | 26 |

| 2.7  | A two input multiplier                                                        | 28 |

| 2.8  | A two input multiplier with $h(x) = x^3 + x + 1$ and $k(x) = x^2 + x + 1$ .   | 30 |

| 2.9  | A structure for the Massey-Omura parallel multiplier over $GF(2^4)$           | 33 |

| 2.10 | A structure for the modified Massey-Omura parallel multiplier over            |    |

|      | $GF(2^4)$ generated by irreducible all one polynomial of degree $m.\ .\ .\ .$ | 37 |

| 2.11 | Circuit diagram of $B_1$ and $B_2$ of the modified Massey-Omura multiplier.   | 41 |

| 2.12 | Proposed serial implementation of the normal basis multiplier                 | 42 |

|      |                                                                             | vii |

|------|-----------------------------------------------------------------------------|-----|

| 2.13 | A circuit for dividing polynomials                                          | 45  |

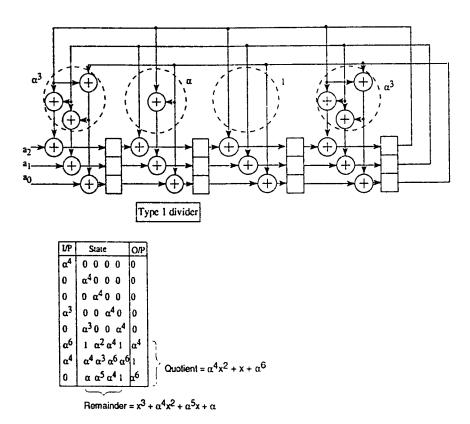

| 2.14 | Type 1 circuit for dividing polynomials                                     | 46  |

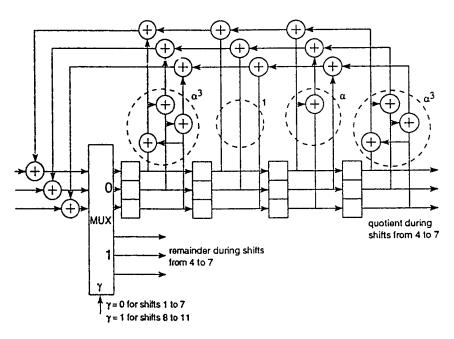

| 2.15 | Type 2 circuit for dividing polynomials                                     | 47  |

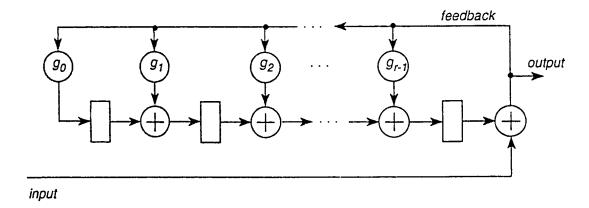

| 2.16 | An (n-k)-stage feedback shift register encoding circuit                     | 52  |

| 2.17 | Encoder for the RS (7,3) code using binary logic elements                   | 54  |

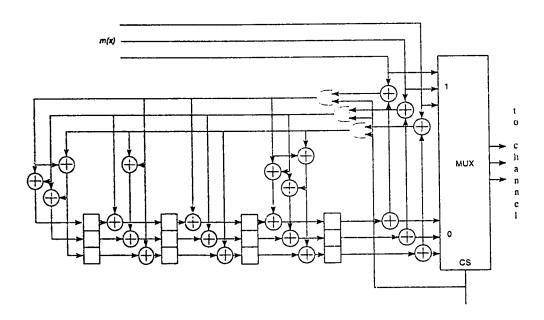

| 2.18 | Pipelined LFSR encoder                                                      | 55  |

| 2.19 | Syndrome Calculator for the RS (7,3) code                                   | 58  |

| 2.20 | Pipelined decoder for the RS (7,3) code                                     | 60  |

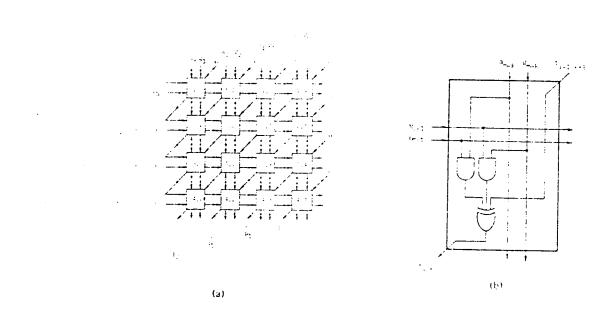

| 3.1  | (a) Parallel-in-parallel-out bit-level systolic array for multiplication    |     |

|      | in $GF(2^4)$ . (b) Circuit of the $(i,k)$ cell in part $(a),\ldots,\ldots$  | 66  |

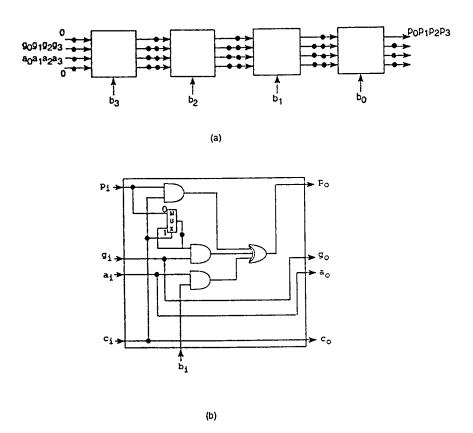

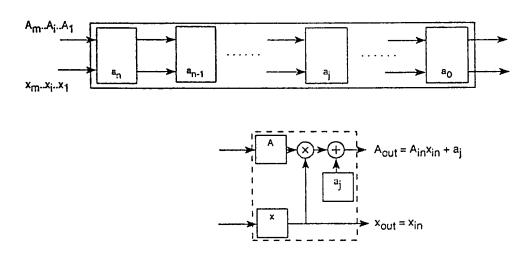

| 3.2  | (a) A serial-in-serial-out systolic array for multiplication in $GF(2^4)$ . |     |

|      | The result $p_j$ will appear after $a_j$ passes through the array. (b) The  |     |

|      | circuit of each basic cell in (a)                                           | 68  |

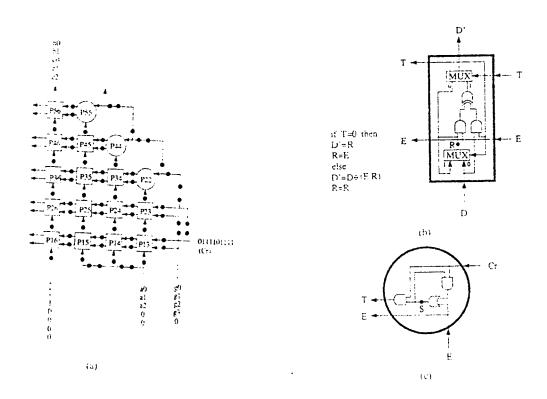

| 3.3  | (a) Systolic array for inversion in $GF(2^3)$ (b) main array cell (c)       |     |

|      | boundary cell                                                               | 76  |

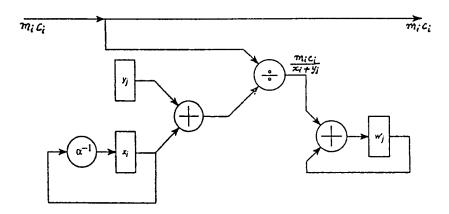

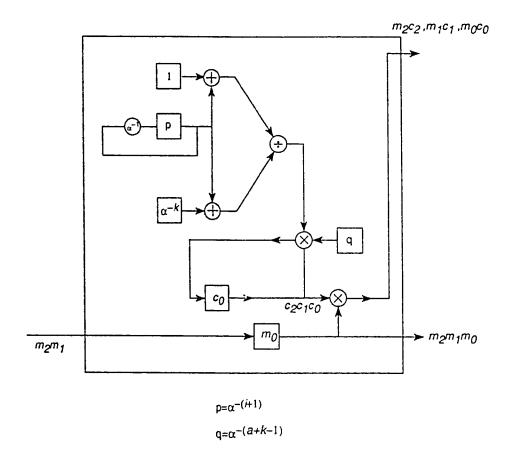

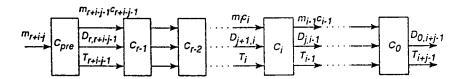

| 3.4  | Cauchy cell $C_j$ -basic computation                                        | 85  |

| 3.5  | Basic Cauchy Encoder                                                        | 86  |

| 3.6  | Cell $C_{pre}$ for the (7,3) RS code                                        | 88  |

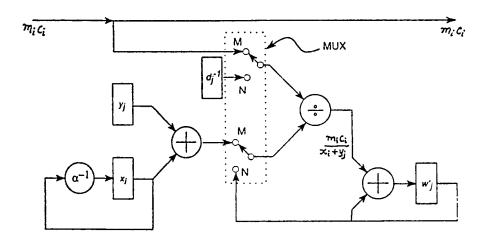

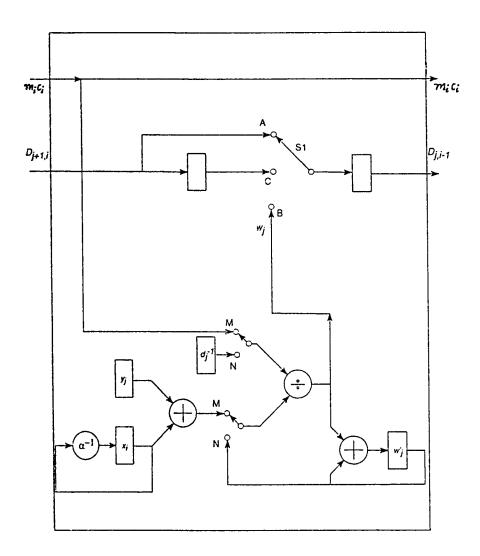

| 3.7  | Cell $C_j$                                                                  | 90  |

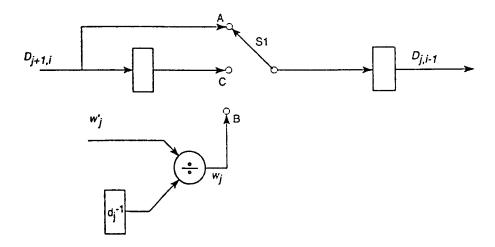

| 3.8  | Output stream circuitry for cell $C_j$                                      | 91  |

#### Abstract

Name:

Mohamed Ahsan

Title:

Architectures for Arithmetic Operations in

Galois Fields  $GF(2^m)$

Major Field:

Electrical Engineering

Date of Degree: June, 1995

Galois fields are used in numerous applications like Reed-Solomon (RS) codes, digital signal processing (DSP) and cryptology. There is a need for efficient multiplication and division methods that can be easily realised on VLSI chips. Massey and Omura have recently developed a new multiplication algorithm for Galois fields based on the normal basis representation. A new bit-scrial modified Massey-Omura multiplier is developed in this thesis to compute multiplications over  $GF(2^m)$  In contrast to the existing multipliers, this new multiplier requires the minimum chip area. A serial-in serial-out systolic array is presented for performing element inversion with standard basis represented. The architecture is highly regular, modular and nearest neighbour connected.

Furthermore, a systolic architecture for an RS encoder, based on Cauchy representation of generator matrix of the code, is presented, consisting of r+1 cells, where r is the redundancy of the code. This encoder is systematic, does not require any feedback or other global signals. Its cells are of low complexity and it is easily reconfigurable for variable redundancy and changes in the choice of the generator polynomial of the code, the architecture is suitable for very high-speed applications.

Finally, a systolic array of an RS decoder, is presented. Systolic array architectures are derived for the various steps including syndrome calculation, key equation solution and error evaluation. The improvements over existing systolic implementations are discussed.

Master of Science Degree

King Fahd University of Petroleum and Minerals

Dhahran, Saudi Arabia

June 1995

#### ملخص البحث

الاسم :- محمد إحسان.

عنوان البحث: - بناء العمليات الحسابية في حقل جالو (CF (2<sup>m</sup>)

التخصص :- هندسة كمربائية

تاريخ الدرجة ،- يونيـــو ١٩٩٥ م.

حقل جالو يستعمل في كثير من التطبيقات ، مثل " ريدسالو من كود " ، وفي معالجة الموجات الرقمية والتشفير السري . هناك حاجة إلى وجود طرق فعالة للضرب والقسمة والتي يمكن من خلالما تنفيذها بسهولة على شرائح " VLSI " . ماسي وأومرا طورا طريقة جديدة للضرب الحسابي لحقل جالو اعتماداً على تمثيل " نورمل Normal " . تحسين ضاربة ماسي - أومرا المتوالية وضحت في هذه الرسالة لحساب عمليات الضرب على حقل جالو . في المقابل للضاربة الموجودة ، هذه الضاربة الجديدة تحتاج إلى أقل مساحة من الشرائح . مصفوفة سستوليك المتوالية عرضت لعمل العنصر المعوكس مع تمثيل "ستاندرد Standard " الأساسي . هذا البناء منتظم جداً وتكراري ومتصل لأقرب جار .

بالإضافة إلى ذلك ، بناء سستوليك لمشفرة ريد سالومن تعتمد على تمثيل كوشي للمصفوفة المولدة المشفرة . هذه المشفرة تحتوي على (ر+۱) خلية ، حيث "ر" هو الزائد من الشفرة .

المشفرة منتظمة ولا تحتاج لأي تغذية إسترجاعية . خلاياها تكون باقل تعقيد وسهولة في إعادة تشكيل المجهول الزائد . وتغيير اختيار متعددة الحدود المولدة للشفرة .

هذا البناء مناسب للتطبيقات السريعة جدأ.

أخيراً ، مصفوفة سستوليك لحل الشفرة عرضت في هذه الرسالة . بناء مصفوفة سستوليك اشتقت لخطوات متعددة متضمنة حساب " سيندروم " ، حل معادلة المفتاح ، وتقبيم الخطا . التحسين على تنفيذ سستوليك الموجود نوقش في هذه الرسالة .

## Chapter 1

### Introduction

Finite or Galois fields are important in many applications, such as error-correcting codes [1, 2, 3], switching theory [4], cryptography [5] and digital signal processing [6].

#### 1.1 Binary Extension Fields

Galois field  $GF(2^m)$  is a number system consisting of  $2^m$  elements, where each element is represented as a vector of m bits. When considered from the hardware point of view, the field  $GF(2^m)$  is of particular interest for computer applications. In particular, for digital computers and digital data transmission usually two symbols, 0 and 1 are used. Therefore, in the following text only  $GF(2^m)$  fields are considered, for which addition and multiplication are defined as follows:

The addition and multiplication defined above are called modulo-2 addition and multiplication respectively. It should be noted that 1 = -1 since 1 + 1 = 0. The alphabet of two symbols, 0 and 1, together with modulo-2 addition and multiplication is called a field of two elements (or a binary field), which is usually denoted by GF(2).

**Definition 1.1** Consider a polynomial F(x), with one indeterminate x and with coefficients from any field F:

$$F(x) = f_0 + f_1 x + f_2 x^2 + \cdots + f_n x^n.$$

The degree of a polynomial is the largest power of x in a term with a nonzero coefficient. The degree of the 0 polynomial is 0.

**Definition 1.2** A polynomial is called monic if the coefficient of the highest power of x is 1. Polynomials can be added and multiplied in the usual way, and they form a ring.

**Definition 1.3** A polynomial of degree n which is not divisible by any polynomial of degree less than n but is greater than 0 is called irreducible.

**Definition 1.4** The greatest common divisor of two polynomial is a monic polynomial of greatest degree which divides both of them. Two polynomials are said to be relatively prime if their greatest common divisor is 1.

Consider computations with polynomials whose coefficients are either 0 or 1. For real numbers, if  $\lambda$  is a root of the polynomial f(x) (that is,  $f(\lambda) = 0$ ), f(x) is divisible by  $x - \lambda$ . This is still true for f(x) with binary coefficients. The only polynomials of degree 1 are x and x + 1. The only polynomials of degree 2 are  $x^2$ ,  $x^2 + x$ ,  $x^2 + 1$  and  $x^2 + x + 1$ . Of these polynomials of degree 2,  $x^2$  and  $x^2 + x$  factor in an obvious way. Since  $1^2 + 1 = 0$ ,  $x^2 + 1$  must be divisible by x + 1. In fact,  $(x+1)^2 = x^2 + x + x + 1 = x^2 + 1$ . However,  $x^2 + x + 1$  does not have 0 or 1 as roots and so is not divisible by any polynomial except 1 and itself. A polynomial F(x) of degree m is said to be *irreducible* over a binary field GF(2) if F(x) is not divisible by any polynomial of degree less than m and greater than zero. It can be proved that  $x^4 + x + 1$  is irreducible by noting that if it is not irreducible, then there must be irreducible factor of degree equal to or less than 2. Since 0 or 1 are not roots, x and x + 1 are not factors. The only remaining possibility is  $x^2 + x + 1$ , it can be verified by long division that  $x^2 + x + 1$  is not divisible by  $x^2 + x + 1$ . Thus,  $x^4 + x + 1$  is irreducible.

Fields with  $2^m$  symbols are called Galois fields, and they are denoted by  $GF(2^m)$ . They are important in the study of cyclic codes. In particular, they are used in decoding BCH codes and as symbols in Reed - Solomon codes. **Definition 1.5** In general, in any GF(q), there is primitive element  $\alpha$ , that is, an element of order q-1. Every nonzero element of GF(q) can be expressed as a power of  $\alpha$ ; i.e., the multiplicative group of GF(q) is cyclic.

**Definition 1.6** An irreducible polynomial of degree m over GF(2) is called primitive if it has a primitive element  $\alpha$  from  $GF(2^m)$  as a root. Then this root and hence all the roots (i.e.,  $\alpha$ ,  $\alpha^2$ ,  $\cdots$   $\alpha^{2^{m-1}}$ ) are all primitive.

An arithmetic field with  $2^m$  symbols is derived as follows. First we start with an arithmetic with two symbols and an irreducible polynomial F(x) of degree m over GF(2). Next we introduce a new symbol,  $\alpha$ , and assuming that  $F(\alpha) = 0$ . Then a table of powers of  $\alpha$  is developed. If F(x) is chosen properly, i.e., if it is irreducible in GF(2), then the powers of  $\alpha$  up to  $2^m - 2$  will be different,  $\alpha^{2^m-1} = 1$ , and  $0, 1, \alpha, \alpha^2, \dots, \alpha^{2^m-2}$  will be the set of  $2^m$  field elements. Furthermore, each element can be expressed as a sum of the elements  $1, \alpha, \alpha^2, \dots, \alpha^{m-1}$ . The nonzero elements form a cyclic abelian group under multiplication, a generator of this group is the primitive element of  $GF(2^m)$ . For example, for m=3,  $F(x)=x^3+x+1$  generates the field elements as shown in Table 1.1.

| Exponent                                           | Polynomial              | Binary | Decimal |

|----------------------------------------------------|-------------------------|--------|---------|

| 0                                                  |                         | 000    | 0       |

| $\alpha^0$                                         | 1                       | 001    | 1       |

| $a^1$                                              | a                       | 010    | 2       |

| $\alpha^2$ $\alpha^3$                              | $\alpha^2$              | 100    | 4       |

| $\alpha^3$                                         | a + 1                   | 011    | 3       |

| a <sup>4</sup>                                     | $\alpha^2 + \alpha$     | 110    | 6       |

| α <sup>4</sup><br>α <sup>5</sup><br>α <sup>6</sup> | $\alpha^2 + \alpha + 1$ | 111    | 7       |

| $\alpha^6$                                         | $\alpha^2 + 1$          | 101    | 5       |

Table 1.1: Representation of elements of  $GF(2^3)$

In general, any element of  $GF(2^m)$  whose powers generate all the nonzero elements of  $GF(2^m)$  is said to be primitive. It has been proved that for each positive integer m there exists at least one primitive polynomial of degree m. It is not easy to recognise a primitive polynomial. However, there are tables of polynomials in which primitive polynomials are indicated. A list of primitive polynomials are given in [1].

**Definition 1.7** Let 3 be an arbitrary element of the Galois field  $GF(2^m)$ . The polynomial m(x) of smallest degree with binary coefficients such that  $m(\beta) = 0$  is called the minimal polynomial of  $\beta$ . The minimal polynomial of  $\beta$  is irreducible.

This can be seen as follows: Suppose that m(x) is not irreducible, say  $m(x) = m_1(x)m_2(x)$ , where  $m_1(x)$  and  $m_2(x)$  are nontrivial. Both  $m_1(x)$  and  $m_2(x)$  have degree lower than the degree of m(x). Since  $m(\beta) = m_1(\beta)m_2(\beta) = 0$ , then either  $m_1(\beta)$  or  $m_2(\beta)$  must be zero. This contradicts the hypothesis that m(x) is the polynomial of the smallest degree such that  $m(\beta) = 0$ . Therefore, m(x) cannot have nontrivial factors and it must be irreducible. It has been proved that every element of  $GF(2^m)$  has a minimum polynomial whose degree is m or less. Since  $m(\beta) = 0$  and  $[m(x)]^{2^l} = m(x^{2^l})$ , then

$$[m(\beta)]^{2^{l}} = m(\beta^{2^{l}}) = 0.$$

This is to say that  $\beta^{2^l}$  is also a root of m(x). Consequently,

$$\beta, \beta^2, \beta^{2^2}, \dots, \beta^{2^l}, \dots$$

are all roots of m(x). Since m(x) has finite degree, it must have a finite number of roots. Thus, there must be a repetition in the above sequence. Let e be the degree of m(x). It can be shown that  $\beta, \beta^2, \beta^{2^2}, \dots, \beta^{2^{r-1}}$  are all the distinct roots of m(x). These elements repeat in the sequence after  $\beta^{2^{r-1}}$ .

#### Definition 1.8

#### All-One Polynomial

A polynomial  $p(x) = x^m + x^{m-1} + \dots + x + 1$  over GF(2) is called all one polynomial (AOP) of degree m.

Attention is restricted to AOP's over GF(2) only. An AOP of degree m is irreducible over GF(2) if (m+1) is a prime and 2 is the generator of  $GF^*(m+1)$ , where  $GF^*(m+1)$  is the multiplicative group in GF(m+1). Table 1.2 shows some possible values of m for an AOP of degree m to be irreducible [7]. Irreducible AOPs are special irreducible polynomials, having the following interesting property: Let p(x) be an irreducible AOP of degree m, then the roots  $\{\alpha, \alpha^2, \alpha^{2^2}, \dots, \alpha^{2^{m-1}}\}$ , of p(x) = 0, are linearly independent over GF(2). It should be noted that the set of roots of p(x) = 0 constructs a normal basis [3] over GF(2), where p(x) is an irreducible AOP over GF(2).

| 2   | 28 | 66  | 138 |

|-----|----|-----|-----|

| 4   | 36 | 82  | 148 |

| 10  | 52 | 100 | 162 |

| 12  | 58 | 106 | 172 |

| _18 | 60 | 130 | 178 |

Table 1.2: Examples of m

Arithmetic operations including the ones discussed above can be implemented in software but the speed of computations is not satisfactory. Thus, to achieve a desired rate of output, several dedicated circuits have been proposed. These are linear feedback shift register (LFSR) circuits [1, 2]. Recently many systolic architectures to perform arithmetic computations in  $GF(2^m)$  have been proposed in literature. The purpose of this thesis is to study various arithmetic operations in  $GF(2^m)$  and the possible systolic circuits that implement them. The application of these circuits to encode and decode Reed-Solomon codes is studied.

### **1.2** Bases of $GF(2^m)$ over GF(2)

#### 1.2.1 Standard Basis

$GF(2^m)$  is a vector space of dimension m over the ground field  $GF(2) = \{0,1\}$ . Any set of m linearly independent elements can be used as a basis for this vector space. In constructing  $GF(2^m)$  from a primitive irreducible polynomial F(x), the basis used is  $1, \alpha, \alpha^2, \cdots, \alpha^{m-1}$ , where  $\alpha$  is a root of the primitive irreducible polynomial. This basis is known as the standard basis representation also called as conventional basis representation or polynomial basis representation of field elements. The elements of  $GF(2^m)$  can be represented using the standard basis representation. Any element can be expressed as a polynomial of  $\alpha$  with degree less than m. That is,

$$GF(2^m) = \{a_{m-1}\alpha^{m-1} + \dots + a_1\alpha + a_0 | a_i \in GF(2) \text{ for } 0 \le i \le m-1\}.$$

Table 1.1 demonstrates an example of the standard basis representation of the field elements.

#### 1.2.2 Normal Basis

A normal basis of  $GF(2^m)$  over GF(2) is of the form  $\lambda, \lambda^2, \lambda^{2^2}, \dots, \lambda^{2^{m-1}}$ . It has been proved in [3] that a normal basis exists in any field  $GF(q^m)$  and any field  $GF(q^m)$  contains a primitive element  $\lambda$  such that  $\lambda, \lambda^p, \dots, \lambda^{p^{m-1}}$  is a normal basis. An element  $b \in GF(2^m)$  can be represented in normal basis as

$$b = b_0 \alpha + b_1 \alpha^2 + \dots + b_{m-1} \alpha^{2^{m-1}}.$$

where  $b_i \in GF(2^m)$  ( $0 \le i \le m-1$ ). If m is odd,  $GF(2^m)$  has a self- complementary normal basis,  $GF(2^m)$  contains a primitive element of trace 1 or conversely, according to [8] a necessary and sufficient condition for  $\lambda, \lambda^2, \lambda^{2^2}, \dots, \lambda^{2^{m-1}}$  to be a normal basis of  $GF(2^m)$  is

$$T_m(\lambda) = \lambda + \lambda^2 + \lambda^{2^2} + \dots + \lambda^{2^{m-1}} = 1.$$

This relation implies that the normal basis representation of 1 is (1.1.1....1).

#### 1.3 Systolic Arrays

Systolic arrays are integrated, special purpose processors whose dominant characteristics are:

- massive, decentralised parallelism

- local communication

- synchronous mode of operation.

#### 1.3.1 Parallelism

The concept of parallelism breaks with the classical approach of obtaining speed by performing each operation more rapidly. In parallel computation, the speed increase comes from the simultaneous execution of operations. Multiprocessors are computers which have more than one processor. The architecture of the multiprocessor is more complex than that of the sequential machine: the problems of memory access become crucial because data have to be supplied to processors at the right time; similarly the problems of communication and synchronisation between processors are important.

#### 1.3.2 The Locality Principle

When one tries to make best use of a parallel architecture for executing a preexisting algorithm, the principal problem is that of distributing the algorithm across the processors in such a way that they will be actively engaged in executing the algorithm and will also be doing other *useful* work.

On close examination of the problem one comes to the conclusion that the main way in which one can be successful is not so much to employ fast processors which can perform operations quickly, but rather, to arrange the processors so that they can communicate efficiently. That is, the processors can access information as quickly as they can process it.

Every interconnection network uses the concept of *locality* in some way or another: for a given spatial distribution of processors, it is not possible to connect one processor to another unless they are neighbours (Fig. 1.1). As a consequence, an algorithm can be programmed in an efficient fashion if it can be distributed in such a way that each processor need only communicate with its neighbours.

As a second consequence of the local connection method concerns the relationship between I/O and computation. Since it is not possible to connect each processor to every other, it is, in the same way, difficult to imagine that each processor could be connected directly to the machine's external environment ( that is to the host computer system), and it is the external environment that is supposed to supply data to the algorithm and to gather its results. In one way or another, this shows that the complexity of an algorithm must reside in its component operations and not in the number of I/O operations that have to be performed.

#### 1.3.3 The Systolic Model

A systolic architecture is organised as a network composed of a large number of identical, elementary cells which are locally connected. Each cell receives data from its neighbouring cells, performs a simple calculation and then transmits its results

Figure 1.1: Locally connected network of processors

(again, only to its neighbours) one cycle later. Only those cells that are at the edge of the network communicate with the external world. To fix an order of size, it can be assumed that each cell is about as complex as a microprocessor.

The cells operate in parallel under the control of a global clock (i.e., they are totally synchronised): several computations are performed at the same time by the network, and several instances of the same problem can be pipelined over the network.

The name systolic comes from an analogy between the circulation of data streams in the network and the circulation of blood in the human vascular circulatory system.

The clock which maintains synchronisation is the 'heart' of the system.

#### 1.4 Literature Review

Important arithmetic operations in finite fields include addition, subtraction, multiplication, division, exponentiation and number inversion. Among these, addition which is the same as subtraction is the simplest one and inversion has been identified as the most complicated and lengthy operation [9].

Multiplication in  $GF(2^m)$  is completely systolisable. One of the first studies on systolic multipliers for finite fields was published by Yeh et al.[10]. They developed a serial-in-serial-out systolic (SISOS) array and a parallel-in-parallel-out systolic (PIPOS) array for implementation of  $GF(2^m)$  multipliers using the standard ba-

sis representations. Both are well suited to VLS1 implementation, but the former (SISOS) requires two control signals and the latter (PIPOS) has contra flowing data streams. A system with unidirectional data flow gains advantages over a system with contra flow in terms of chip cascadability, fault tolerance and possible wafer scale integration. The systolic architecture described in [11] is also suitable for implementation using VLSI techniques, but involves broadcasting in data flow. It is often desirable to avoid broadcasting when designing a high-speed system. Wang and Lin [12] propose a parallel-in-parallel-out systolic array and a serial-in-serial-out systolic array for implementation of  $GF(2^m)$  multipliers using the standard basis representation, both of which have unidirectional data flow. The parallel form structure incorporates fault-tolerant design and the serial form structure requires only one control signal. Zhou [13] proposes a new bit-serial systolic array to compute multiplication over  $GF(2^m)$  which requires one control signal.

Hasan and Bhargava [9] have studied division over  $GF(2^m)$ . Their work has been extended by Flenn et al.[14]. A systolic solution to the problem of division has been proposed by Wang and Lin [15]. Hasan and Bhargava [9] propose bit-serial systolic divider and multiplier for finite fields  $GF(2^m)$

The problem of encoding of Reed-Solomon(RS) codes using systolic arrays has been studied by Seroussi [16]. One of the first studies on decoding of RS codes using systolic arrays has been published by Shao et al. [17]. They use the modified Euclidean algorithm to solve the key equation. Kimura et al. [18] propose a systolic

solution to the problem of RS decoding. They use the extended Euclidean algorithm to solve the key equation. Their solution is based on the work proposed by Brent et al. [19]. Several others [20, 21, 22] have proposed other nonsystolic versions to the problem of RS decoding. Nelson et al. [23] propose a systolic RS decoder which uses the extended Euclidean algorithm to solve the key equation. They use the systolic array proposed by Fitzpatrick et al. [24] to solve the key equation. The RS decoder proposed in [23] is least complex in terms of area and time. The systolic array of [24] to solve the key equation has been improved by Doyle et al. [25].

## Chapter 2

## Architectures Using Linear Shift

## Register Circuits

Galois field arithmetic can be implemented more easily than ordinary arithmetic because there are no carries. Several circuits have been proposed in [1, 3, 2] to perform the arithmetic operations in Galois fields.

#### 2.1 Linear Switching Circuits

In linear switching circuits, information is assumed to be some representation of elements of  $GF(2^m)$ . Three basic types of devices are used as shown in Fig 2.1.

A linear finite-state switching circuit is any circuit consisting of a finite number of adders, storage devices, and constant multipliers connected in a permissible way.

Adder can be implemented using an XOR gate.

The storage device is a D-type flip-flop.

For binary case, the constant multiplier is

as follows:

1 → Connection

0 → No connection

Constant Multiplier for  $k = \alpha^3$

For nonbinary case, it can be an ordinary m-input m-output binary logic circuit, whose design is dependent on the irreducible primitive polynomial. e.g., for GF(2<sup>3</sup>) using  $F(x) = x^3 + x + 1$ .

e.g., for GF(2<sup>3</sup>) using  $F(x) = x^3 + x + x$ Let  $k = \alpha^3$ . The input  $\beta$  can be represented as a polynomial

$$\beta = a_2 \alpha^2 + a_1 \alpha + a_0. \text{ Therefore,}$$

$$\alpha^3 (a_2 \alpha^2 + a_1 \alpha + a_0) = (a_2 + a_1) \alpha^2 + (a_1 + a_2 + a_0) \alpha + (a_2 + a_0).$$

Figure 2.1: The building blocks for linear switching circuits.

#### 2.2 Adders for $GF(2^m)$

Addition in  $GF(2^m)$  is bit independent, straight-forward and is easily realised by m independent xor gates. In order to add two field elements, their vector representations are added and the resultant vector is the vector representation of the sum of the two field elements.

Example 2.1 To add  $\alpha^7$  and  $\alpha^{13}$  of  $GF(2^4)$ . Their vector representations are (1101) and (1011), respectively. Their vector sum is (1101) + (1011) = (0110), which corresponds to the exponential representation of  $\alpha^5$ .

Addition can be performed both serially and in parallel. Fig. 2.2 shows a circuit for addition in  $GF(2^4)$  for each of the two cases: serial and parallel data flow. In each case, the addends are in shift registers to start with, and the sum is in a third shift register at the conclusion of the addition. The circuit for serial addition requires four clock times to complete the addition; the circuit for parallel addition requires only one clock time but has more wires and modulo-2 adders. If desired, the addends could be fed back to the inputs of their own registers so that at the end of the addition they could again be found in their registers for other purposes.

Figure 2.2: Addition of two field elements of  $GF(2^4)$ .

## 2.3 Multipliers for $GF(2^m)$

# 2.3.1 Multiplication of a Field Element by a Fixed Field Element

Let  $\beta$  be a field element in  $GF(2^m)$ , then it can be represented as a polynomial in  $\alpha$  as follows:

$$\beta = b_{m-1}\alpha^{m-1} + \dots + b_1\alpha + b_0$$

**Example 2.2** Let us multiply  $\beta$  in, say  $GF(2^4)$ , by the primitive element  $\alpha$ , whose minimal polynomial is  $F(x) = x^4 + x + 1$ .

Then  $\beta$  should be expressed as a polynomial in  $\alpha$  as follows:

$$\beta = b_0 + b_1 \alpha + b_2 \alpha^2 + b_3 \alpha^3.$$

Multiplying both sides of the equality by  $\alpha$  and using the fact  $\alpha^4 = \alpha + 1$ , the following equality is obtained:

$$\alpha \beta = b_0 \alpha + b_1 \alpha^2 + b_2 \alpha^3 + b_3 \alpha^4 \mod (\alpha^4 + \alpha + 1)$$

$$= b_3 + (b_0 + b_3) \alpha + b_1 \alpha^2 + b_2 \alpha^3.$$

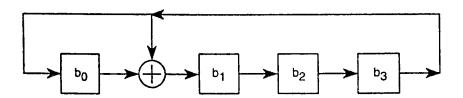

This multiplication can be carried out by the feedback shift register shown in Fig. 2.3. First, the vector representation of  $(b_0, b_1, b_2, b_3)$  of  $\beta$  is loaded into the register. Then the register is pulsed once. The new contents in the register form the

Figure 2.3: Serial multiplication implementation of  $\alpha + \beta$ .

vector representation of  $\alpha\beta$ . The equivalent parallel multiplication is given in Fig. 2.4.

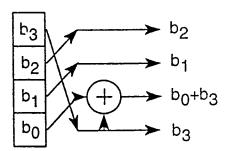

**Example 2.3** To multiply an arbitrary element  $\beta$  of  $GF(2^4)$  by the element  $\alpha^3$ .

Again  $\beta$  is expressed in polynomial form as

$$\beta = b_0 + b_1 \alpha + b_2 \alpha^2 + b_3 \alpha^3.$$

Multiplying both sides of the equation by  $\alpha^3$ , the following equation is obtained:

$$\alpha^{3}\beta = b_{0}\alpha^{3} + b_{1}\alpha^{4} + b_{2}\alpha^{5} + b_{3}\alpha^{6}$$

$$= b_{0}\alpha^{3} + b_{1}(1+\alpha) + b_{2}(\alpha+\alpha^{2}) + b_{3}(\alpha^{2}+\alpha^{3})$$

$$= b_{1} + (b_{1} + b_{2})\alpha + (b_{2} + b_{3})\alpha^{2} + (b_{0} + b_{3})\alpha^{3}.$$

Based on the expression above, the circuit obtained is shown in Fig. 2.5. Multiplication is carried out by first loading the vector representation  $(b_0, b_1, b_2, b_3)$  of  $\beta$  into the register. On pulsing the register, the new contents of the register are the vector representation of  $\alpha^3\beta$ . The serial implementation uses the same circuit as given in Fig.2.3. This time the register is pulsed three times. The new contents in the register form the vector representation of the product  $\alpha^3\beta$ .

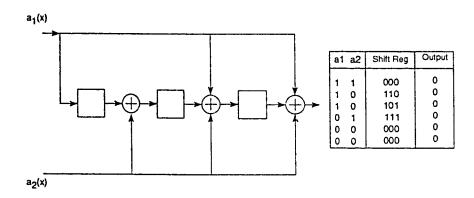

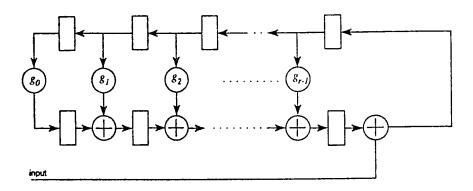

# 2.3.2 Multiplication of any Polynomial by a Fixed Polynomial mial

The circuit shown in Fig. 2.6 is known as linear feed-forward shift register in digital system theory and is also known as a finite impulse response (FIR) filter in digital

Figure 2.4: Parallel multiplication implementation of  $\alpha \cdot \beta$ .

Figure 2.5: Parallel multiplication implementation of  $\alpha^3 \cdot \beta$ .

Figure 2.6: Shift Register Circuits for multiplying polynomials.

signal processing (DSP). It multiplies any input polynomial

$$a(x) = a_k x^k + a_{k-1} x^{k-1} + \cdots + a_1 x + a_0, \quad a_i \in \{0, 1\}$$

by the fixed polynomial

$$h(x) = h_r x^r + h_{r-1} x^{r-1} + \cdots + h_1 x + h_0, h_i \in \{0, 1\}.$$

Example 2.4 Let the fixed multiplier be  $x^3 + \alpha x + \alpha^3$  and the variable multiplicand be  $\alpha^3 x^2 + x + 1$ .

The storage devices are assumed to contain 0's initially, and the coefficients of a(x) are assumed to enter high-order first.

Another circuit for multiplication is shown in Fig.2.6, which is an unconventional form of an FIR filter. The number of shifts required to obtain the complete product is equal to the sum of the degrees of the input polynomial added to 2 (= 7 in this case).

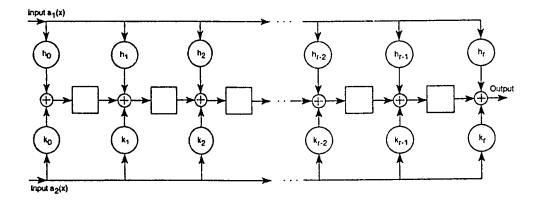

## 2.3.3 Two Input Multiplier

Circuits of the type shown above can have more than one input. The circuit shown in Fig. 2.7 has two inputs  $a_1(x)$  and  $a_2(x)$ , and the output is

$$b(x) = a_1(x)h(x) + a_2(x)k(x),$$

where

$$h(x) = h_r x^r + h_{r-1} x^{r-1} + \dots + h_0.$$

Figure 2.7: A two input multiplier

$$k(x) = k_r x^r + k_{r-1} x^{r-1} + \dots + k_0,$$

The circuit is shown as if h(x) and k(x) have the same degree, but in case the degrees are not equal, r can be taken as the larger degree, and the high order coefficients of one polynomial can be 0.

It is to be noted that in these circuits, the coefficient of the  $x^{r+i}$  comes at the same time that the coefficient of  $x^i$  goes in. The coefficient of  $x^r$  in the product comes out r units of time after the coefficients of  $x^0$  enters the input. Thus, in a sense, the output is delayed r units of time.

**Example 2.5** Let  $h(x) = x^3 + x + 1$  and  $k(x) = x^2 + x + 1$  be the fixed polynomials and the inputs be  $a_1(x) = x^2 + x + 1$  and  $a_2(x) = x^3 + x + 1$  respectively.

The resulting two input multiplier circuit is shown in Fig. 2.8.

## 2.3.4 Proposed Serial Modified Massey-Omura Multiplier

Massey and Omura developed a multiplier which obtains the product of two elements in the finite field  $GF(2^m)$ . They utilise a normal basis of form  $\{\alpha, \alpha^2, \alpha^4, \dots, \alpha^{2m-1}\}$  to represent each element in the field, where  $\alpha$  is the root of an irreducible polynomial of degree m over GF(2). In this basis, each element in the field  $GF(2^m)$  can be represented by m binary digits.

Figure 2.8: A two input multiplier with  $h(x) = x^3 + x + 1$  and  $k(x) = x^2 + x + 1$ .

#### **Preliminaries**

Multiplication in the normal basis representation requires for any one product digit the same logic circuitry as it does for any other product digit. Adjacent product-digit circuits differ only in their inputs, which are cyclically shifted versions of one another. Wang et al. [26] have developed a pipeline architecture for a Massey-Omura Multiplier (MOM) on  $GF(2^m)$  suitable for VLSI design.

Representing an element of  $GF(2^m)$  in normal basis as

$$b = b_0 \alpha + b_1 \alpha^2 + \dots + b_{m-1} \alpha^{m-1}$$

where  $b_i \in GF(2)$   $(0 \le i \le m-1)$  is the *i*th coordinate of b. In vector notation.

$$b = \mathbf{b} \alpha^{\mathbf{t}}$$

.

where  $\mathbf{b} = [b_0, b_1, \dots, b_{m-1}]$ ,  $\alpha = [\alpha, \alpha^2, \dots, \alpha^{2^{m-1}}]$ , and t denotes the vector transposition.

Let d be the product of any two elements b and c of  $GF(2^m)$ , i.e.,

$$d = \mathbf{b}\alpha^{\mathbf{t}}(\mathbf{c}\alpha^{\mathbf{t}})^{\mathbf{t}} = \mathbf{b}\mathbf{M}\mathbf{c}^{\mathbf{t}}$$

(2.1)

where the multiplication matrix  ${f M}$  is defined by

$$\alpha^{\mathbf{t}}\alpha = \begin{bmatrix} \alpha^{2^{0}+2^{0}} & \alpha^{2^{0}+2^{1}} & \cdots & \alpha^{2^{0}+2^{m-1}} \\ \alpha^{2^{1}+2^{0}} & \alpha^{2^{1}+2^{1}} & \cdots & \alpha^{2^{1}+2^{m-1}} \\ \vdots & \vdots & \ddots & \vdots \\ \alpha^{2^{m-1}+2^{0}} & \alpha^{2^{m-1}+2^{1}} & \cdots & \alpha^{2^{m-1}+2^{m-1}} \end{bmatrix}.$$

(2.2)

We may write M as

$$\mathbf{M} = \mathbf{M}_0 \alpha + \mathbf{M}_1 \alpha^2 + \dots + \mathbf{M}_{m-1} \alpha^{2^{m-1}}. \tag{2.3}$$

where the entries of the Boolean matrix  $\mathbf{M_k}$  belong to GF(2). In  $\mathbf{M_k}$ , each row and column is numbered as  $0,1,\dots,m-1$ . Then entry (i,j) of  $\mathbf{M_k}$  contains the coefficient of  $a^{2^k}$  when  $a^{2^i+2^j}$  is expressed in terms of the normal basis using  $k=0,1,\dots,m-1$ . From eqn. 2.1 and eqn. 2.3, one obtains the coordinates of the product as

$$d_{m-k-1} = \mathbf{b} \mathbf{M}_{\mathbf{m}-\mathbf{k}-1} \mathbf{c}^{\mathbf{t}}, \qquad k = 0, 1, \dots, m-1$$

$$= \mathbf{b}^{(\mathbf{k})} \mathbf{M}_{\mathbf{m}-\mathbf{k}} \mathbf{c}^{(\mathbf{k})\mathbf{t}}$$

(2.4)

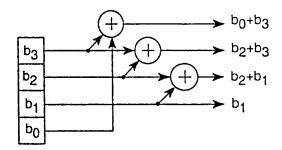

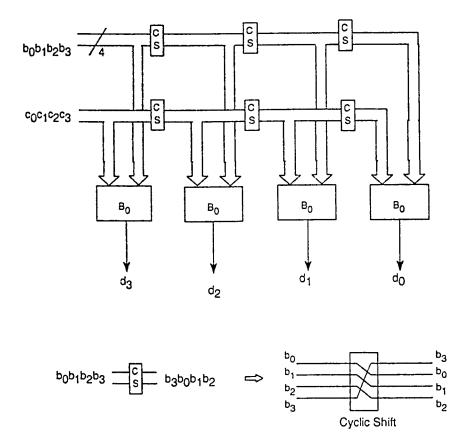

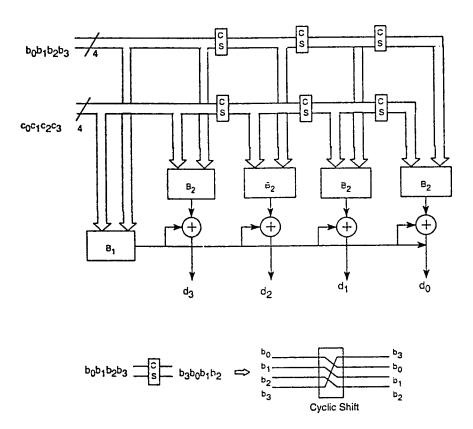

where  $\mathbf{b^{(k)}}$  is the k-fold right cyclic shift of b. A parallel multiplier based on eqn. 2.4 is shown in Fig. 2.9 and is known as a parallel-type Massey-Omura multiplier. These are m identical blocks for the m coordinates of the product d. The adjacent blocks differ only in their inputs, which are cyclically shifted versions of one another. The complexity of the module and, consequently, that of the multiplier depends on the irreducible polynomial generating the field.

#### A Modified Parallel Massey-Omura Multiplier

In this section, based on the work presented in [27], finite fields  $GF(2^m)$  generated by irreducible AOP are considered which lead to low complexity multipliers. Let  $A_m(x)$  be the irreducible AOP over GF(2). If  $\alpha \in GF(2)$  satisfies  $A_m(\alpha) = 0$ , then  $\alpha, \alpha^2, \dots, \alpha^{2^{m-1}}$  are linearly independent roots of  $A_m(x)$  and form a normal basis for

Figure 2.9: A structure for the Massey-Omura parallel multiplier over  $GF(2^4)$ .

$GF(2^m)$ . This normal basis is an *optimal normal basis* in the sense that it results in the lowest number of 1's in  $M_{m-1}$  and yields a low complexity multiplier [7]. The distribution of 1's in  $M_{m-1}$  is given in the following theorem.

Theorm 2.1 The number of 1's in the matrix  $M_{m-1}$  of an irreducible polynomial of degree m is 2m-1. These 1's appear at row i and column j satisfying

$$2^{((i-(m/2)+1))} + 2^{((j-(m/2)+1))} = 0, \text{ or } m \bmod (m+1), \tag{2.5}$$

where ((i)) denotes  $i \mod m$ .

Using the above theorem, it can be shown that  $i = ((\frac{m}{2} + j))$  always satisfies eqn.2.5 [46]. Separating these m 1's, one can express  $\mathbf{M_{m-1}}$  as a sum of two matrices, i.e.,

$$M_{m-1} = P + Q \pmod{2}.$$

(2.6)

where the entry at (i, j) of  $\mathbf{P} \stackrel{\triangle}{=} [p_{i,j}]_{i,j=0}^{m-1}$  is given as follows:

$$p_{i,j} = \begin{cases} 1, & \text{if } i = ((\frac{m}{2} + j)), \\ 0, & \text{otherwise.} \end{cases}$$

(2.7)

Referring to eqn. 2.4, one can write the shifted vector  $\mathbf{b}^{(k)}$  as

$$\mathbf{b}^{(k)} = \mathbf{b}\mathbf{T}^{(k)}. \tag{2.8}$$

where the entry at (i,j) of matrix  $\mathbf{T}^{(k)} \stackrel{\triangle}{=} [t_i^{(k)}]_{i,j=0}^{m-1}$  is

$$t_{i,j}^{(k)} = \begin{cases} 1, & \text{if } i = ((j-k)), \\ 0, & \text{otherwise.} \end{cases}$$

(2.9)

Now it can be easily seen that for any integer k

$$\mathbf{T}^{(k)}\mathbf{P}\mathbf{T}^{(k)t} = \mathbf{P}. \tag{2.10}$$

Using equations 2.4, 2.6, 2.8 and 2.10, for  $0 \le k \le m-1$ , we obtain

$$d_{m-1-k} = \mathbf{b} \mathbf{T}^{(k)} \mathbf{P} \mathbf{T}^{(k)t} \mathbf{c}^{t} + \mathbf{b}^{(k)} \mathbf{Q} \mathbf{c}^{(k)t} \pmod{2}$$

$$= \mathbf{b} \mathbf{P} \mathbf{c}^{t} + \mathbf{b}^{(k)} \mathbf{Q} \mathbf{c}^{(k)t} \pmod{2}$$

$$\stackrel{\triangle}{=} \tilde{d} + \tilde{d}_{m-1-k} \pmod{2}.$$

(2.11)

Since  $\tilde{d}$ , which is independent of k, is present in each coordinate  $d_{m-1-k}$ , it needs to be computed only once for  $k=0,1,\dots,m-1$ , resulting in a reduction in the circuit complexity of a parallel-type multiplier.

Example 2.6 Consider the irreducible all-one polynomial of degree m=4, i.e.,  $A_4(x)=x^4+x^3+x^2+x+1$ . Since the order of the root  $\alpha$  of the irreducible polynomial is m+1, the multiplication matrix M becomes

$$\mathbf{M} = \begin{bmatrix} \alpha^2 & \alpha^3 & \alpha^5 & \alpha^9 \\ \alpha^3 & \alpha^4 & \alpha^6 & \alpha^{10} \\ \alpha^5 & \alpha^6 & \alpha^8 & \alpha^{12} \\ \alpha^9 & \alpha^{10} & \alpha^{12} & \alpha^{16} \end{bmatrix} = \begin{bmatrix} \alpha^2 & \alpha^3 & 1 & \alpha^4 \\ \alpha^3 & \alpha^4 & \alpha & 1 \\ 1 & \alpha & \alpha^3 & \alpha^2 \\ \alpha^4 & 1 & \alpha^2 & \alpha \end{bmatrix}$$

$$\stackrel{\triangle}{=} \mathbf{M}_0 \alpha + \mathbf{M}_1 \alpha^2 + \mathbf{M}_2 \alpha^4 + \mathbf{M}_3 \alpha^8$$

$$= \mathbf{M}_0 \alpha + \mathbf{M}_1 \alpha^2 + \mathbf{M}_2 \alpha^4 + \mathbf{M}_3 \alpha^3.$$

As the roots  $\alpha$ ,  $\alpha^2$ ,  $\alpha^4$ ,  $\alpha^8 (= \alpha^3)$  are linearly independent,  $\alpha + \alpha^2 + \alpha^3 + \alpha^4 = 1$  and the Boolean Matrix  $M_{m-1} = M_3$  is

$$\mathbf{M}_{m-1} = \begin{bmatrix} 0 & 1 & 1 & 0 \\ 1 & 0 & 0 & 1 \\ 1 & 0 & 1 & 0 \\ 0 & 1 & 0 & 0 \end{bmatrix}.$$

Then

$$\mathbf{P} = \begin{bmatrix} 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \\ 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \end{bmatrix} \quad \mathbf{Q} = \begin{bmatrix} 0 & 1 & 0 & 0 \\ 1 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 0 \end{bmatrix}.$$

Finally,

$$\tilde{d} = \mathbf{b}\mathbf{P}\mathbf{c}^{t} = [b_{0}, b_{1}, b_{2}, b_{3}]\mathbf{P}[c_{0}, c_{1}, c_{2}, c_{3}]^{t}$$

$$\tilde{d}_{m-1-k} = \mathbf{b}^{(k)}\mathbf{Q}\mathbf{c}^{(k)t}$$

$$= [b_{((-k))}, b_{((-k+1))}, b_{((-k+2))}, b_{((-k+3))}]$$

$$\cdot \mathbf{Q}[c_{((-k))}, c_{((-k+1))}, c_{((-k+2))}, c_{((-k+3))}]^{t} \quad (0 \le k \le 3)$$

$$d_{m-1-k} = \tilde{d} + \tilde{d}_{m-1-k} \quad (0 \le k \le 3).$$

Fig. 2.10 shows a structure for the parallel multiplier based on eqn. 2.11. The common term  $\tilde{d}$  is generated by block  $B_1$ , and the coordinate-dependent terms  $\tilde{d}_{m-1-k}$   $(k=0, 1, \dots, m-1)$  by m blocks of the same kind denoted as  $B_2$ . The inputs to two adjacent  $B_2$  blocks are cyclically shifted versions of one another.

Figure 2.10: A structure for the modified Massey-Omura parallel multiplier over  $GF(2^4)$  generated by irreducible all one polynomial of degree m.

Referring to eqn. 2.7, the matrix P has one 1 in each row and column, resulting in m AND gates and m-1 XOR gates in  $B_1$ . It has been shown in [27] that  $\mathbf{M}_{m-1}$  has two 1's in all rows and columns, except the last where there is only one 1. It follows from eqn. 2.6 that matrix Q has m-1 1's which are distributed in m-1 rows and m-1 columns. Each row and column has one 1, except the last row and column, resulting in m-1 AND gates and m-2 XOR gates in  $B_2$ . The total number of gates for the modified Massey-Omura multiplier is as follows:

AND:

$$m + m(m-1) = m^2$$

.

$$XOR: m-1+m+m(m-2) = m^2-1.$$

For comparison, the other parallel-type MOM [26] (hereafter denoted as MOM) of the same class of finite fields  $GF(2^m)$ , it is generated by an irreducible polynomial and uses normal basis. Like the MOM, the multiplier proposed in [27] (denoted as MOM, M) uses the normal basis. The realisation of both multipliers requires only AND and XOR gates corresponding to mod 2 additions and multiplications. The AND gates, however, can be directly substituted by NAND gates as the XOR of two AND outputs is equivalent to the XOR of two NAND outputs. Although time delays due to gates for the MOM and the MOM, M are the same, the latter requires only about half the XOR gates. The summary of the gate counts and time delays is presented in Table 2.1 [27].

| Multiplier   | Number of AND gates | Time delay due to gates                                                                      |

|--------------|---------------------|----------------------------------------------------------------------------------------------|

| MOM<br>M_MOM | $m^2 \ m^2$         | $D_N + (1 + \lceil \log_2 m - 1 \rceil) D_X$<br>$D_N + (1 + \lceil \log_2 m - 1 \rceil) D_X$ |

Table 2.1: Comparison of Normal basis multipliers generated by the irreducible AOP of degree m

#### Proposed Serial Multiplier

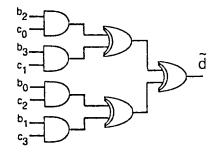

For the parallel multiplier of [27], the internal description  $B_1$  and  $B_2$  is not given. A suggested circuit diagram for  $B_1$  and  $B_2$  is given in Fig. 2.11. It satisfies the gate count given in [27].

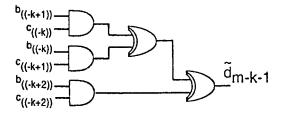

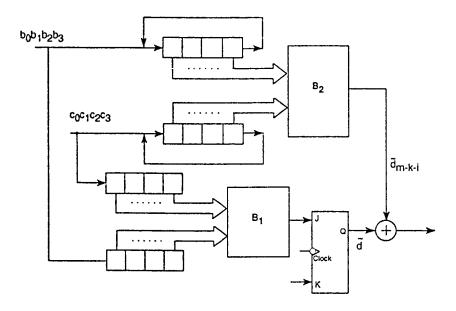

The work in [27] or [7] does not discuss any serial form implementation of the normal basis multiplier. They both use all one primitive irreducible polynomials. A suggested serial implementation of this multiplier is shown in Fig. 2.12. The proposed multiplier is also based on an all one primitive irreducible polynomial.

#### Operation and Implementation

It is based on the same principle as the parallel multiplier proposed in [27]. It requires first m bits to load the inputs into the shift registers. Then m shifts are requires to obtain the digits  $\tilde{d}_{m-k-1}$  (0)  $\leq k \leq m-1$ . Additional logic circuitry is required to generate the output  $\tilde{d}$  continuously as it is required to add  $\tilde{d}$  to each  $\tilde{d}_{m-k-1}$  (0  $\leq k \leq m-1$ . The additional logic circuitry can be a simple flip-flop (JK flip-flop) which can latch the output at  $\tilde{d}$  for rest of the operation.

#### Conclusions

The proposed multiplier can be realised by simple AND and XOR gates. It can be seen that the serial type multiplier requires the minimum number of gates. The price paid is the the delay in getting the output. It requires m shifts to compute the

Figure 2.11: Circuit diagram of  $B_1$  and  $B_2$  of the modified Massey-Omura multiplier.

Figure 2.12: Proposed serial implementation of the normal basis multiplier.

product. The maximum switching speed is determined by the delays due to gates, which is this case is given by  $D_N + (1 + \lceil \log_2 m - 1 \rceil)D_X$ , where  $D_X$  is the delay due to an XOR gate and  $D_N$  is the delay due to an AND gate. Therefore, the delay due to the gates in computing the product serially is  $m\{D_N + (1 + \lceil \log_2 m - 1 \rceil)D_X\}$ . All the parameters are tabulated in Table 2.2

# **2.4** Dividers for $GF(2^m)$

Division in  $GF(2^m)$  is performed by linear feedback shift registers (LFSR), also known as infinite-impulse-response filter (IIR). A circuit for dividing  $d(x) = d_n x^n + d_{n-1}x^{n-1} + \cdots + d_0$  by  $g(x) = g_r x^r + g_{r-1}x^{r-1} + \cdots + g_0$  is shown in Fig. 2.13. The storage devices must be set to 0 initially. The output is 0 for the first r shifts, that is, until the input symbol reaches the end of the shift register. Then the first nonzero output appears, and its value is  $d_n g_r^{-1}$ , the first coefficient of the quotient. For each quotient coefficient  $q_j$ , the polynomial  $q_j g(x)$  must be subtracted from the dividend. The feedback connections accomplish this subtraction. After a total of n shifts, the entire quotient has appeared at the output, and the remainder is in the shift register.

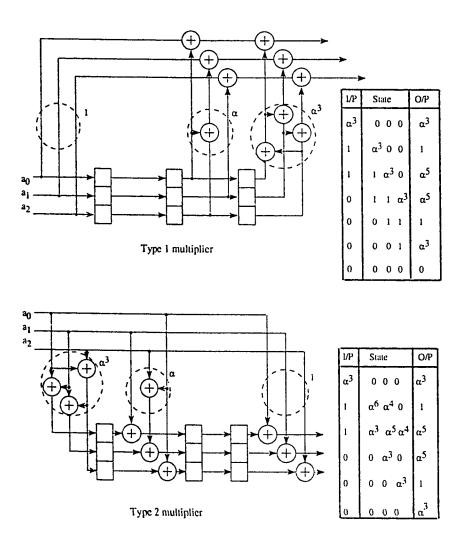

**Example 2.7** Two types of circuits which performs division in  $GF(2^3)$  are presented in Figs. 2.14 and 2.15 for dividing the input polynomial  $v(x) = \alpha^4 x^6 + \alpha^3 x^3 + \alpha^6 x + \alpha^6$  by the fixed polynomial  $g(x) = x^4 + \alpha^3 x^3 + x^2 + \alpha x + \alpha^3$ .

| Normal                                       |

|----------------------------------------------|

| 2m - 1                                       |

| 2m - 2                                       |

| $D_N + (1 + \lceil \log_2 m - 1 \rceil) D_N$ |

| m                                            |

|                                              |

Table 2.2: Parameters of the proposed serial multiplier

Figure 2.13: A circuit for dividing polynomials.

Figure 2.14: Type 1 circuit for dividing polynomials.

| ИP |   | State                             | Quotient | Rem.                             |

|----|---|-----------------------------------|----------|----------------------------------|

| α4 |   | 0000                              | 0        |                                  |

| 0  | 1 | $\alpha^4$ 0 0 0                  | 0        |                                  |

| 0  | ١ | 1 α <sup>4</sup> 0 0              | 0        |                                  |

| α3 |   | $\alpha^6$ 1 $\alpha^4$ 0         | 0        |                                  |

| 0  | ١ | 1 α <sup>6</sup> 1 α <sup>4</sup> | 0        |                                  |

| α6 | , | α <sup>6</sup> 1 α <sup>6</sup> 1 | α4       |                                  |

| α4 |   | α α <sup>5</sup> 1 α <sup>6</sup> |          |                                  |

| 0  | - | α <sup>3</sup> α α <sup>6</sup> 1 | α6       |                                  |

| 0  |   | 0 α <sup>3</sup> α α <sup>6</sup> |          | α <sup>6</sup><br>α <sup>3</sup> |

| 0  |   | 00 α <sup>3</sup> α               |          | α <sup>3</sup>                   |

| 0  |   | 000α                              | 1        | 0                                |

| 0  |   | 0000                              |          | α <sup>6</sup>                   |

Quotient =  $\alpha^4 x + x + \alpha^6$ Remainder =  $\alpha^6 x^3 + \alpha^3 x^2 + \alpha^6$

Figure 2.15: Type 2 circuit for dividing polynomials.

## 2.5 Applications: Reed-Solomon (RS) Codes

#### 2.5.1 Preliminaries

Reed-Solomon (RS) codes are cyclic non-binary codes. They are used in error control coding for deep space communication and for data storage devices. The codewords can be represented as polynomials where the coefficients are m-bit symbols taken from a finite field  $GF(2^m)$ . RS error correction is concerned with correcting symbols and not individual bits. For a t-error correcting (TEC) Reed-Solomon code the generator polynomial is

$$g(x) = (x - \alpha)(x - \alpha^2) \cdots (x - \alpha^{2t}). \tag{2.12}$$

This always is a polynomial of degree 2t. Hence a RS code satisfies n - k = 2t. They are Maximum Distance Separable (MDS) codes, and the minimum distance is n - k + 1 which is the largest minimum distance a code can have. For a fixed (n, k), no code can have a larger minimum distance than a RS code. The parameters of an RS code defined over  $GF(2^m)$  are given below:

Number of bits per symbol : m

Code length in symbols :  $n = 2^m - 1$

Number of information symbols : k = n - d + 1

Error correcting capability : t

Number of parity symbols : 2t

Minimum distance

$$: d = n - k + 1$$

The cyclic property of the RS codes makes it attractive to use shift-register circuits for constructing encoders and decoders. RS codes can be implemented non-systematically by multiplication of the variable information polynomial i(x) with the fixed polynomial g(x) to get the codeword c(x). This can be implemented with a FIR filter over GF(2).

### 2.5.2 Systematic Encoding of RS Codes

Given the generator polynomial g(x) of an (n,k) RS code, the code can be put in a systematic form. That is, the first k digits of the each code word are the unaltered information digits: the last n-k digits are parity check digits. Suppose that the message of k digits to be encoded is

$$m = (m_0, m_1, m_2, \cdots, m_k - 1).$$

(2.13)

The corresponding message polynomial is

$$m(x) = m_0 + m_1 x + m_2 x^2 + \dots + m_{(k-1)} x^{k-1}$$

(2.14)

Multiplying m(x) by  $x^{n-k}$  and then dividing by g(x), we obtain

$$x^{n-k}m(x) = q(x)g(x) + r(x)$$

(2.15)

where q(x) and r(x) are the quotient and the remainder respectively.

Since the degree of the generator polynomial g(x) is n-k, the degree of r(x) must

be n-k-1 or less,

$$r(x) = r_0 + r_1 x + r_2 x^2 + \dots + r_{(n-k-1)} x^{n-k-1}.$$

(2.16)

Rearranging eqn 2.15, we obtain

$$r(x) - x^{n-k}m(x) = q(x)g(x)$$

(2.17)

This indicates that  $r(x) + x^{n-k}m(x)$  is a multiple of g(x) and has degree n-1 or less. Therefore,  $r(x) + x^{n-k}m(x)$  is a code polynomial of the RS code c generated by g(x).

$$c(x) = r(x) + x^{n-k} m(x)$$

$$= r_0 + r_1 x + r_2 x^2 + \dots + r_{n-k-1} x^{n-k-1} + \dots$$

$$m_0 x^{n-k} + m_1 x^{n-k+1} + \dots + m_{(k-1)} x^{n-1}$$

(2.18)

From eqn 2.18, it is clear that the encoding of a message block m(x) of k digits is equivalent to calculating the parity check polynomial r(x) which is the remainder of dividing  $x^{n-k}m(x)$  by the generator polynomial g(x). This is accomplished by a dividing circuit which is a shift register with feedback connections according to the generator polynomial, with  $g_0 = 1$ ,

$$q(x) = q_0 + q_1 x + q_2 x^2 + \dots + q_{n-k-1} x^{n-k-1} + x^{n-k}.$$

(2.19)

An encoding circuit with an (n-k)-stage shift register is shown in Fig. 2.16. The quantities  $g_0, g_1, \dots, g_r$  are the coefficients of the generator polynomial of the code.

Consider the example of a double error correcting (DEC) RS (7,3) code with symbols from  $GF(2^3)$ . The primitive polynomial is

$$p(z) = z^3 + z + 1$$

and the generator polynomial is given by

$$g(x) = LCM [m_1(x), m_2(x), m_3(x), m_4(x)]$$

$$= (x + \alpha)(x + \alpha^2)(x + \alpha^3)(x + \alpha^4)$$

$$= [x^2 + (\alpha + \alpha^2)x + \alpha^3] [x^2 + (\alpha^3 + \alpha^4)x + \alpha^7]$$

$$= (x^2 + \alpha^4 + \alpha^3)((x^2 + \alpha^6x + \alpha^0)$$

$$= x^4 + (\alpha^6 + \alpha^4)x^3 + (1 + \alpha^3 + \alpha^3)x^2 + (\alpha^4 + \alpha^2)x + \alpha^3$$

$$= x^4 + \alpha^3x^3 + x^2 + \alpha x + \alpha^3$$

Therefore,  $g(x) = x^4 + \alpha^3 x^3 + x^2 + \alpha x + \alpha^3$ . When implemented with binary circuits, the octal shift registers stages are three binary shift register stages in parallel. All data are 3-bit wide. The binary equivalent of the coefficients of the generator polynomial are calculated by multiplying the coefficients with a polynomial  $a_2z^2 + a_1z + a_0$ ,  $a_i \in GF(2)$  and taking the remainder on division by the irreducible polynomial p(z). The computation is described below:

$$R_{p(z)}[z^{3}(a_{2}z^{2} + a_{1}z + a_{0})] = (a_{1} + a_{2})z^{2} + (a_{0} + a_{1} + a_{2})z + (a_{0} + a_{2})$$

Figure 2.16: An (n-k)-stage feedback shift register encoding circuit

$$R_{p(z)}[z(a_2z^2+a_1z+a_0)] = a_1z^2+(a_2+a_0)z+a_0$$

The binary implementation of the (7,3) RS code is shown in Fig. 2.17.

The implementation shown above is in wide use. It is simple, and it meets the requirements for most applications. However, in some very high speed applications, the presence of a global feedback signal imposes constraints on the switching speed of the encoder. The fact that the input to all (n-k) stages depend on the feedback signal, forces the (n-k) stages to be synchronous, hence imposing the use of a global clock. The need to distribute the global clock and the feedback signal to all stages of the encoder might restrict the maximum switching speed achievable in a practical implementation. An alternative approach for the elimination of the feedback is to modify the FSR encoder of Fig. 2.16, by "pipelining" the feedback path so that the feedback signal goes through one delay unit before it is fed back to each shift register stage. This architecture is shown in Fig. 2.18. The resulting encoding stream is interleaved 2:1.

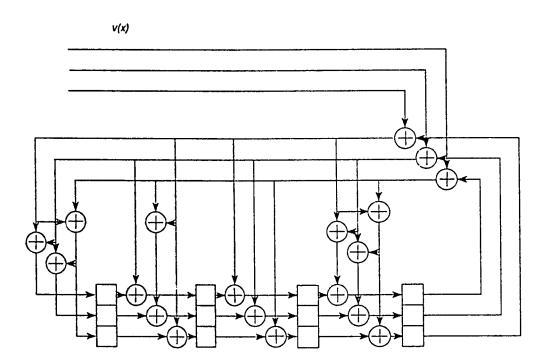

### 2.5.3 Decoding of RS Codes

When a codeword is transmitted over a noisy channel, it may be corrupted by noise. At the output of the channel, the received word may or may not be the same as the transmitted code word. The function of the decoder is to recover the transmitted code word from the knowledge of the received word. Let the received word be

Figure 2.17: Encoder for the RS (7,3) code using binary logic elements.

Figure 2.18: Pipelined LFSR encoder

represented by the binary polynomial

$$v(x) = v_0 + v_1 x + v_2 x^2 + \dots + v_{n-1} x^{n-1}$$

.

The decoder first checks whether or not the received polynomial corresponds to a codeword by dividing the polynomial by the generator polynomial g(x) of the code. The remainder after the division is the syndrome of the received word.

$$v(x) = p(x)q(x) + s(x), (2.20)$$

where s(x) is a polynomial of degree (n-k-1) or less. Thus, the syndrome is a (n-k)-tuple. If the syndrome is zero, the received polynomial is divisible by the generator polynomial and corresponds to a codeword; the decoder will accept the received word as the transmitted code vector. If the syndrome is a non-zero vector, the received vector is not a codeword and errors have been detected. Supposing that c(x) be the transmitted polynomial, then in the case of an error

$$v(x) = c(x) + e(x)$$

(2.21)

where e(x) is the error pattern caused by the channel disturbance. Since c(x) is a code polynomial, it must be a multiple of the generator polynomial g(x), say

$$c(x) = m(x)g(x). (2.22)$$

Combining Eqs. 2.20, 2.21 and 2.22, we obtain

$$e(x) = [p(x) - m(x)] g(x) + s(x)$$

(2.23)

That is, the syndrome of v(x) is equal to the remainder resulting from dividing the error pattern by the generator polynomial g(x) of the code. Thus, the syndrome of the received word contains the information about the error pattern in the received word, which will be used for error correction.

The syndrome calculation is accomplished by a division circuit which is identical to the encoding circuit at the transmitter. The syndrome calculator for the RS (7,3) code is shown in Fig. 2.19.

The received word is shifted into the register with all stages initially set to "0". After the entire received word has been entered into the shift register, i.e., after n shift pulses, the contents will be the syndrome.

#### Error Trapping

An error trapping decoder is a modification of a Meggitt decoder that can be used for certain cyclic codes including BCH codes and RS codes. Suppose that all errors in a received word occur close together. Then the syndrome, properly shifted, exhibits an exact copy of the error pattern. Defining the length of an error pattern as the smallest number of sequential stages of a shift register that must be observed so that for some cyclic shift of the error pattern, all errors are within this segment of the shift register. Supposing that the longest-length error pattern that must be corrected is no longer than the syndrome. Then for some cyclic shift of the error pattern, the syndrome is equal to the error pattern. For such codes, the syndrome

Figure 2.19: Syndrome Calculator for the RS (7,3) code.

generator is shifted until a correctable pattern is observed. The content of the syndrome generator is subtracted from the cyclically shifted received polynomial and correction is complete. Referring to the example of the Reed-Solomon (7,3) code over GF(8) with generator polynomial

$$g(x) = x^4 + (z+1)x^3 + x^2 + zx + (z+1),$$

where the field elements are expressed as polynomials in z. Alternatively,

$$g(x) = x^4 + \alpha^3 x^3 + x^2 + \alpha x + \alpha^3$$

,

where the field elements are expressed in terms of the primitive element a = z. This is a double error correcting (DEC) code. The error pattern e(x) has at most two

| $\alpha^0 = 1$           | $g(x) = x^4 + \alpha^3 x^3 + x^2 + \alpha x + \alpha^3$                     |

|--------------------------|-----------------------------------------------------------------------------|

| $\alpha^1 = z$           | $c(x) = \alpha^4 x^6 + \alpha^4 x^4 + \alpha^3 x^3 + \alpha^6 x + \alpha^6$ |

| $\alpha^2 = z^2$         | $e(x) = \alpha^4 x^4 + \alpha^3$                                            |

| $\alpha^3 = z + 1$       | $v(x) = \alpha^4 x^6 + \alpha^3 x^3 + \alpha^6 x + \alpha^4$                |

| $\alpha^4 = z^2 + z$     |                                                                             |

| $\alpha^5 = z^2 + z + 1$ |                                                                             |

| $a^6 = z^2 + 1$          |                                                                             |

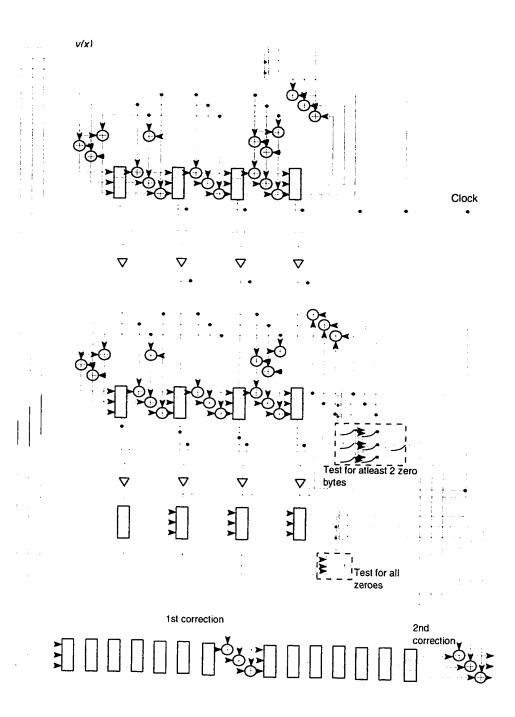

nonzero terms and is a polynomial of degree 6 or less. It can always be cyclically shifted into a polynomial of degree 3 or less. Because the syndromes are of degree 3 or less, error trapping can be applied. The error trapping decoder is shown in Fig. 2.20. The binary circuit implementation uses octal shift register stages with three binary shift register stages in parallel. The multiply-by-z+1 (that is, by  $\alpha^3$ ) and

Figure 2.20: Pipelined decoder for the RS (7.3) code

-z (that is, by  $\alpha$ ) circuits in the feedback path are simple three-input three-output binary-logic circuits. A total of 21 shifts are necessary for this decoder to correct all errors. The first set of 7 shift computes the syndrome. The second set of 7 shifts corrects at least one error and the third set of 7 shifts corrects the second error.

In Table 2.3, for each shift, the content of both the syndrome register and the information buffer are listed. Beginning with the eighth shift, the circuit will correct an error whenever it sees an error-trapped pattern. This is a pattern with at most two nonzero symbols and one with one of the nonzero symbols in the right-most place. Such a pattern must always occur at least once in the second 7 shifts if no more than 2 errors occur. In the example, it occurs at shift 13. Hence, the error is trapped. It is to be noticed that the high-order syndrome symbols are normally to the right. That the error is trapped can be seen from a 4 symbol segment of the cyclically shifted error pattern  $(e_4, e_5, e_6, e_0)$ . Because the error is trapped,  $e_0$  is corrected in the information register and set equal to zero (or subtracted from itself) in the syndrome register. After 14 shifts, the syndrome register contains the syndrome of the remaining error pattern. The process repeats through a third set of 7 shifts, after which the error correction is complete.

If the syndrome is initially nonzero but no error is trapped during the second set of 7 shifts, then more than two errors occurred (but the converse is not true). Additional logic can easily included to detect an uncorrectable error pattern.

| Shift | Syndrome Register                                             |                   | Information Register                                   |

|-------|---------------------------------------------------------------|-------------------|--------------------------------------------------------|

| 0     | 0 0 0 0                                                       |                   | 0 0 0 0 0 0                                            |

| 1     | $1 \alpha^5 \alpha^4 1$                                       |                   |                                                        |

|       | $\alpha^3 \alpha^3 \alpha^4 \alpha^6$                         |                   | $a^40000000$                                           |

| 2     |                                                               |                   | $0  \alpha^4 0  0  0  0  0$                            |

| 3     | $\alpha^2 \alpha \alpha^4 \alpha$                             |                   | $0\ 0\ \alpha^4 0\ 0\ 0\ 0$                            |

| 4     | $\alpha^3 \alpha^4 \alpha^3 \alpha^6$                         |                   | $\alpha^30~0~\alpha^40~0~0$                            |

| 5     | $\alpha^2 \alpha^1 \alpha^3 \alpha^5$                         |                   | $0 \ \alpha^3 0 \ 0 \ \alpha^4 0 \ 0$                  |

| 6     | $\alpha^40 \ 0 \ \alpha^6$                                    |                   | $\alpha^{6}0 \ \alpha^{3}0 \ 0 \ \alpha^{4}0$          |

| 7     | $\alpha^6 0 \ \alpha^3 \alpha^6$                              | Syndrome          | $\alpha^4 \alpha^6 0 \ \alpha^3 0 \ 0 \ \alpha^4$      |

| 8     | $\alpha^2 \alpha^2 \alpha^6 \alpha^5$                         | . •               | $\alpha^4 \alpha^4 \alpha^6 0 \alpha^3 0 0$            |

| 9     | $\alpha \ 1 \ \alpha^3 \alpha^5$                              |                   | $0 \alpha^4 \alpha^4 \alpha^6 0 \alpha^3 0$            |

| 10    | $\alpha \ \alpha^5 \alpha^4 1$                                |                   | $0.0 \alpha^4 \alpha^4 \alpha^6 0 \alpha^3$            |

| 11    | $\alpha^3 0 \alpha^4 \alpha^6$                                |                   | $\alpha^30$ 0 $\alpha^4\alpha^4\alpha^60$              |

| 12    | $\alpha^2 \alpha \alpha^6 \alpha$                             |                   | $0 \alpha^3 0 0 \alpha^4 \alpha^4 \alpha^6$            |

| 13    | $\frac{\alpha^4 0 \ 0 \ \alpha^3}{\alpha^4 0 \ 0 \ \alpha^3}$ |                   |                                                        |

| 14    | $\frac{\alpha \ 0 \ 0 \ \alpha}{0 \ \alpha^4 0 \ 0}$          | . ← Trapped error | $\alpha^{6}0 \ \alpha^{3}0 \ 0 \ \alpha^{4}\alpha^{4}$ |

|       |                                                               | -                 | $\alpha^6\alpha^60 \alpha^30 0 \alpha^4$               |

| 15    | $0.0  \alpha^4 0$                                             | • <u> </u>        | $\alpha^6\alpha^60$ $\alpha^30$ 0                      |

| 16    | $0\ 0\ 0\ \alpha^4$                                           | ← Trapped error   | $\alpha^6\alpha^60 \ \alpha^30$                        |

| 17    | 0000                                                          |                   | $\alpha^6 \alpha^6 0 \ \alpha^3$                       |

| 18    | 0000                                                          |                   | $\alpha^6 \alpha^6 0$                                  |

| 19    | 0000                                                          |                   | $\alpha^6 \alpha^6$                                    |

| 20    | 0000                                                          |                   | $\alpha^6$                                             |

| 21    | 0000                                                          |                   |                                                        |

Table 2.3: Error Trapping Example

# Chapter 3

# Architectures Using Systolic

# Arrays

The advantages of the LSR circuits and the designs based on the normal basis are that they take lesser area. However, they are less expandable because irreducible polynomials for different m are not related, but the design focusses on one particular m each time. Since systolic arrays have the advantages of regularity, modularity and expandability, systolic designs are worthy of consideration.

# 3.1 Multipliers for $GF(2^m)$

Multipliers based on standard basis or conventional basis do not require any basis conversion. Wang and Lin [12] developed a serial-in-serial-out systolic (SISOS) ar-

ray multiplier and a parallel-in-parallel-out systolic (PIPOS) array multiplier which obtains the product of two elements in the finite field  $GF(2^m)$  in standard basis. The multipliers are based on the algorithm developed in [28], which is presented in the next section.

#### 3.1.1 Parallel-In-Parallel-Out Systolic (PIPOS) Array

Let two elements of  $GF(2^m)$  be  $A(x) = a_{m-1}x^{m-1} + \cdots + a_1x + a_0$  and  $B(x) = b_{m-1}x^{m-1} + \cdots + b_1x + b_0$ , and the irreducible polynomial be  $F(x) = x^m + g_{m-1}x^{m-1} + \cdots + g_1x + 1$ , where the coefficients  $a_j$ ,  $b_j$ , and  $g_j \in GF(2)$ . The product  $A(x)B(x) \operatorname{mod} G(x)$  can be represented by  $P(x) = p_{m-1}x^{m-1} + \cdots + p_1x + p_0$ .

The multiplication A(x)B(x) modG(x), can be expanded by multiplying each term of B(x) by A(x) as shown below in eqn. 3.1.

$$P(x) = A(x)B(x) \bmod G(x)$$

$$= A(x)\{b_{m-1}x^{m-1} + \dots + b_1x + b_0\} \bmod G(x)$$

$$= \{A(x)b_{m-1}x^{m-1} \bmod G(x) + \dots + A(x)b_1x \bmod G(x) + A(x)b_0 \bmod G(x)$$

(3.1)

Beginning with the first term,  $A(x)b_{m-1}x^{m-1} \mod G(x)$ , each successive term in eqn. 3.1 is added to it and the sum reduced  $\mod G(x)$  until all terms have been used. Based on the above algorithm, P(x) can be computed recursively as follows:

$$T_0(x) = 0 (3.2)$$

$$T_i(x) = [T_{i-1}(x)x] \mod G(x)$$

$+ A(x)b_{m-i}, \qquad i = 1, 2, \dots, m$  (3.3)

$$P(x) = T_m(x). (3.4)$$

where

$$T_i(x) = t_{i,m-1}x^{m-1} + t_{i,m-2}x^{m-2} + \dots + t_{i,1}x + t_{i,0}$$

(3.5)

$$P(x) = p_{m-1}x^{m-1} + p_{m-2}x^{m-2} + \dots + p_1x + p_0.$$

(3.6)

Denoting the coefficient of the highest order term of  $T_i(x)$  by  $M_i$ , we can write the recurrence relation as

$$T_i(x) = T_{i+1}(x)x + G(x)M_{i-1}$$

$+ A(x)b_{m-i}, i = 1, 2, 3, \dots, m$  (3.7)

The above computing procedure is realised by a PIPOS array as shown in Fig. 3.1 [12], where  $m \times m$  basic cells are used. The basic cell at position (i, k) performs the following logic operation:

$$t_{i,k} = t_{i-1,k+1} \oplus (g_{m-k} \cdot M_{i-1})$$

$$\oplus (a_{m-k} \cdot b_{m-i}).$$

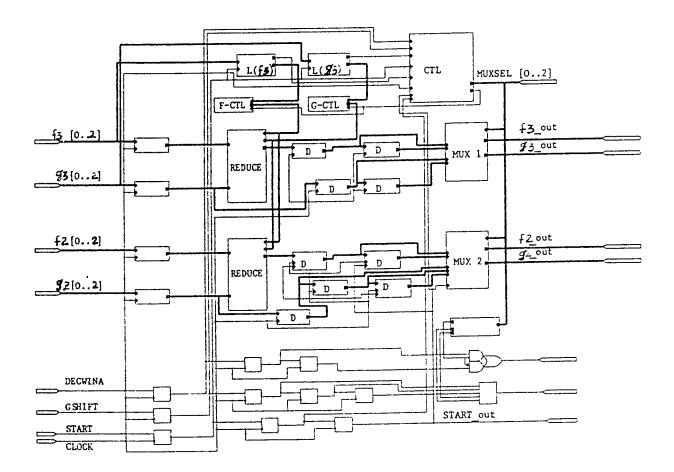

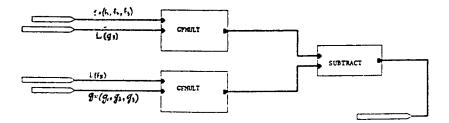

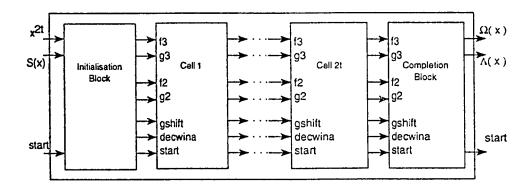

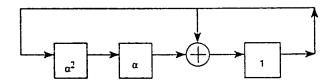

(3.8)