### Organization of Parallel Memories

by

Husam Saad Abu-Haimed

A Thesis Presented to the FACULTY OF THE COLLEGE OF GRADUATE STUDIES

KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

**MASTER OF SCIENCE**

In

**COMPUTER ENGINEERING**

June, 1997

**INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI

films the text directly from the original or copy submitted. Thus, some

thesis and dissertation copies are in typewriter face, while others may be

from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the

copy submitted. Broken or indistinct print, colored or poor quality

illustrations and photographs, print bleedthrough, substandard margins,

and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete

manuscript and there are missing pages, these will be noted. Also, if

unauthorized copyright material had to be removed, a note will indicate

the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by

sectioning the original, beginning at the upper left-hand corner and

continuing from left to right in equal sections with small overlaps. Each

original is also photographed in one exposure and is included in reduced

form at the back of the book.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white

photographic prints are available for any photographs or illustrations

appearing in this copy for an additional charge. Contact UMI directly to

order.

UMI

A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor MI 48106-1346 USA 313/761-4700 800/521-0600

# ORGANIZATION OF PARALLEL MEMORIES

يحاعد اعداعد اعد

BY

#### **HUSAM SAAD ABU-HAIMED**

A Thesis Presented to the

FACULTY OF THE COLLEGE OF GRADUATE STUDIES

KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

र्वे त्राम्मास्त्राम्मास्त्राम्मास्त्राम्मास्त्राम्मास्त्राम्मास्त्राम्मास्त्राम्मास्त्राम्मास्त्राम्मास्त्राम्मास्त्राम्मास्त्राम्मास्त्राम्मास्त्राम्मा

# MASTER OF SCIENCE In

**COMPUTER ENGINEERING**

**JUNE 1997**

UMI Number: 1386583

UMI Microform 1386583 Copyright 1997, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

300 North Zeeb Road Ann Arbor, MI 48103

# KING FAHD UNIVERSITY OF PETROLEUM AND MINERALS DHAHRAN, SAUDI ARABIA COLLEGE OF GRADUATE STUDIES

This thesis, written by

#### **HUSAM SAAD ABU-HAIMED**

under the direction of his Thesis Advisor and approved by his Thesis Committee.

has been presented to and accepted by the Dean of the College of Graduate Studies.

in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE IN COMPUTER ENGINEERING

Thesis Committee

Dr. Mayez Al - Mouhamed (Chairman)

Dr. Khalid M. Al - Tawi. (Co - Chairman)

Dr. Khalid Lilleithy Member

Dr. Must & Box sigit ( Vl mber)

Dr. Ahalid M. Al - Tawil

(Department Chairman)

Dr. Abdallah M. Ai - Shehri

(Dean, College of Graduate Studies)

9-8-97 Date

## **Dedicated**

To my mother

who gave me every thing in excess and asked for nothing but my success.

To my father.

To my brothers and sisters.

#### Acknowledgement

First and foremost, all praise to Allah who gave me all the help, guidance, and courage to finish my work. May Allah help me to convey all what I learned for the benefit and goodness of Islam and humanity.

Acknowledgment is due to King Fahd University of Petroleum and Minerals. Dhahran, Saudi Arabia, for providing me with all the support needed to conduct this research.

I am so thankful to my thesis advisor, Dr. Mayez Al-Mouhamed, for his continuous help and guidance throughout the course of this thesis and all of my research. As my thesis advisor as well as my academic advisor, he put every possible effort to help me achieve my goals. Working with him is an experience that I can never forget. I am also thankful to my thesis committee members Dr. Khalid Al-Tawil, Dr. Khaled Elleithy. and Dr. Muslim Bozyigit for their real cooperation and helpful and constructive criticism.

All my thanks and appreciation to my mother, in the first place, and then to my family for their cooperation, understanding, and patience throughout my academic work. My Deep thanks go to my dear friend Mr. Tariq Ibraheem for his great help and support since the beginning of my work and up to the last moment. Thanks also to my friends Ala Al-Fuqaha, Ahmed Al-Shargawi. Talal Al-Kharroobi, and Mohamed Kaleem for their help. Last but not least, I am thankful to my friends (in alphabetical order) Abdallah Al-

Anzi, Abdallah Al-Ghumaiz, Ahmed Al-Kubayir, Ahmed Al-Sawi, Hatim Khan, Khalid Al-Blwi, Luai Aqil, Mouhamed Al-Khubani, Mouhamed Nabhan, Mouhamed Shogair, Nedal Saadeh, Samir Abbad, and Walid Al-Faris for their great friendship.

# **Contents**

| Ac  | know   | ledgme   | ent                          | i   |

|-----|--------|----------|------------------------------|-----|

| Lis | st of  | Tables   | •                            | vii |

| Lis | t of   | Figures  | s                            | ix  |

| Ab  | stract | t (Engli | ish)                         | œ   |

| Ab  | stract | t (Arab  | ic)                          | vii |

|     |        |          |                              |     |

| 1.  | Intr   | oductio  | nn                           | 1   |

| 1.  | 1.1    |          | nology                       |     |

|     |        | 1.1.1    | Alternative Technologies     |     |

|     |        | 1.1.2    | Wider Buses                  | . 3 |

|     |        | 1.1.3    | Use of SRAM                  | . 3 |

|     |        | 1.1.4    | Special Interfaces           | . 4 |

|     | 1.2    | Softw    | rare                         | . 5 |

|     |        | 1.2.1    | Minimizing Memory References | . 6 |

|    |      | 1.2.2    | Reducing Idle Time                     | 7    |

|----|------|----------|----------------------------------------|------|

|    | 1.3  | Archit   | tecture                                | 8    |

|    |      | 1.3.1    | Cache Architecture                     | 8    |

|    |      | 1.3.2    | Parallel Memory Architecture           | 9    |

|    | 1.4  | Time :   | Parallelism                            | . 10 |

|    | 1.5  | Space    | Parallelism                            | . 10 |

|    |      | 1.5.1    | Prime Memory Systems                   | . 13 |

|    |      | 1.5.2    | Skewing Schemes                        | . 14 |

|    |      | 1.5.3    | Bitwise Address Transformation Schemes | . 15 |

| 2. | Lite | rature ] | Review                                 | . 18 |

|    | 2.1  | Backg    | round                                  | . 18 |

|    | 2.2  | Regula   | ar Data Patterns                       | . 20 |

|    | 2.3  | Prime    | Memory Systems (PMS)                   | . 21 |

|    | 2.4  | Skewi    | ng Schemes                             | . 24 |

|    | 2.5  | Bitwis   | se Address Transformations             | . 26 |

| 3. | Line | ar Bitv  | vise Storage Schemes                   | . 31 |

|    | 3.1  | Introd   | uction                                 | . 31 |

|    | 3.2  | Backg    | round                                  | . 34 |

|    | 3.3  | Analy    | sis of Storage Schemes                 | . 39 |

|    | 3.4  | Comb     | ined Storage Schemes                   | . 41 |

|    | 3.5  | Acces    | sing Arbitrary Strides                 | . 47 |

|    | 3.6 | NP-Completeness                       | 50    |

|----|-----|---------------------------------------|-------|

| 4. | Heu | ristic Approaches                     | 52    |

|    | 4.1 | Introduction                          | 52    |

|    | 4.2 | Coloring heuristics                   | 54    |

|    | 4.3 | Weighted coloring with node splitting | 55    |

|    | 4.4 | A clustering-based heuristic          | 57    |

|    | 4.5 | The merge-split heuristic             | 62    |

|    | 4.6 | Evaluation                            | 68    |

|    |     | 4.6.1 Power-of-2 Patterns             | 68    |

|    |     | 4.6.2 Arbitrary Strides               | 71    |

|    |     | 4.6.3 Results                         | 72    |

| 5. | Neu | ral Networks                          | 83    |

|    | 5.1 | Background                            | 84    |

|    | 5.2 | Why Use a NN ?                        | 85    |

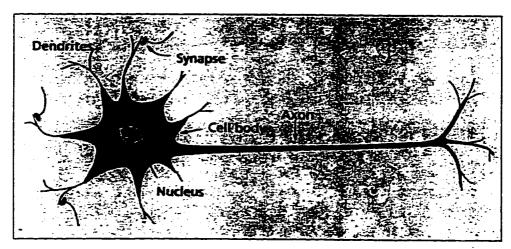

|    | 5.3 | Biological Neural Nets                | 87    |

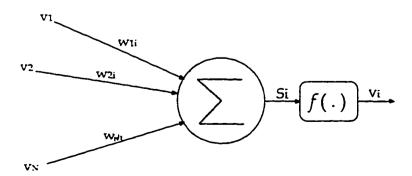

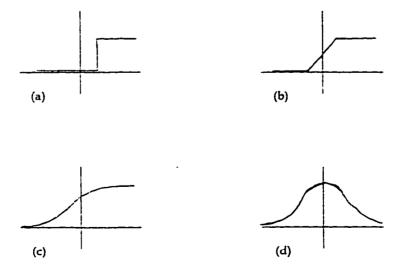

|    | 5.4 | Artificial Neural Nets                | 38    |

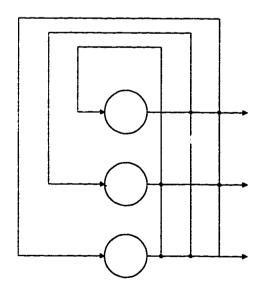

|    | 5.5 | The Hopfield Model                    | 9 i   |

|    | 5.6 | Constructing the matrix               | 94    |

|    | 5.7 | Proposed Architecture I               | 96    |

|    | 5.8 | Proposed Architecture II              | . 103 |

|    | 5.9 | Evaluation                            | . 106 |

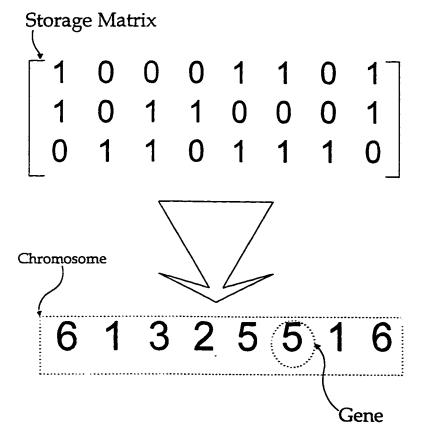

| 6. | Gen   | etic Algorithms          | 114   |

|----|-------|--------------------------|-------|

|    | 6.1   | Background               | 115   |

|    | 6.2   | Encoding Scheme          | 118   |

|    | 6.3   | Fitness Function         | 120   |

|    | 6.4   | Initial Population       | 121   |

|    | 6.5   | Selection                | 121   |

|    | 6.6   | Crossover                | 123   |

|    | 6.7   | Mutation                 | 125   |

|    | 6.8   | Control Parameters       | 127   |

|    | 6.9   | The Algorithm            | 129   |

|    | 6.10  | Evaluation               | 131   |

| 7. | Com   | parisons and Conclusions | 138   |

|    | 7.1   | Comparisons              | 138   |

|    | 7.2   | Conclusion               | . i43 |

|    | Bibli | iography                 | 145   |

# **List of Tables**

| Table 4-1: Worst Case Pattern Access of MS       | 77  |

|--------------------------------------------------|-----|

| Table 4-2: Worst Case Pattern Access of GC       | 77  |

| Table 4-3: Worst Case Pattern Access of Clust    | 77  |

| Table 4-4: Stride Access of MS                   | 82  |

| Table 4-5 : Stride Access of GC                  | 82  |

| Table 4-6 : Stride Access of Clust               | 82  |

| Table 5-1: Worst Case Pattern Access of AI       | 109 |

| Table 5-2: Worst Case Pattern Access of AII      | 109 |

| Table 5-3: Stride Access of AI                   | 113 |

| Table 5-4: Stride Access of AII                  | 113 |

| Table 6-1: Worst Case Pattern Access of 2-Cut GA | 134 |

| Table 6-2: Worst Case Pattern Access of 1-Cut GA | 134 |

| Table 6-3 : Stride Access of 2-Cut GA            | 131 |

|                                                | viii |

|------------------------------------------------|------|

| Table 6-4: Stride Access of 1-Cut GA           | 137  |

| Table 7-1: Ranking of the different techniques | 143  |

-

# **List of Figures**

| Figure 1-1: Cache Memory                        | 4  |

|-------------------------------------------------|----|

| Figure 1-2 : Cache Topologies                   | 8  |

| Figure 1-3: Memory Pipelining                   | 10 |

| Figure 1-4 : SIMD Model                         | 11 |

| Figure 1-5 : Simple Storage Schemes             | 15 |

| Figure 1-6: Bitwise Transformations             | 16 |

| Figure 2-1: Lawrie's Scheme with M=5 and P=4    | 22 |

| Figure 2-2: Row Skewing                         | 25 |

| Figure 2-3: Memories with Buffers               | 29 |

| Figure 2-4 : Space-Time-Multiplexed Memory      | 30 |

| Figure 3-1: Patterns a) sub-row, b) sub-column, | 35 |

| Figure 3-2: Address Sequence for s=2 and m=3    | 49 |

| Figure 3-3 :Address Sequence for s=6 and m=3    | 49 |

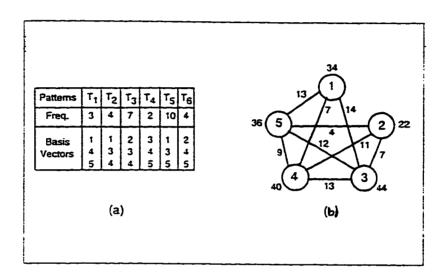

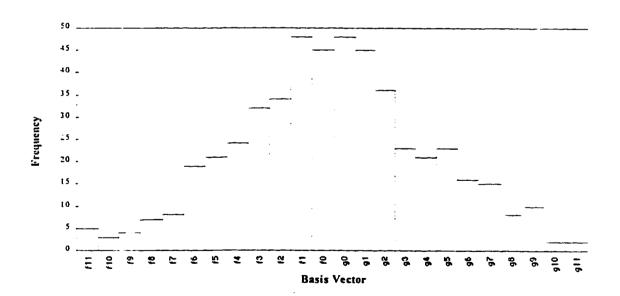

| Figure 4-1: Set of Pattern Bases and their Conflict Graph      | 54 |

|----------------------------------------------------------------|----|

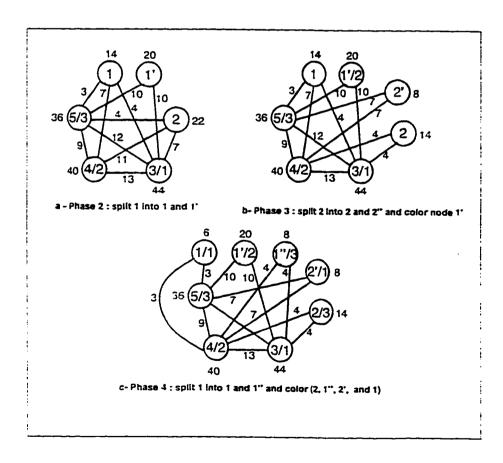

| Figure 4-2: Node Splitting by GC                               | 56 |

| Figure 4-3: Conflict Diagrams in Clustering                    | 60 |

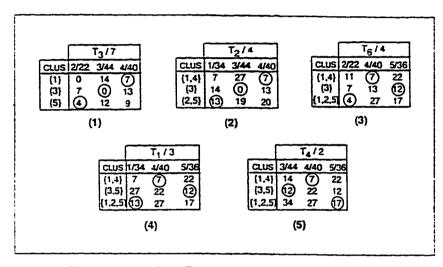

| Figure 4-4: The Merge/Split Heuristic                          | 66 |

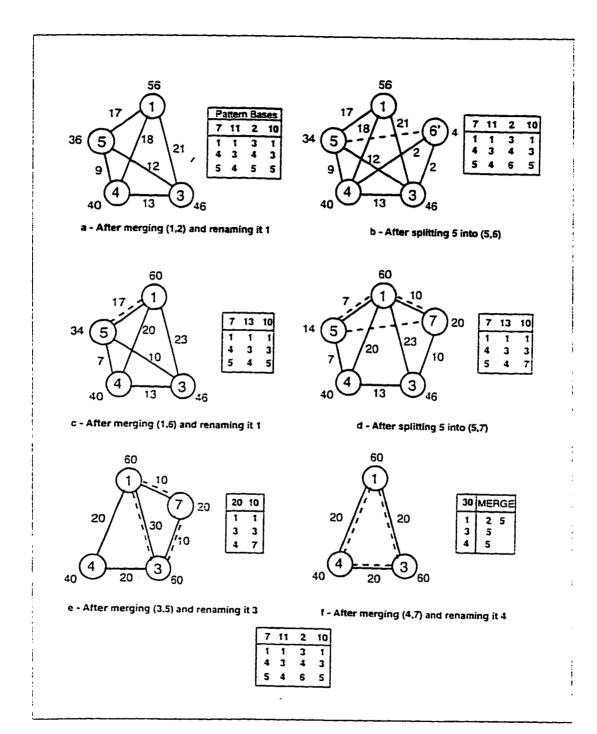

| Figure 4-5: Normal Distribution of Vectors                     | 70 |

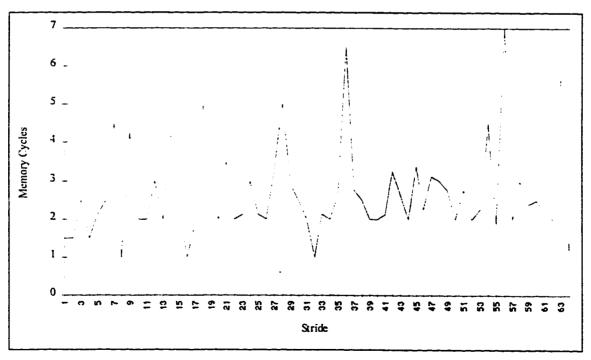

| Figure 4-6: Patterns Corresponding to Strides (1,2,,64)        | 74 |

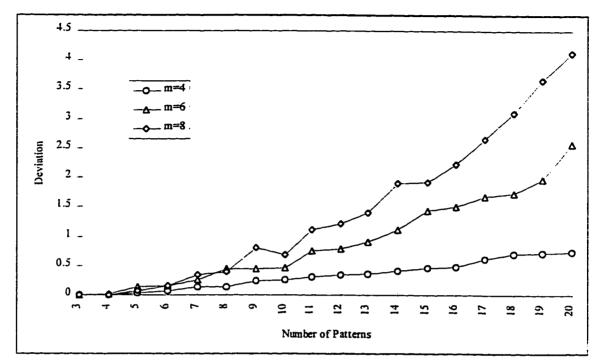

| Figure 4-7: Pattern Access of MS                               | 75 |

| Figure 4-8: Pattern Access of GC                               | 75 |

| Figure 4-9: Pattern Access of Clust                            | 76 |

| Figure 4-10: Pattern Access for m=8                            | 76 |

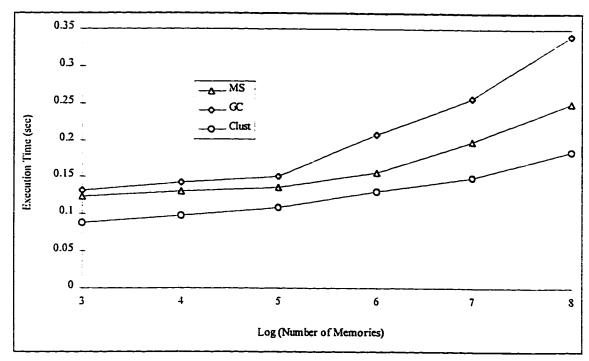

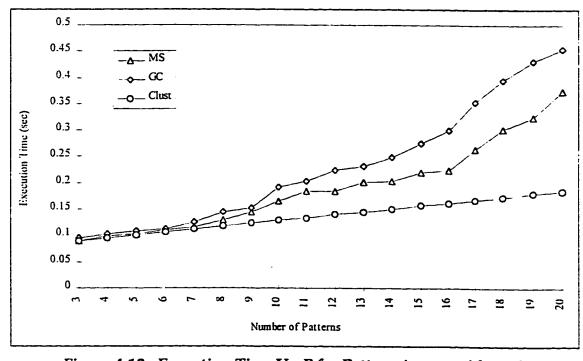

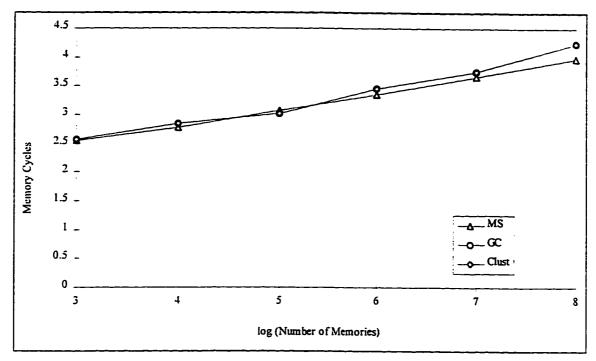

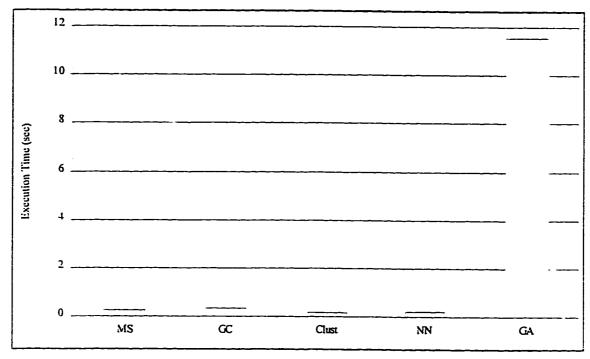

| Figure 4-11: Execution Time Vs. m for Pattern Access with P=20 | 78 |

| Figure 4-12: Execution Time Vs. P for Pattern Access with m=8  | 78 |

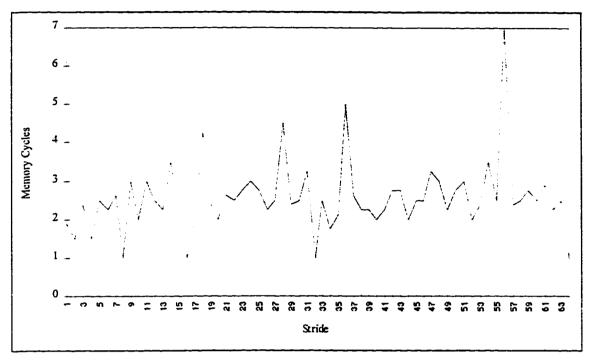

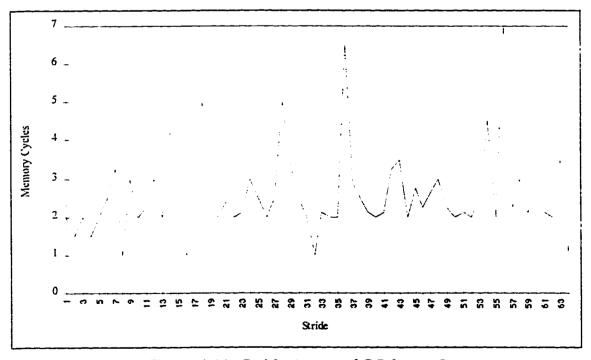

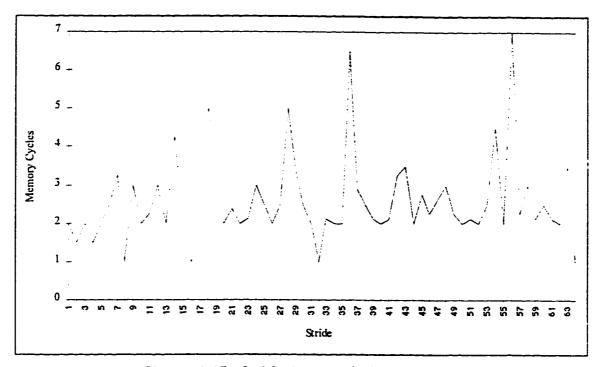

| Figure 4-13: Stride Access of MS for m=3                       | 79 |

| Figure 4-14: Stride Access of GC for m=3                       | 79 |

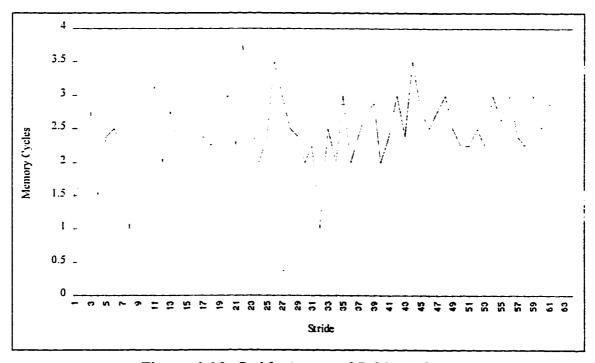

| Figure 4-15: Stride Access of Clust for m=3                    | 80 |

| Figure 4-16: Stride Access of Sohi's Solution | 80  |

|-----------------------------------------------|-----|

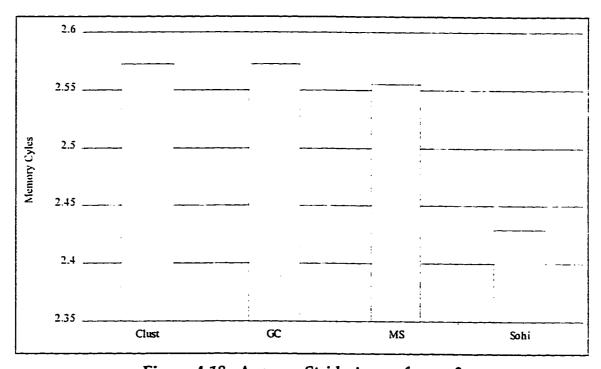

| Figure 4-17: Average Stride Access            | 81  |

| Figure 4-18: Average Stride Access for m=3    | 81  |

| Figure 5-1: Biological Neuron                 | 85  |

| Figure 5-2 : Artificial Neuron                | 88  |

| Figure 5-3: Forms of Output Function          | 89  |

| Figure 5-4 : Feedback Model                   | 91  |

| Figure 5-5 : Constructing Dissimilar Vectors  | 96  |

| Figure 5-6 : Architecture I Layout            | 97  |

| Figure 5-7 : Architecture I Connections       | 99  |

| Figure 5-8: The Update Algorithm              | 100 |

| Figure 5-9: Building The Storage Matrix       | 102 |

| Figure 5-10 : The Restricted Matrices         | 103 |

| Figure 5-11 : Architecture II Layout          | 104 |

| Figure 5-12 : Architecture II Connections     | 105 |

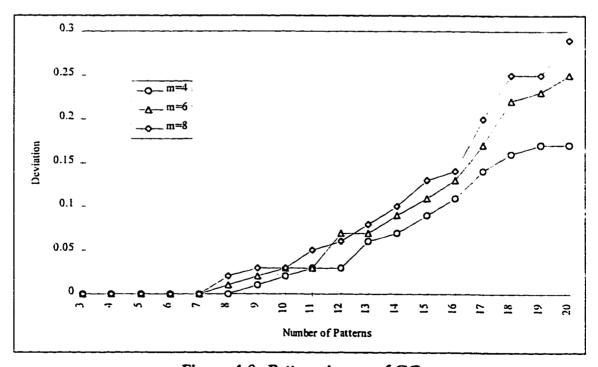

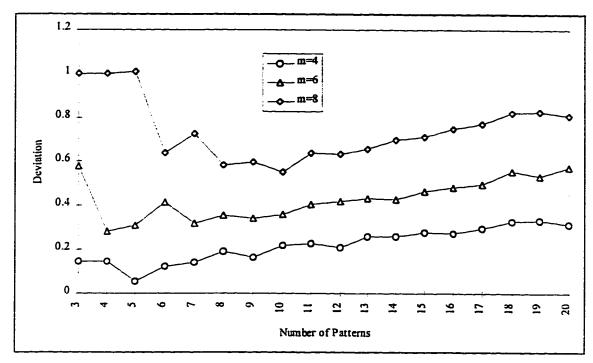

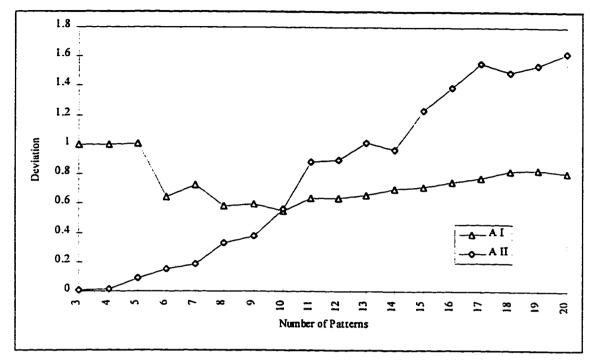

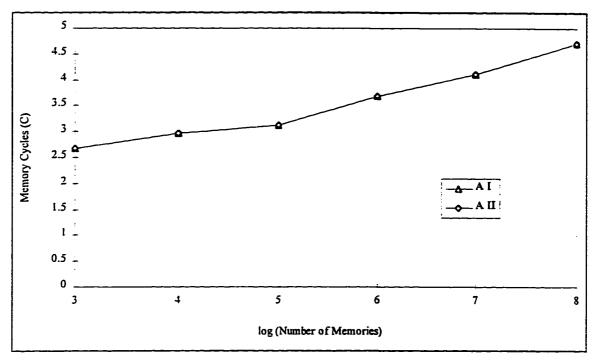

| Figure 5-13: Pattern Access of AI                   | 108 |

|-----------------------------------------------------|-----|

| Figure 5-14: Pattern Access of AII                  | 108 |

| Figure 5-15: Pattern Access for m=8                 | 109 |

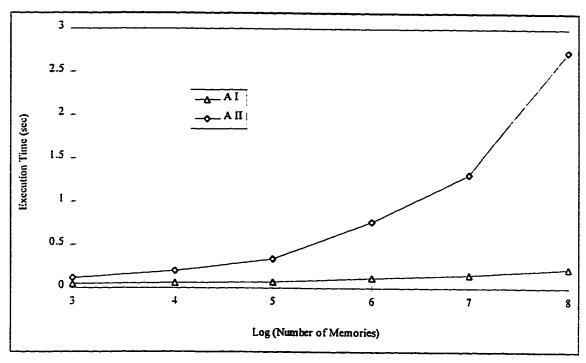

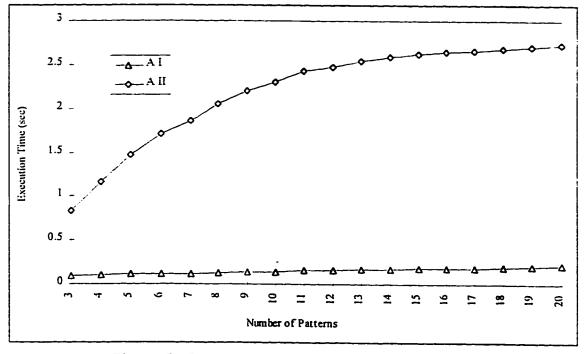

| Figure 5-16: Execution Time Vs. m of Pattern Access | 110 |

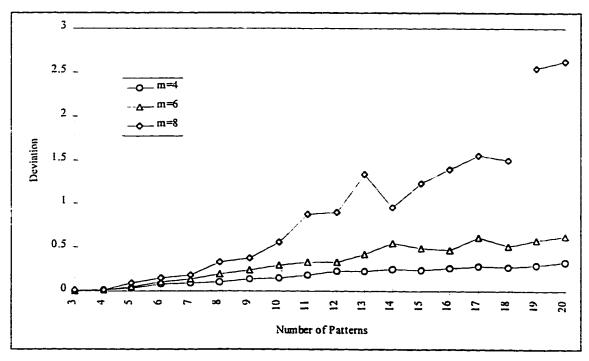

| Figure 5-17: Execution Time Vs. P of Pattern Access | 110 |

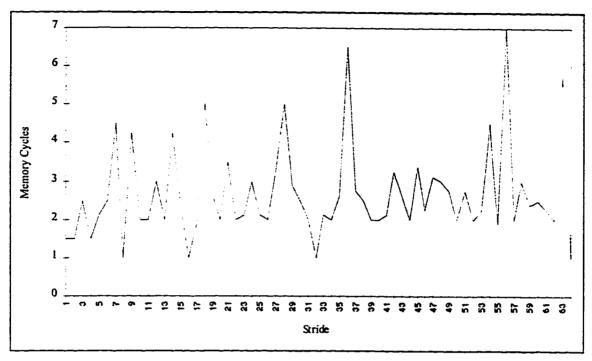

| Figure 5-18: Stride Access of AI for m=3            | 111 |

| Figure 5-19: Stride Access of AII for m=3           | 111 |

| Figure 5-20 : Average Stride Access of NN           | 112 |

| Figure 5-21: Average Stride Access for m=3          | 112 |

| Figure 6-1 : Encoding Scheme                        | 119 |

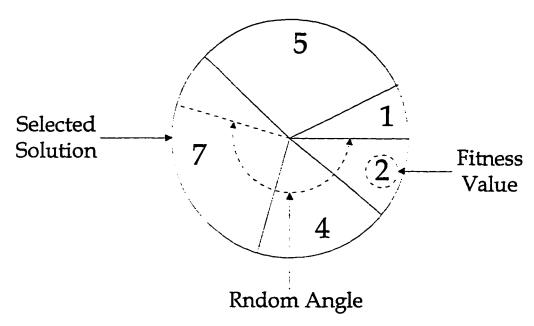

| Figure 6-2 : Roulette Wheel Method                  | 123 |

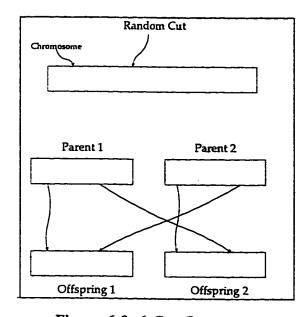

| Figure 6-3: 1-Cut Crossover                         | 124 |

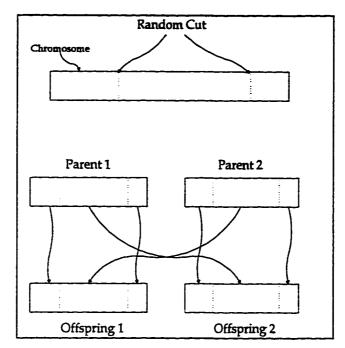

| Figure 6-4 : 2-Cut Crossover                        | 125 |

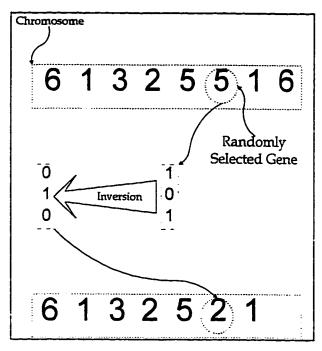

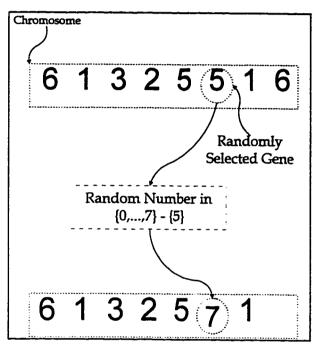

| Figure 6-5: Mutation by Inversion                   | 126 |

| Figure 6-6: Mutation by Random Number               | 127 |

| Figure 6-7: The GA                                         | 130 |

|------------------------------------------------------------|-----|

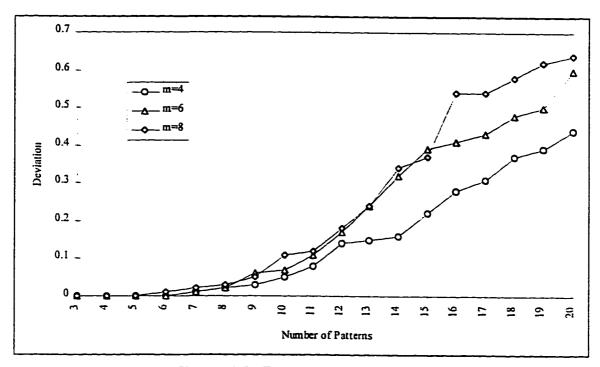

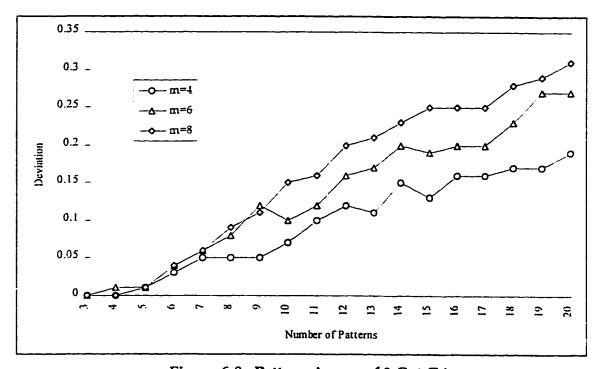

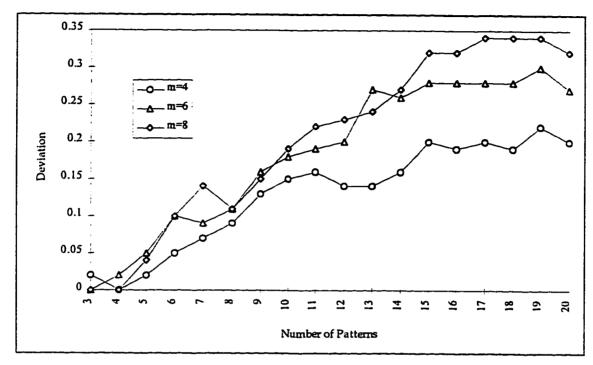

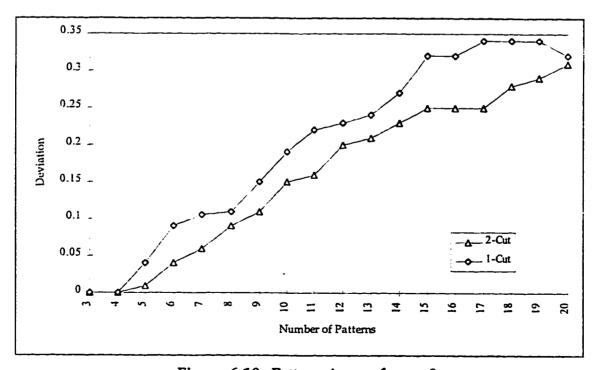

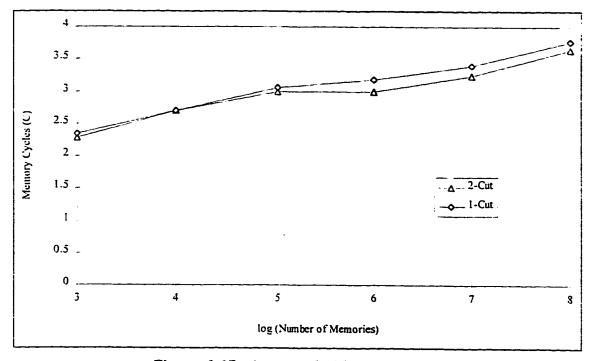

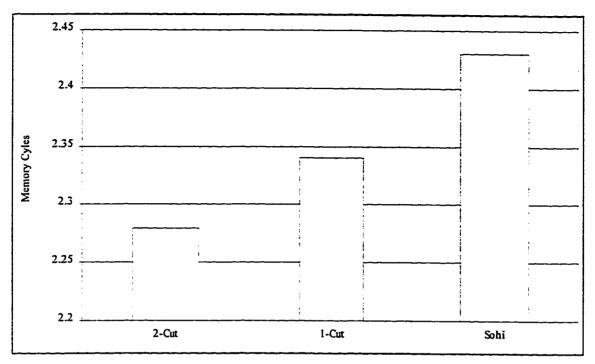

| Figure 6-8: Pattern Access of 2-Cut GA                     | 132 |

| Figure 6-9: Pattern Access of 1-Cut GA                     | 133 |

| Figure 6-10: Pattern Access for m=8                        | 133 |

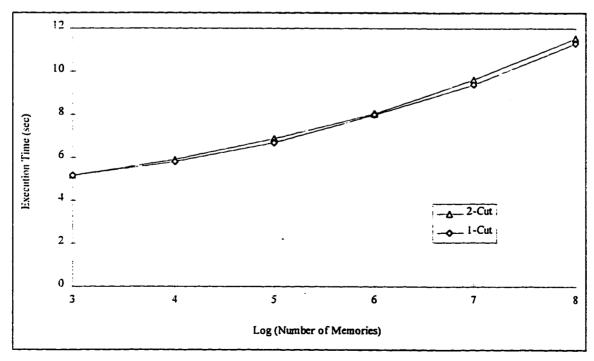

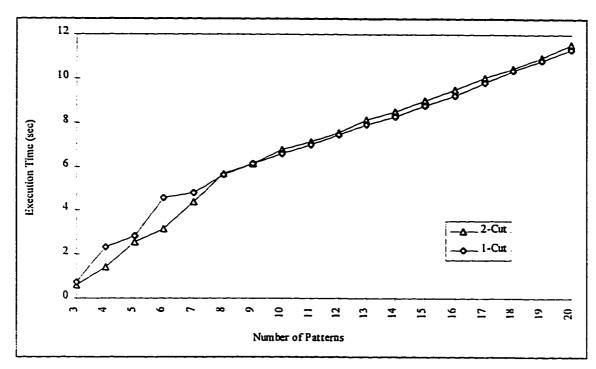

| Figure 6-11: Execution Time Vs. P of GA                    | 134 |

| Figure 6-12: Execution Time Vs. m of GA                    | 135 |

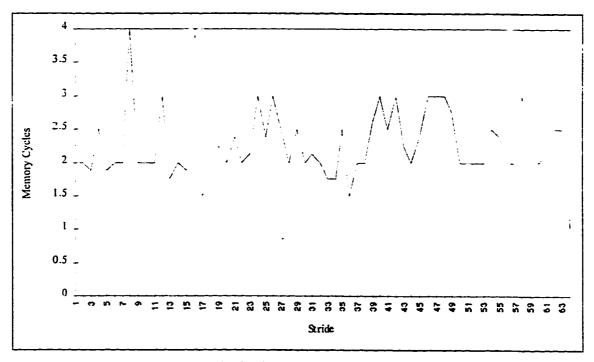

| Figure 6-13: Stride Access of 2-Cut GA                     | 135 |

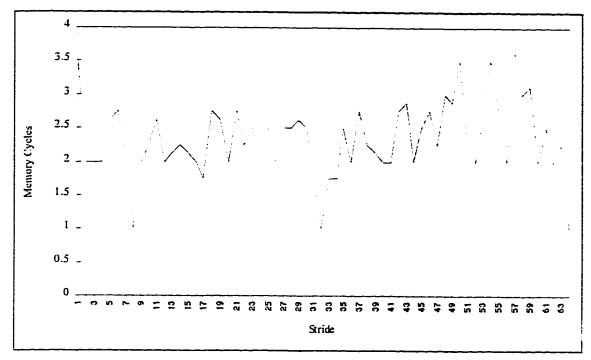

| Figure 6-14: Stride Access of 1-Cut GA                     | 136 |

| Figure 6-15: Average Stride Access of GA                   | 136 |

| Figure 6-16: Average Stride Access for m=3                 | 137 |

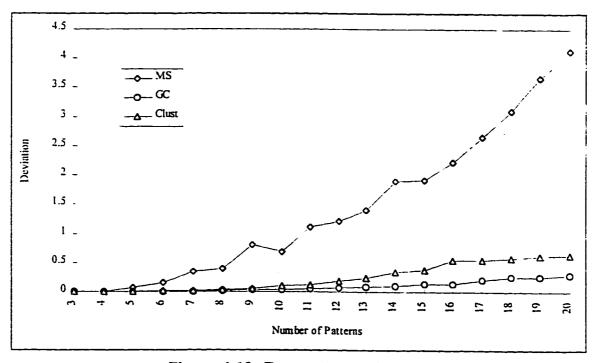

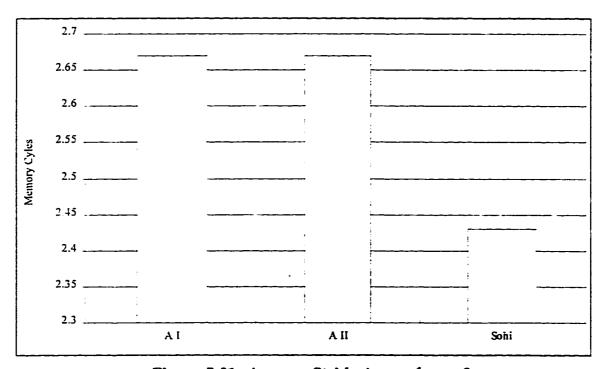

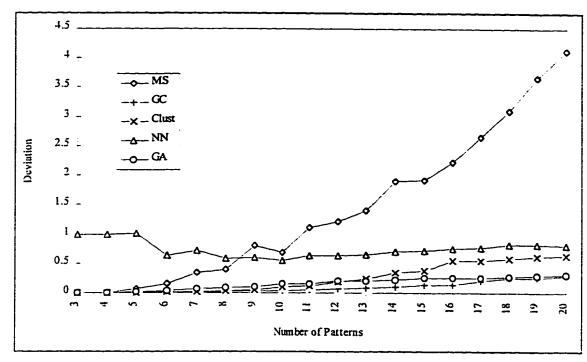

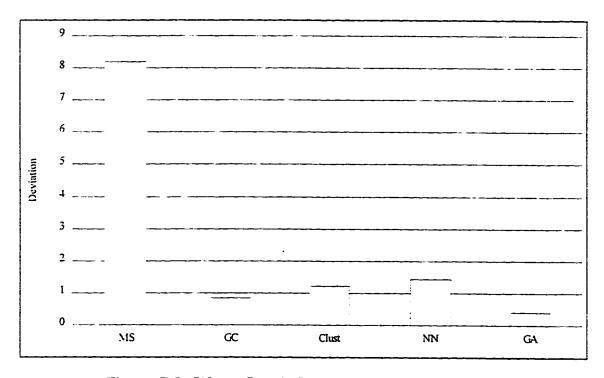

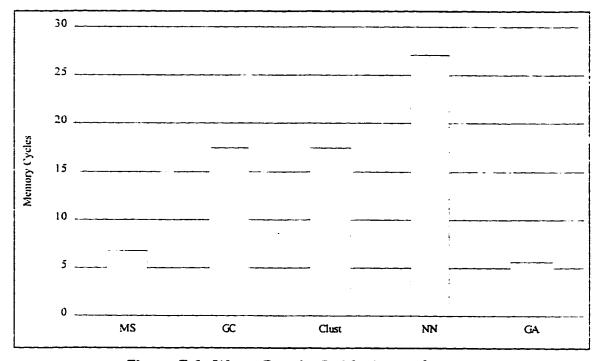

| Figure 7-1: Pattern Access for m=8                         | 140 |

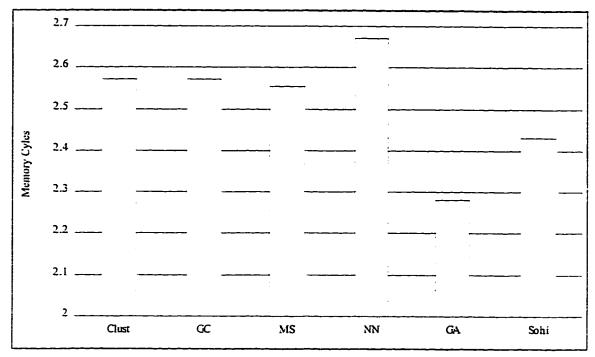

| Figure 7-2: Worst Case in Pattern Access for P=20,m=8      | 140 |

| Figure 7-3: Execution Time in Pattern Access for P=20, m=8 | 141 |

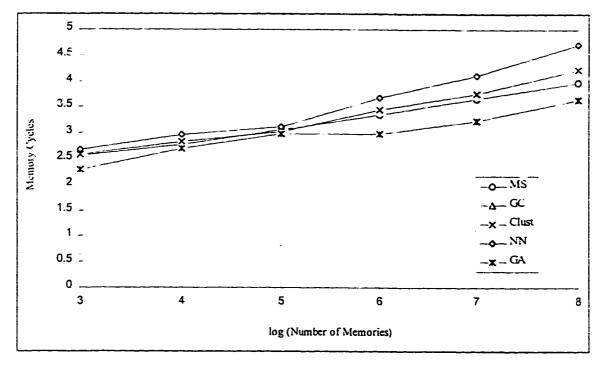

| Figure 7-4: Average Stride Access                          | 141 |

| Figure 7-5: Average Stride Access for m=3                  | 142 |

Figure 7-6: Worst Case in Stride Access for m=8

142

#### **Abstract**

Name:

Husam Saad Abu-Haimed

Title:

Organization of Parallel Memories

Major Field:

Computer Engineering

Date of Degree:

June 1997

The use of parallel memories has been the most promising technique to bridge the gap between high performance processors and available memories. By having N parallel memories, we aim to have a total memory bandwidth of NB, where B is the bandwidth of a single memory bank. However, using simple interleaving techniques, the effective bandwidth becomes much less than that and is about  $\sqrt{N}B$  [21]. This is because of serialization of memory access which happens when a number of elements that will be referenced at the same time are stored into the same memory bank. Having low memory throughput can severely affect the overall performance of vector machines and SIMD systems.

To minimize memory conflicts, researchers have considered storage schemes for conflict-free access of frequently used patterns like rows, columns, and power of 2 patterns and strides. In this thesis, we consider power of 2 patterns as well as arbitrary strides. A new approach for combining different patterns into one linear bitwise storage

scheme is proposed. We use 5 different approaches to construct combined storage schemes: 3 coloring-based heuristics, a Neural Networks approach, and a Genetic Algorithms approach.

In the case of power of 2 patterns, we were able to hit the lower bound on access time for small problems. For large problems, we achieved small deviations from the lower bound (5% -29%). In the case of arbitrary strides, access time of our schemes were 10% less than the best known bitwise schemes [41]. In addition, our schemes work with any power of 2 number of memories, while some other schemes work with a fixed number of memories like [41] which works with 8 memories.

Master of Science Degree

King Fahd University of Petroleum and Minerals

Dhahran, Saudi Arabia

June 1997

#### خلاصة الرسالة

الاسم: حسام سعد ابو حيمد

عنوان الرسالة: تنظيم الذاكرة المتوازية

التخصص: هندسة الحاسب الآلي

تاريخ الشهادة: يونيه ١٩٩٧

يعد استخدام الذاكرات المتوازية من اكثر الطبرق فعالية في وصل فجوة السرعة بين المعالجات عالية الأداء والذاكرات البطيئة الموجودة. N وحدة ذاكرة متوازية يأمل المصمون بالحصول على سرعة كلية تساوي N حيث أن N هي سرعة وحدة ذاكرة واحدة. لكن باستخدام طرق التخزين التقليدية تكون السرعة الفعلية لنظام الذاكرات المتوازية تساوي  $\sqrt{N}B$  وليس N [٢١]. هذا ناتج عن تسلسل عمليات الدخول للذاكرة والذي يحدث عندما يكون عدد من عناصر البيانات التي تستخدم في نفس الوقت موجودة في نفس وحدة الذاكرة.

ان انخفاض سرعة الذاكرة يؤثر بشكل كبير على الأداء العام في الأجهزة المتجهية (Vector Machines) وأجهزة (SIMD). لذا فقد أجريت عدة دراسات لحل هذه المشكلة منذ طرح الأجهزة المتجهية في منتصف الستينيات. فطور الباحثون الكثير من طرق التخزين الإزالة تعارضات الذاكرة (Memory conflicts) عند الدخول إلى النمانج (Patterns) كثيرة الاستخدام كالسطور، الأعمدة، الخطى (Strides) ونعانج القوة ۲ (Power of 2 patterns)

قي هذا البحث منقوم بدراسة طرق تخزين نعائج القوة ٢ بالإضافة إلى خطى الولوج العاسة (Arbitrary strides). سنقدم طريقة جنيدة لدمج نمائج مختلفة في خطة تخزين واحدة حيث نستخدم ه طرق مختلفة لبناء خطط التخزين (Storage schemes): ٣ طرق تقوم على تلوين الرسوم (Graph coloring)، طريقة تستخدم الشبكات العصبية، وطريقة تستخدم الخوارزميات الجينية.

في حالة نمانج القوة ٢، استطعنا إن نحقق الحد الأدنى لوقت الدخول لهذه النمانج في المسائل الصغيرة والمتوسطة. أما في المسائل الكبيرة فقد استطعنا تقليل الزيادة في وقت الدخول عن الحد الأدنى إلى ٥٪ - ٢٩٪ في حالة خطى الولوج العامة تمكنا من تحقيق تحسن بقدر /١٠ عن أفضل ما تمكن من تحقيقه الباحثون [٤١] بالإضافة إلى أن طريقتنا تعمل مع أي عدد (من القوة ٢) مسن الذاكراة على عكس ما في [٤١] والذي يعمل مع ٨ ذاكرات فقط

درجة الماجستير في العلوم جامعة الملك فهد للبترول والمعادن الظهران- المملكة العربية السعودية يونيه ١٩٩٧

# Chapter 1

#### 1. Introduction

The processing power needed by scientific and engineering applications like numerical analysis, image processing, artificial intelligence, and many other applications image been ever increasing. To satisfy these needs, the processing power of high performance processors has been increasing in a similar pace. However, for many applications like image processing and numerical analysis, the overall performance is highly affected by how fast a processor can get the information to be processed. In other words, the speed of the memory system can significantly affect the overall performance.

The bandwidth mismatch between fast processors and the available memories has been a main design problem for long time. Researchers and designers have been always looking for the right way of combining processing power and memory system architecture. Different ways have been in use to bridge the gap between processors and memories. The available techniques fall mainly into three categories: technology, software, and architecture.

#### 1.1 Technology

In the technology side, scientists have been pushing hard to go around undesired physical characteristics of memory devices. Physical characteristics like signal delay, races, and capacitive behavior have been the most significant obstacles of speeding up memory. Many of these characteristics have been negligible for long time, but started to cause problems for larger scales of integration. As the integration technology advances, many negligible effects become significant. Solving these problems is the aim of most technological research. In general, technology contributes to speeding memory up by the use of alternative technologies, wider buses, SRAM, and special interfaces.

#### 1.1.1 Alternative Technologies

Today, most of the industry relies on the use of CMOS technology which is cheaper than other technologies. With CMOS, much higher densities of memory devices can be integrated into a chip, which gives larger storage. Moreover, it consumes less power than other technologies like TTL and ECL. However, undesired physical characteristics like signal delay and capacitive behavior are encountered more in CMOS technology, which

makes it slower. To gain speed, other technologies like TTL and ECL (which have much faster switching) can be used, though that will be on the expense of cost and power consumption. ECL is much faster, but the most power consuming. BiCMOS is a hybrid technology of TTL and CMOS. It is faster than CMOS and less power consuming than TTL [32].

#### 1.1.2 Wider Buses

Memory speed can also be gained by increasing the memory bus width. Doing so allows transferring more data bits at the same memory cycle. Memory bus width ranges from 8-bit to 32-bit in different systems. The optimal width is the one that matches the memory bus with the system bus [32].

#### 1.1.3 Use of SRAM

The main problem of the main memory is being dynamic. In Dynamic RAM (DRAM), data bits are stored in capacitors. A data bit is read by draining out the current from the capacitor. So, the data bit has to be written back and the capacitor has to be recharged before reading it again. In addition, capacitors need to be refreshed because of the current leakage they have. This makes the memory cycle much longer. Another type of RAM is the Static RAM (SRAM). In SRAM, a data bit is stored in a flip-flop and a read cycle can start as soon as the previous one is complete. This makes SRAM much faster than

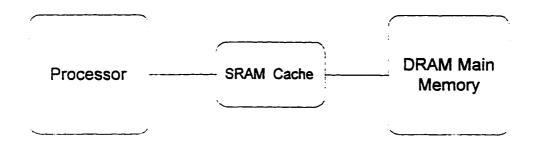

DRAM. Unfortunately, SRAM is about four times larger than DRAM and hence costs four times more [32]. So, we can not build the whole memory of SRAM, but it can be used as a cache memory. Cache is a small SRAM inserted between the processor and the memory. The cache holds data with high probability of being referenced and so avoids accessing the slow DRAM main memory as shown in Figure 1-1. Design issues of cache are discussed in section 1.3.1.

Figure 1-1: Cache Memory

#### 1.1.4 Special Interfaces

Another bottleneck is the interface between memory and processor. Several input/output modes were invented to enhance and speed up this interface [32]. When a memory row is selected by stropping its address, all data bits in that row appear on the output amplifiers. In random access mode, one column is selected and its bits appear on the output pins. In a page mode read operation, all the row data bits are held on the sense amplifiers while new column is selected. This way, no time is spent on writing the data on the amplifiers back to the memory cells and precharging before a new column in that row is selected. This

reduces the memory cycle if the data to be read lies in the same row. Various similar modes are in use like hyperpage mode [32].

In spite of the memory speedup achieved by technological development, it has some problems. First, it is bounded by physical limits. Signal speed inside memory chips is bounded by the speed of light and we are now very close to this limit; current signal speed is about  $\frac{1}{3}$  of the speed of light. Moreover, device dimensions are approaching the atomic level and further dimension reduction is becoming increasingly harder; compare the  $25\mu$  technology with the  $2.64\,\text{Å}$  diameter of the Silicon atom [23]. So, speeding memory up by increasing signal speed or reducing device dimensions is almost exhausted. Second, whenever memory speed is increased by technological developments. processor speed can be similarly increased, which means that the speed gap between processors and memories is still persistent and will result in low utilization of processing power.

#### 1.2 Software

Software and hardware are functionally equivalent, but with different cost and performance. Software can be thought of as an extension of hardware. We can not afford enough physical memory to hold all programs that may run concurrently, so we can emulate this memory in software by virtual memory and page swapping. Similarly, we can not afford a CPU for every program or user of a system, so we emulate this in

software by multitasking or timesharing. In these two cases we compensated for hardware by software to save cost on the expense of performance. But how can we use similar arguments to hide memory hardware latency by software and speed up the overall memory system.

If the memory technology used is slow or the memory organization does not deliver the needed throughput, the software can not change these inherent physical and hardwired characteristics of the memory system. The software can not boost the memory speed to match the processor speed. However, it can improve overall performance by trying to hide these undesired characteristics by mainly two techniques. First, by reducing the number of services requested from the systems slowest part, the memory. Second, by keeping the processor busy during the portion of time spent on waiting for memory.

#### 1.2.1 Minimizing Memory References

We can reduce the number of memory references by two means. First, by reducing the frequency of load and store operations. This is a compiler task. The compiler optimizes the code and efficiently schedules internal registers to minimize the number of load and store operations. Second, if it is necessary to use load or store operations, then try to make them to the cache instead of the main memory. This task is performed by the operating system. The memory management part of the operating system uses different algorithms to keep the most likely to be referenced pages in the cache. By doing so, the operating

system can hide the memory latency from the processor. There are many cache management algorithms and techniques in the literature. The performance of these algorithms is application dependent [45,48].

So, no matter how the compiler will optimize, the program must need access to the memory. And no matter what clever techniques the operating system will use to manage the cache, there will be cases where the main memory will be accessed (cache misses). So, software can virtually reduce the memory latency, but can not completely hide it.

#### 1.2.2 Reducing Idle Time

If the software can not completely hide the memory latency, it still has a chance of partially or completely hiding its effect on performance. This can be achieved by keeping the processor busy performing other tasks instead of waiting for the memory operation. Many techniques are in use to keep the processor busy while waiting for a memory request. This is an operating system and compilers task. The operating system can switch to another process after issuing a memory request to minimize idle time. The compiler also can find pieces of code that can run in parallel so that the operating system can switch from one to another. The trend of multithreading is an example of such techniques that can be used to reduce the processor idle time.

#### 1.3 Architecture

As discussed in previous sections, technology and software approaches have been used to speed up the memory. However, these approaches still have their limitations. Beyond these two approaches we are left with the other alternative approach, which is the architectural organization of the memory system. Research in memory architecture has been going in two directions: cache architectures and parallel architectures.

#### 1.3.1 Cache Architecture

As mentioned in section 1.1.3, cache is a small SRAM inserted between processor and main memory. The cache memory function is based on the concept of data locality. The processor accesses a relatively small amount of data in each time window. The cache

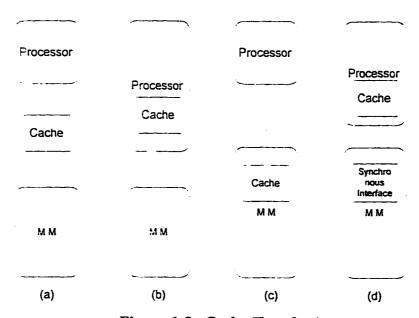

Figure 1-2: Cache Topologies

memory is intended to capture the essential data by the program so that, main memory access time is hidden by the small access time of the cache. There are various cache topologies having different properties. Figure 1-2 [32] shows four different topologies. In the simplest form, cache is inserted between processor and main memory as in (a). In (b), the cache is embedded to the processor to avoid input/output delays and to match the memory bus with the wide processor bus. In (c), it is embedded to the main memory to connect the fast cache to the wide internal DRAM bus. In (d), the cache is embedded in the processor and a synchronous interface is embedded in the main memory to deliver fast bursts of data to the cache [32].

It is observed that the cache memory concept has some limitations. It seams that there is some limitation on increasing throughput beyond some cache size and organization. The limit results from two conflicting effects: temporal locality and spatial locality. The first requires small page size while the second requires the opposite. Since any program contains a mixture of the two (temporal locality and spatial locality), it is possible to find some cache size and organization that is suitable for a typical program but not necessarily for other programs [32].

#### 1.3.2 Parallel Memory Architecture

The other architectural direction is the parallel memory organization. This approach can be divided into two categories: time parallelism and space parallelism.

#### 1.4 Time Parallelism

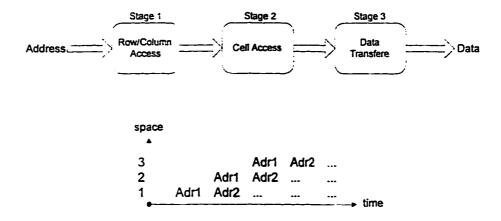

In this approach, the memory access process is decomposed into a number of independent stages. When a memory access request is done with one stage, it can go to the next one and the previous stage can start processing another request. In other words, different memory requests can be overlapped. This is memory pipelining. A possible memory access decomposition is shown in Figure 1-3. In this example, it is decomposed into three stages. Unlike instruction execution pipelines, where up to 20 stages or more can be exploited, it is hard to decompose memory access process into more than about three stages. This puts a limit on the gain of memory pipelining or time parallelism [21].

Figure 1-3: Memory Pipelining

# 1.5 Space Parallelism

In time parallelism, different requests are processed by different stages representing different processing steps. In space parallelism, however, identical units process in

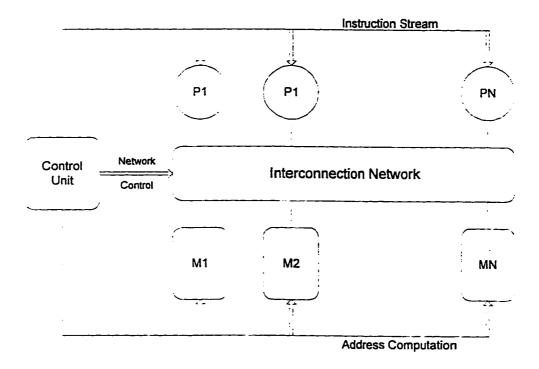

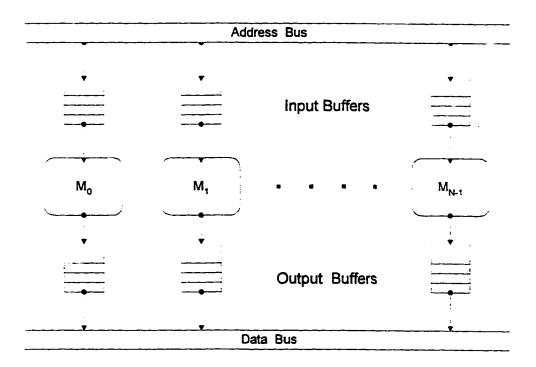

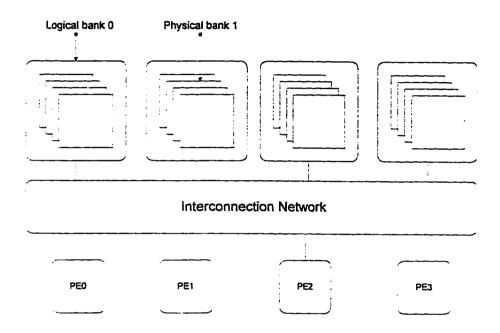

parallel different requests. In other words, the memory is divided into identical memory banks so that, a number of memory requests can be processed at the same time. In this scheme, in general, a number of memory banks or memory modules (M) is connected through a network to a processor or in the general case to a number of processors (P). So, any processor  $p_i$  can access memory bank  $m_j$  by alignment through the network. One well-known example of this model is the SIMD computer shown in Figure 1-4. By using this scheme, we can achieve in the optimal case a memory speedup of M, which means

Figure 1-4: SIMD Model

that the processor/memory speed gap will be significantly reduced or completely eliminated. By using M parallel memories, it is expected that the average bandwidth is  $MB_m$ , where  $B_m$  is the bandwidth of one memory bank. Unfortunately, due to

serialization of addresses at the input of some memory banks, the effective bandwidth is far from being linear ( $MB_m$ ). The reason is that due to data organization a request can not be decomposed into requests to all M memory banks, because many data elements fall into the same memory bank. An effective bandwidth given by Hwang [21], is  $B_{parallel} = \sqrt{M}B_m$ .

To achieve an optimal memory access, all the data elements that will be accessed at the same time should be stored into different memory banks. In many cases, this condition is difficult or impossible to be met. That may result in severe performance degradation of many orders. Consider the case were we have k data elements that will be needed at the same time, but are stored into the same memory bank. At least k memory cycles will be needed to access these k elements instead of  $\left\lceil \frac{k}{M} \right\rceil$  cycles in the optimal case. To avoid or minimize this problem, we have to consider the data patterns that will be accessed by the program and predefine storage mappings that minimize access conflicts for these specific patterns. The task of finding out these data patterns is performed by a parallelizing compiler. Parallelizing compilers have to perform data dependence analysis in order to parallelize a given code.

As an example of simple data patterns, consider the case where the pattern is a set of consecutive data elements in an array. Low Order Interleaving (LOI) can be used in this case. In LOI, consecutive array elements are stored into consecutive memory banks.

For example, if element  $e_i$  is stored into memory bank  $m_i$ , then element  $e_{i+1}$  is stored into memory bank  $m_{(j+1) \mod M}$ . If we have  $2^m$  memory banks and d-bit array element address, then LOI can be implemented by taking the least significant n bits of the d-bit  $(n \le d)$  address as the memory bank number in which that array element should be stored. For example, the element  $e_i$  whose address in the array is  $i_{d-1}i_{d-2}...i_{n-1}...i_0$  will be stored into memory bank  $m_j$  where  $j = i_{n-1}i_{n-2}...i_0$ . LOI helps only with patterns in which the least significant n bits of addresses take all the possible combinations for all the elements in the pattern. A set of consecutive elements is a special case of such patterns. However, many other patterns are frequently needed by different types of applications. Consider the situation where a program references array elements with stride 2 (stride is the difference between two consecutive elements in the pattern) and we have  $2^m$  memory banks. Now if LOI is used, only half of the memory banks will be used, those even numbered, and the memory throughput will drop to half the optimal. In general, if the stride is  $2^s$  with  $2^m$  memory banks and LOI,  $2^s$  cycles will be needed to access  $2^m$ elements instead of 1 cycle in the optimal case.

#### 1.5.1 Prime Memory Systems

A more general case is for any stride S and M memory banks (S, M) are any integers). Let g be the greatest common divisor of S and M, g = GCD(S, M). Then, it can be shown using number theory that g cycles will be needed to access a pattern of M elements if

LOI is used [7,25]. Many techniques were proposed to solve this problem [7,14,25,38]. One proposed solution is to have S and M relatively prime [7], i.e., GCD(S, M) = 1. This leads to the optimal case and M elements can be read in one cycle. If M is a prime number, then for any stride S that is not a multiple of M then, GCD(S, M) = 1 and we can achieve the perfect access.

This scheme will guarantee conflict-free access for any number of patterns P with strides  $s_1, s_2, ..., s_P$  such that,  $GCD(s_i, M) = 1$ ;  $1 \le i \le P$ . However, this scheme is computationally expensive and time consuming because it needs to compute the *modulo* function. In the case where S and M are power of two, the *modulo* function is just a shift operation. In the general case where S and M can be any numbers, however, it will cost much more. Implementing the modulo function in hardware is difficult while implementing it in software is time consuming.

#### 1.5.2 Skewing Schemes

Other approaches were introduced to avoid computing the *modulo* function [4,13,18,19,20,31]. Many of these approaches rely on observing the data patterns frequently needed by different applications and then constructing priori mappings of data elements so that these patterns could be accessed with minimum conflicts, though other patterns might not. Examples of frequently used patterns are columns, rows, diagonals, and square blocks. Figure 1-5 shows three simple storage schemes of such patterns. The

numbers in bold are the row and column indices. The numbers inside indicate the memory bank number in which the corresponding array element should be stored. In (a), elements in one column are stored into different memory banks which means that they can be accessed in parallel. However, elements in one row are stored into one memory bank. The scheme in (b) gives conflict-free access to columns as well as to rows as can be seen. Scheme (c) adds another pattern and gives conflict-free access to square blocks of size  $2 \times 2$ . By having these patterns known in advance, storage schemes or mappings that give conflict-free access to these patterns are predefined. Such schemes are good for applications were predefined patterns constitute most of the actually accessed patterns. Other applications with more general or irregular patterns will suffer severe degradations.

|     | 0 | 1 | 2 | 3 |     |   | 0 | 1 | 2   | 3 |   | 0 | 1 | 2 | 3 |

|-----|---|---|---|---|-----|---|---|---|-----|---|---|---|---|---|---|

| 0   | 0 | 0 | 0 | 0 |     | 0 | 0 | 1 | 2   | 3 | 0 | 0 | 2 | 1 | 3 |

| 1   | 1 | 1 | 1 | 1 | •   | 1 | 1 | 0 | 3   | 2 | 1 | 1 | 3 | 0 | 2 |

| 2   | 2 | 2 | 2 | 2 | ,   | 2 | 2 | 3 | 0   | 1 | 2 | 2 | 0 | 3 | 1 |

| 3   | 3 | 3 | 3 | 3 |     | 3 | 3 | 2 | 1   | 0 | 3 | 3 | 1 | 2 | 0 |

| (a) |   |   |   |   | (b) |   |   |   | (c) |   |   |   |   |   |   |

Figure 1-5: Simple Storage Schemes

## 1.5.3 Bitwise Address Transformation Schemes

Looking for more general and efficient schemes, several Bitwise Address Transformations (BAT) were proposed. In this section, linear BAT schemes will be discussed, while general BAT schemes will be discussed in section 2.5. Linear

transformations map the addresses generated by the program into memory banks. The d-bit address generated by the program is multiplied by a linear transformation matrix  $M_{d\times n}$  to generate an n-bit address that is the memory bank number in which that array element is to be stored. In the matrix multiplication process, the logical AND corresponds to scalar multiplication while XOR corresponds to addition. This transformation is simple and efficient; all what it needs is ANDing followed by XORing. Its simplicity makes it suitable for hardware implementation which means fast operation. Many known schemes can be represented by linear transformations. The schemes shown in Figure 1-5 can be represented in linear transformation forms as shown in Figure 1-6.

$$(a) \binom{m_0}{m_1} = \begin{pmatrix} 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \end{pmatrix} \binom{j_1}{j_0} i_1 i_2 k_3$$

$$(b) \binom{m_0}{m_1} = \begin{pmatrix} 1 & 0 & 1 & 0 \\ 0 & 1 & 0 & 1 \end{pmatrix} \binom{j_1}{j_0} i_1 i_2 k_3$$

$$(c) \binom{m_0}{m_1} = \begin{pmatrix} 1 & 0 & 0 & 1 \\ 0 & 1 & 1 & 0 \end{pmatrix} \binom{j_1}{j_0} i_1 i_2 k_3$$

Figure 1-6: Bitwise Transformations

These are linear transformations of the form  $m_{2\times 1}=M_{2\times 4}\times X_{4\times 1}$ , where m is the memory bank number, M is the transformation matrix, X is the array element address, and j and i represent the column index and row index, respectively. Linear transformation schemes can be used with many other types of regular or irregular data patterns. They were used in situations with single power-of-two stride and perfect access was guaranteed. However, with no satisfying solutions arise in situations with multiple patterns and with nonpower-of-two strides.

# Chapter 2

## 2. Literature Review

## 2.1 Background

Rather than just increasing the speed of scalar computations, vector parallelism has been heavily studied and implemented since 1965. This is due to the ease of detecting and exploiting this type of parallelism [25,38]. Vector processing is utilized in vector machines and in SIMD machines. In such machines, a set of memory words belonging to some vector are read and processed in parallel. Sohi [41] noticed that cache memories were not able to provide vector machines with high-bandwidth access to elements of large data structures, which necessitates the use of parallel or interleaved memories. Seznec and Lenfant [37] noticed that parallel memories in SIMD machines have to be synchronized. They showed that an SIMD machine without synchronization will have about 38% of the

theoretical throughput, while this throughput can be increased to 50% just by synchronizing the memories without changing the storage scheme.

The unability to access vector elements in parallel can significantly decrease the memory throughput and affect the overall performance. Such cases happen when more than one element belonging to the same vector are stored into the same memory bank, which causes memory access conflict. This problem has been the subject of many studies since the late 1960's. The degree of conflict depends on the access stride. If the stride is relatively prime with the number of memory banks, perfect access can be easily achieved. Problems, however, arise with other strides. In [37], Seznec and Lenfant considered a stride distribution collected from real applications. The distribution was as follows:

- 80% of the vectors are accessed with stride 1.

- 10% of the vectors are accessed with odd strides other than 1.

- for  $k \ge 1, \frac{10}{2^k}$ % of the accessed vectors have strides of the form  $r2^k$ , where r is an odd number.

The study showed that having  $N=2^n$  memories, then accessing 100 N-element vectors using simple interleaving techniques will result in 55% of the throughput for n=9. Though only 10% of the strides are not conflict-free accessible, this small portion may cause severe degradation.

As shown above, using simple interleaving techniques, one can waste about 50% of the memory throughput. Since the introduction of Illiac IV in the late 1960's, researchers have developed many techniques to avoid this waste by avoiding memory conflicts. These techniques belong to three classes: Prime Memory Systems (PMS), Skewing schemes, and Bitwise Address Transformations.

## 2.2 Regular Data Patterns

Before discussing the different storage schemes, let's look at the kind of data patterns usually considered in these schemes. In a system of M memories each of K words, Budnik [7] showed that the ratio between all possible M-element vectors and those that are accessible in parallel is approximately  $\left(\frac{1}{2\pi M}\right)^{\frac{1}{2}}e^{M}$ . So, there is storage scheme(s) that allow conflict-free access to all possible patterns. So, it is beneficial to consider only those patterns that are expected in practice rather than considering arbitrary patterns. That is why all studies in the literature considered frequently used patterns like rows, columns, diagonals, and power-of-two patterns and strides of the form  $r2^x$  for odd r. Budnik also showed that the ratio between differently ordered vectors and uniquely ordered vectors is  $M^{M-1}$ . So, it is of great benefit to have a reskewing interconnection scheme between processors and memories. By having such scheme, we can consider a vector instance without considering its order. A crossbar switch gives optimal connection and can reskew a vector in any order, but it is very expensive for large systems. Multistage

interconnection networks are the best and most widely used alternative. Constructing a storage scheme for these networks is more difficult because it has to avoid network conflict in data realignment or reskewing.

## 2.3 Prime Memory Systems (PMS)

Budnik [7] and Lawrie [25] showed that if the number of memory banks and the access strides are relatively prime, then these strides can be accessed without conflict. Budnik proposed row rotation scheme, in which, every row of the array is rotated with respect to the previous row with a distance d. They showed that when a' is relatively prime with the number of memory banks, then columns, rows, and square blocks can be accessed in parallel. They applied their scheme for the case of  $2^l + 1$  memories and  $d = 2^{2l} + 1$  and for other cases also.

In a conventional PMS, the mapping is defined as follows:

$$F(A) = A \mod M$$

$$r(A) = A / M$$

Where F is the memory bank to which A is mapped and r is the offset of A in that memory bank. Computing this address is expensive; it needs computing the *modulo* function in addition to integer division to find r(A). These two operations are complex and can cause a lot of overhead. Gao [14] proposed a high speed multiple-bit division approach which includes the approach to find " $A \mod M$ " by parallel "l-bit cycle adder"

in one step when  $M=2^l\pm 1$ . Many other techniques were proposed to compute the *modulo* function. Lawrie [25] proposed the use of prime number of memories and  $P=2^p$  processors. He redefined the PMS mappings to be:

$$F(A) = A \bmod M$$

$$r(A) = A / P$$

By dividing over P instead of M, scheme avoids dividing by a prime number and instead uses a very simple division, since P is a power of two. This fast address computation is on the expense of memory wastage. Since P < M, only  $\frac{P}{M}$  of the memory space is used, while  $1 - \frac{P}{M}$  of the memory is wasted in what is called *holes*. A possible combination could be M = 257 and P = 256. In this case,  $\frac{1}{257}$  of the memory is wasted. Figure 2-1 shows this mapping for M = 5 and P = 4.

|   | MO   | M1   | M2   | МЗ   | M4   |

|---|------|------|------|------|------|

| 0 | 0    | 1    | 2    | 3    | hole |

| 1 | 5    | 6    | 7    | hole | 4    |

| 2 | 10   | 11   | hole | 8    | 9    |

| 3 | 15   | hole | 12   | 13   | 14   |

| 4 | hole | 16   | 17   | 18   | 19   |

| 5 | 20   | 21   | 22   | 23   | hole |

| 6 | 25   | 26   | 27   | hole | 24   |

Figure 2-1: Lawrie's Scheme with M=5 and P=4

Gao [14] and Seznec and Lnfant [38] proposed a new mapping:

$$F(A) = A \bmod M$$

$$r(A) = A \bmod C$$

Where  $C=2^c$  is the number of words per memory bank. By having  $M=2^c\pm 1$ , we make M and C relatively prime. They showed using the Chinese remainder theorem that this mapping is a one-to-one mapping from the address space  $\{0,..., M\times 2^c-1\}$  onto the set of memory words of the memory system. In this scheme integer division is avoided and in computing r(A) only modulo with respect to  $C=2^c$  is computed which is a very simple operation; it is just the least significant c bits of A.

A major problem with PMS schemes is realigning data to processors. This alignment is very complex. In [38], they proposed a special network called the Chinese remainder network. However, this network is complex and specific to this application. In addition to this, computing the addresses in PMS schemes is very complex. Although fast hardware was proposed to compute the *modulo* function, it still causes some overhead and requires very complex hardware. Moreover, it is desired to have power-of-two number (that is not prime) of memories and processors for the following reasons [13]:

- 1. It simplifies address computation.

- 2. It allows the use of most efficient interconnection networks.

- 3. It achieves optimal utilization of address decoders.

## 2.4 Skewing Schemes

A skewing scheme is defined in the literature to be a scheme that does not use a prime number of memories. Most skewing schemes are linear. Linear schemes are of the form  $F(i,j) = (ai + bj) \mod M$  for some constants a and b, where i and j are the indices of the corresponding element. In computing F(i,j), arithmetic and modulus operations are needed. When bitwise logical operations are used instead of arithmetic and modulus operations (for example,  $F(i,j) = i \oplus j$ ), the scheme is called bitwise transformation. All skewing schemes are periodic. The class of linear schemes is a proper subclass of the class of periodic schemes [11].

Patterns like rows and columns can be accessed without conflict using linear skewing schemes. However, Lawrie [26] and Budnik [7] showed that patterns like diagonals and coils are nonlinear and there is no linear skewing scheme to access such patterns with  $2^n$  memories, where n > 1. Shapiro [39] claimed that  $T = \{row, column, diagonal, square, block\}$  has no valid skewing scheme (a scheme that gives conflict-free access), but Deb [10] presented a counter example to that claim by presenting a valid nonlinear scheme of T for n = 2. Then, Raghavendra [4] gave a general algorithm that finds a nonlinear skewing scheme for any n.

Wijshoff and Leeuwen [47] studied periodic skewing schemes and showed various properties of these schemes in light of foundations in the mathematical theory of integral latices and  $\overset{\checkmark}{Z}$ -modulus.

Harper [18] proposed the use of dynamic storage schemes, in which a storage scheme is selected for each vector based on the access patterns used with that vector. He synthesized storage schemes for  $r2^x$  stride families, where r is an odd number. It was shown that if a storage scheme gives conflict-free access to a stride  $2^x$ , then it will also give access to any stride  $r2^x$  for any odd r, but not for any other x. These schemes rely on skewing every period of addresses generated by a linear scheme with respect to the previous period. This scheme is shown in Figure 2-2. The performance of this scheme was studied for arbitrary strides and simulation showed that using buffers can improve throughput for nonconflict-free strides.

|     | <b>M</b> 0 | M1 | M2 | M3 |

|-----|------------|----|----|----|

| . 0 | 0          | 1  | 2  | 3  |

| 1   | 7          | 4  | 5  | 6  |

| 2   | 10         | 11 | 8  | 9  |

| 3   | 13         | 14 | 15 | 12 |

| 4   | 16         | 17 | 18 | 19 |

| 5   | 23         | 20 | 21 | 22 |

| 6   | 26         | 27 | 24 | 25 |

Figure 2-2: Row Skewing

To solve the problem with nonlinear patterns like diagonals and coils, Deb [11] proposed a multiskewing scheme. In multiskewing, an array is divided into parts and each part is stored using a different linear storage scheme. Deb showed that storing an array with different linear schemes enables conflict-free access of nonlinear patterns. He then gave an instance of such schemes and showed that all conventional linear patterns in addition to diagonals and coils can be accessed without conflict.

#### 2.5 Bitwise Address Transformations

Bitwise address transformation schemes are skewing schemes that use bitwise logical instead of arithmetic operations in address computations. In [19,34,41,46] the advantages of using bitwise address transformations over the other schemes were discussed:

- 1. Use of simple logical operations rather than arithmetic and modulus operations.

- 2. Simple control of cheap, general, and well studied interconnection networks.

- 3. Compact representation as logical operations and Boolean matrices.

- 4. Bitwise operations have no carry which makes the complexity of address computation independent of the number of memories.

- 5. Data movement is fast and efficient and can be pipelined through the interconnection network.

Frailong, Jalby, and Lenfant [13] developed a general power-of-two data pattern that covers many conventional patterns like rows, columns, grids, and rectangles. They proposed an XOR-scheme of the form:  $F(i,j) = Ai \oplus Bj$ , where A and B are Boolean matrices. They identified the necessary and sufficient conditions for conflict-free access of these patterns and identified the conditions for their scheme to pass the  $\Omega$  network. Norton and Melton [31] synthesized the first bitwise linear transformation scheme for conflict-free access of power-of-two strides and formulated the conditions for their scheme to pass the baseline network. They also gave an efficient procedure for constructing Boolean matrices representing these storage schemes.

Lee and Wang [27] tried to apply bitwise schemes for the pattern set T. To achieve so, they used a nonlinear bitwise scheme defined as follows:

$$F(i,j) = i \oplus Pj \oplus j_0$$

$$r(i,j) = i$$

Here P is a Boolean matrix. They showed that this scheme gives conflict-free access of T. However, data realignment is very complex. Processors are connected to memories with an indirect binary n-cube network in addition to a reverse shuffle network connecting processors with each other. Raghavendra and Boppana [34] defined a similar mapping:

$$F(i,j) = i \oplus Pj$$

$$r(i,j) = i$$

This is a valid scheme for T. They used an  $\Omega$  network with some additional hardware for data realignment. This solution uses half the number of memories and network size of those used in Lawrie's scheme. Boppana and Raghavendra modified this scheme to work with the inverse  $\Omega$  network [6,34].

Most of the storage schemes try to provide conflict-free access of known patterns like T or strides of the form  $r2^x$ . But the use of these schemes with other patterns and strides significantly degrades the throughput [18,41,46]. [18,41,46] studied this problem and proposed the use of buffers at memory inputs and outputs (Figure 2-3) and presented simulation results that showed the profitability of using these buffers. Valero [46] uses buffers with a reordering technique. In reordering, elements of a given nonconflict-free stride are read into buffers in consecutive memory cycles (other vectors can be read during these cycles) and then reordered and given to processors. Valero showed that using buffers without reordering can lead to a maximum latency of  $\frac{L(T-1)}{T}$  cycles, where L is the length of the vector stream to be read and  $T=2^t$  is the ratio between processor and memory cycle. This needs  $\frac{L}{T} - \left\lceil \frac{L}{T^2} \right\rceil$  buffers per memory bank. With reordering, however. at most T-1 extra cycles will be needed to read a stream of length L.

Harper [19] expressed the conflict-free access conditions of a  $r2^x$  stride in terms of the periodicity of the transformation matrix and used elementary matrices of known periods to compose transformation matrices of maximum period for optimal access.

In all the previous schemes, a space multiplexed memory system was assumed. Seznec and Lenfant [37] proposed the use of time multiplexed as well as space multiplexed memory system. This system is shown in Figure 2-4. The system consists of P processors and N logical memory banks where  $P = N = 2^n$ . Each logical memory bank consists of  $2^d$  physical banks. They used XOR scheme on different fields of the array element address to compute the physical memory bank. Their scheme gives conflict-free access to any slice of  $2^{d+q+n}$  consecutive vector elements with stride  $r2^k$ ,  $k \le q$ . So, this scheme restricts the size of accessible vectors. The evaluation of this scheme, using the stride distribution presented at the beginning of the chapter, showed that it boosts the throughput to 90% rather than 50% with LOI.

Figure 2-3: Memories with Buffers

Figure 2-4: Space-Time-Multiplexed Memory

# Chapter 3

# 3. Linear Bitwise Storage Schemes

### 3.1 Introduction

Since the knowledge of data patterns or patterns is within the capability of the compiler, storage schemes that offer higher flexibility have been proposed [13] as linear transformations from the processor address to the storage location. Frailong [13] presented a necessary and sufficient condition for conflict-free access of data patterns. The image by the storage scheme of all the elements of a given pattern should map into different memory modules. Therefore, the columns or the rows of the needed transformation matrix should be linearly independent.

Norton [31] synthesized a transformation matrix that allows conflict-free access to a number of power of 2 strides. The scheme was intended for the RP3 multiprocessor. As the interconnection network should provide data alignment between processors and memories, other constraints [5] can then be used for finding the storage matrix. By using bitwise linear transformation matrices, Boppana [6] proposed a conflict-free storage scheme to the row, column, main-diagonal, and square blocks. The above matrix is characterized by non-singular diagonal sub-matrices.

The data patterns that are accessed by a program can be mapped by a dynamic storage scheme that minimizes the overall memory conflicts for a set of given patterns. Dynamic storage schemes make the hardware transparent to the user and avoid reorganizing the data, but require the address transformation to be implemented as part of every processor hardware to increase concurrency. We are concerned with dynamically reconfigurable storage schemes for SIMD models that minimize the overall access time for an arbitrary set of weighted data patterns.

For array references, vectorizing loops in presence of loop-carried-dependency (LCD) may constrain the SIMD load and store operations to some specific data patterns such as the row (LCD across the columns), the column (LCD across the row), stride access, or arbitrary blocks. The problem is to find how arrays can be stored into parallel memories in order to force the elements of a given data pattern to be uniformly distributed

over the memories. Each uniformly distributed data pattern can then be accessed in one memory cycle so that each PE is mapped to one element of the pattern.

Given a program that requires access to a set of data patterns, our objective is to find a cost-effective storage scheme that minimizes overall memory access time. A general approach for combining the constraints of different data patterns into one single bit-wise address transformation is proposed. We will see that finding the address transformation that minimizes overall access time of a given set of data patterns is reduceable to m-coloring, where 2<sup>m</sup> is the number of memories. Since the transformation should be implemented by each PE of some SIMD system, it is interesting to optimize its hardware requirements. Optimizing the transformation is investigated by using coloring heuristics and the access frequency of each data pattern. In this case, the problem consists of minimizing the access time as well as the number of gates required to implement the transformation.

In section 3.2, we give a background on power of 2 patterns and their representation. In section 3.3, linear bitwise schemes are analyzed with some definitions and results known in literature. In section 3.4, we present our combined storage scheme. Access of arbitrary strides is discussed in section 3.5. The chapter is concluded by stating the NP-Completeness of the problem of constructing combined storage schemes in section 3.6.

### 3.2 Background

Consider an SIMD computer that consists of a number of processing elements and memory units connected by a network as shown in Figure 1-4. Any processor can access any memory unit through an interconnection network. We assume that there is an equal number N of processors and memory units, and that N is a power of two  $N = 2^m$ . If more than one processor tries to access a location in a given memory unit, during a given instruction cycle, a conflict occurs. If i processors all try to access a given memory unit during the same cycle, it takes i cycles for the memory unit to serve them. Since all processors run in lock-step, the entire computation is dramatically slowed. It would be desirable to store the data that should be simultaneously accessed into different memories so that parallel access to all items can be achieved.

Suppose that we know a priori the memory access patterns of a given program. We assume that the data to be accessed is a two dimensional array. Let the statement a(i,j) = F(a(i,j-1),...) be the body of a loop, where a(.,.) is a 2-D array and F is some function. Due to data dependency between a(i,j) and a(i,j-1) across the iterations, one way to vectorize the loop is to distribute the code so that the PEs evaluate elements along rows of the array. Thus the PEs need to perform simultaneous access to a column of data element from the array which allows defining a column data access pattern. Note that a column access may be translated within the array to allow different instances of column patterns be accessed in parallel.

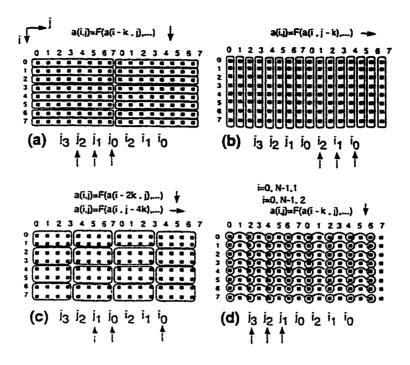

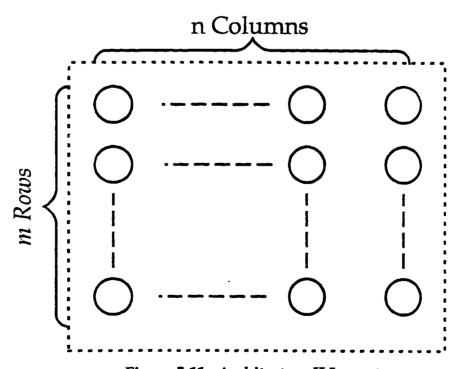

Figure 3-1: Patterns a) sub-row, b) sub-column, c) 2X4 blocks, and d) row/stride access

A pattern is defined as a collection of array elements whose addresses are related by some relationship. The *origin* of a pattern is the coordinate of its upper leftmost element. Changing the origin allows access to different instances of the pattern. Figure 3-1 shows an  $8 \times 16$  array that is partitioned into a set of 8-elements row-pattern, column-pattern,  $2 \times 4$  block-pattern, and a stride-2 row-pattern. A pattern that is needed for some SIMD program is a collection of array elements that any instance (its origin) of it can be accessed in parallel, by all the PEs, during the running of the program. We are interested in patterns of arbitrary dimension but having power-of-2 elements.

We would like to find a function that allows us to access all patterns in a conflict free manner. By this, we mean that for all given patterns, for all pattern instances, all of the elements of any pattern instance map to distinct memory units. For instance, in a matrix multiply algorithm, we would like to have conflict free access to all rows, and all columns. The set of all rows (columns) is a pattern, and each row (column) is a pattern instance. We want to allocate the array among the memory units in such a way that no two elements of the same row are in the same memory unit, and no two elements of the same column are in the same memory unit. Such an allocation is called a conflict-free storage scheme [13,31] for the row and the column.

Without loss of generality, the memory is considered as a single two dimensional array such that the element in the *i*th row and the *j*th column is denoted by (i, j). The upper left-most element is (0.0). To simplify the notation, the sizes of the horizontal and vertical dimensions are both  $2^d$ . By convention, the array is always indexed by a variable i in the vertical direction, and a variable j in the horizontal direction.

The binary representation of an integer i is  $i_{d-1}...i_1i_0$ . In other words, the least significant bit of i is  $i_0$ , the first bit is  $i_1$ , etc.

A row position i can also be thought of as a vector, over the finite field  $Z_2$ , the integers modulo 2. In  $Z_2$ , addition corresponds to logical exclusive or, and multiplication corresponds to logical and.  $(i_{d-1}...i_1i_0)$  is the vector representation of i, in terms of the

bits of i. We define a vector space  $F = \mathbb{Z}_2^d$  for horizontal position. Let  $B(F) = \{f_{d-1}, ..., f_0\}$  be the canonical basis of F, i.e.  $f_0 = (0, ..., 0, 1), f_1 = (0, ..., 1, 0), ..., f_{d-1} = (1, 0, ..., 0)$ . Each row has a unique representation as a vector in F. A row i is expressed as  $i_{d-1}f_{d-1}\oplus ...\oplus i_1f_1\oplus i_0f_0$  in terms of components over B(F). For example, 11 in binary is 1101, and so the vector representation of row 11 is (1,1,0,1). Expressed as a linear combination of the basis F, row 11 is  $1f_3 \oplus 0f_2 \oplus 1f_1 \oplus 1f_0$ :

$$1.\begin{pmatrix} f_1 \\ 1 \\ 0 \\ 0 \\ 0 \end{pmatrix} \oplus 0.\begin{pmatrix} f_1 \\ 0 \\ 1 \\ 0 \\ 0 \end{pmatrix} \oplus 1.\begin{pmatrix} f_1 \\ 0 \\ 0 \\ 1 \\ 0 \end{pmatrix} \oplus 1.\begin{pmatrix} f_2 \\ 0 \\ 0 \\ 0 \\ 1 \\ 0 \end{pmatrix}$$

Without loss of generality, we assume  $d \times d$  2-dimensional arrays to simplify the notation, but both sizes can be arbitrary as well. We similarly define vector spaces G for column positions and with canonical bases  $B(G) = \{g_{d-1}, ..., g_1, g_0\}$ . There are  $2^m$  memories and that the number of PEs is identical to the number of memories. Let H be  $\frac{1}{2}$  vector space for memory unit numbers and its basis  $B(H) = \{h_{m-1}, ..., h_1, h_0\}$ .

The Cartesian product of the vector spaces F and G is another vector space  $F \times G$  with basis  $B(F \times G) = \{f_{d-1}, ..., f_1, f_0, g_{d-1}, ..., g_1, g_0\}$ . Any location  $(i,j) \in F \times G$  in memory is uniquely associated with a linear combination  $i_{d-1}f_{d-1} \oplus ... \oplus i_0 f_0 \oplus j_{d-1}g_{d-1} \oplus ... \oplus j_0 g_0$  of the basis vectors of  $B(F \times G)$ . Adding two vectors in  $\mathbb{Z}_2^{2d}$  corresponds to bitwise **exclusive or**. Multiplying a vector by the scalar 1

gives back that vector, while multiplying a vector by the scalar 0 results in the zero vector.

Consider the parallel access to 8 memories for the set of elements  $\{(i,j)\}=(i_{d-1},...,i_0,j_{d-1},...,j_3,-,-,-)$ , where  $i_{d-1},...,i_0,j_{d-1},...,j_3$  are constant for all the 8 elements and components  $i_2,i_1,i_0$  take all possible combinations. The accessed pattern  $(T_1)$  consists of a sub-row of 8 successive elements of array A. Pattern  $T_1$  is associated a basis  $B(T_1)=\{g_2,g_1,g_0\}$ . We note that  $i_2,i_1,i_0$  are the components of (i,j) over the basis  $B(T_1)$ , i.e. projection of (i,j) over  $B(T_1)$ . The set of components  $i_{d-1},...,i_0,j_{d-1},...,j_3$  represent the pattern origin and used to define one instance of  $T_1$ . By changing the origin we can access different instances of  $T_1$ . For example, we can position the origin of  $T_1$  into  $2^{2d-3}$  different locations within array A.

To access a sub-column of 8 successive elements, we define pattern  $T_2$  that accesses the set  $\{(i,j)\} = (i_{d-1},...,i_3,-,-,-,j_{d-1},...,j_0)$  The basis of  $T_2$  is  $B(T_2) = \{f_2,f_1,f_0\}$ . Finally, we define a pattern  $T_3$  that consists of 2 successive rows by 4 successive columns for which the set of elements is  $\{(i,j)\} = (i_{d-1},...,i_1,-,j_{d-1},...,j_2,-,-)$ . The basis of  $T_3$  is  $B(T_3) = \{f_0,g_1,g_0\}$ .

To cause the parallel access to all the 8 elements of  $T_1$ , for a given instance of the origin, one can choose to store each element A(i,j) into memory  $(i_2,i_1,i_0)$ . In this case, all the elements of  $T_1$  will be distributed over all the memories and parallel access to  $T_1$

becomes possible. Therefore, accessing one single pattern does not pose any problem. We are interested in finding storage schemes that allow an array to be accessed in parallel with respect to an arbitrary set of data patterns.

## 3.3 Analysis of Storage Schemes

Each location  $(i, j) \in F \times G$  has 2d components over the basis  $B(F \times G)$ . Denote by V a subspace of  $F \times G$  whose basis B(V) is formed by m vectors out of the 2d canonical vectors of  $B(F \times G)$ , where  $n \le 2d$ . From now on we consider vector x (also y) as the projection of some (i, j) over V.

Consider the following two Boolean matrices:

$$M_1 = \begin{pmatrix} 1 & 0 & 1 \\ 0 & 1 & 1 \\ 0 & 0 & 1 \end{pmatrix} \qquad M_2 = \begin{pmatrix} 1 & 0 & 1 \\ 0 & 1 & 1 \\ 0 & 1 & 1 \end{pmatrix}$$

Matrix  $M_1$  represents a linear permutation defined over the set of integers (0,....7).  $M_1$  achieves the permutation  $(0,1,2,3,4,5,6,7) \rightarrow (0,7,2,5,4,3,6,1)$ . Each source has a unique image by  $M_1$ . However, the image by  $M_2$  of the ordered set of elements (0,1,2,3,4,5,6,7) is (0,7,3,4,4,3,7,0). We note that each image by  $M_2$  has two sources. We are interested in finding Boolean matrices M that causes an array to be distributed over the memories for a given set of data patterns. Each element A(i,j) of some array A will be stored into memory module Mx, where x is the projection of A(i,j) over the basis of

the corresponding pattern, and M will be called storage scheme. In the following we present a theorem that states the necessary and sufficient condition to cause the elements of an array to be distributed over the memories to allow parallel access to a given data pattern.

**Theorem 1** Two different vectors  $x, y \in V$  always have different images by an  $m \times m$  matrix M if and only if M is non-singular.

The proof of this theorem can be found in any book on linear algebra. As an example of theorem 1, matrix  $M_1$  allows one-to-one mapping of the source elements (0,...,7) to the image (0,7,2,5,4,3,6,1) which causes the source elements to be distributed over the memories if each array element A(i,j) is stored into memory  $M_1x$  and  $M_1$  is non-singular, where x is the projection of (i,j) over some three canonical vectors of  $B(F \times G)$ . Note that  $M_2$  does not allow the same result because  $M_2$  is singular. For example, in row-major memory organization element  $(i,j) = (i_{d-1},...,i_0,j_{d-1},...,j_0)$  is stored into memory module Mx, where  $x = (j_2,j_1,j_0)$  and M is the  $3 \times 3$  identity matrix.

**Theorem 2** A pattern T that is defined by its basis  $B(T) = \{t_{m-1}, ..., t_0\} \subset B(F \times G)$  can be accessed in parallel using  $2^m$  memories if each element  $x = x_{m-1}t_{n-1} \oplus ... \oplus x_0t_0$  of T is stored into memory module Mx and matrix M is non-singular.

**Proof** As M is non-singular, then elements  $x, y \in T$  such that  $x \neq y$  satisfy  $Mx \neq My$  as shown in Theorem 1. Therefore, the elements of T will be distributed over the memories whenever each element  $x \in T$  is stored into memory Mx and M is non-singular.

## 3.4 Combined Storage Schemes

Consider a set  $\Gamma = \{T_1, ..., T_q\}$  of data patterns so that each pattern consists of  $2^m$  elements. The basis of each pattern  $T_k$  is denoted by  $B(T_k) = \{t_{k,m-1}, ..., t_{k,0}\}$ , where  $t_{k,m-1}, ..., t_{k,0}$  are some canonical vectors chosen from  $B(F \times G)$ . Since each pattern instance has  $2^m$  elements, our objective is to define a storage scheme for the array A(i,j) so that any pattern instance can be accessed in one memory cycle. In other words,  $2^m$  elements of any pattern instance should be distributed over the  $2^m$  memories in order to allow parallel access to that pattern.

Definition 1 The basis B of a set  $T_1,...,T_q$  of data patterns is the set of all distinct canonical vectors of the bases of all patterns  $T_1,...,T_q$ :  $B = \bigcup_{1 \le k \le q} B(T_k) = \{t_{m-1},...,t_0\}$ . where  $t_k$  is a canonical vector of B and n = Card(B)

The bases of two data patterns may or may not share a number of canonical vectors. Therefore, the number of distinct vectors n in the union of all pattern bases

should always satisfies  $m \le n \le 2d$ . Consider the previously defined set of patterns  $\{T_1, T_2, T_3\}$  with bases  $B(T_1) = \{f_2, f_1, f_0\}$ ,  $B(T_2) = \{g_2, g_1, g_0\}$ , and  $B(T_3) = \{f_0, g_1, g_0\}$ . which allows finding  $B = \bigcup_{1 \le k \le 3} B(T_k) = \{f_2, f_1, f_0, g_2, g_1, g_0\}$ .

**Definition 2** The projection of vector  $(i,j) \in F \times G$  over the basis  $B(T_k)$  is defined by vector  $x^{b(T_k)} = x_{n-1}t_{k,n-1} \oplus ... \oplus x_0t_{k,0}$  that is formed by the components of (i,j) over the basis  $B(T_k)$ .

It is important to note that each data pattern has power of 2 elements and all instances of a given data pattern are non-overlapping. Therefore, the projection of vector (i,j) over  $B(T_k)$  gives the location of element (i,j) within pattern  $T_k$  and the other components of (i,j) remain constant when accessing  $T_k$  in parallel. The constant components specify the origin of the pattern instance. For parallel access of sub-columns of  $2^3$  elements for some array  $A(10 \times 12)$ , the element address will be  $(i,j) = (i_2,...,i_0,j_{11},...,j_0)$  and its projection over the pattern (sub-row) basis is  $\{i_2,i_1,i_0\}$ . When accessing a sub-column in parallel, the components over  $(g_2,g_1,g_0)$  of all addresses located in a sub-column instance take all possible combination of bits in  $\{i_2,i_1,i_0\}$ . Moreover, the projection of all elements of some pattern  $T_k$  that is accessed in parallel take all possible combinations over the canonical vectors of  $B(T_k)$ .

We similarly define the projection of vector x over the basis B of all the data patterns.

**Definition 3** The projection of vector  $(i,j) \in F \times G$  over the basis B is the vector  $x^b = x_{n-1}t_{n-1} \oplus ... \oplus x_0t_0$  that is formed by the components of (i,j) over the canonical vectors of B.

Each vector (i,j) admits a projection  $x^b$  over the basis B of all data patterns. For example, vector  $(i,j) = f_{d-1}i_{d-1} \oplus ... \oplus f_0i_0 \oplus g_{d-1}j_{d-1} \oplus ... \oplus g_0j_0$  has a projection  $x^b = f_3i_3 \oplus f_2i_2 \oplus f_0i_0 \oplus g_3j_3 \oplus g_2j_2 \oplus g_0j_0$  over the basis  $B = \bigcup_{1 \le k \le 3} B(T_k)$ . In the following we define the combined storage matrix M that is used to evaluate the memory module number where the (i,j)th element of some array should be stored.

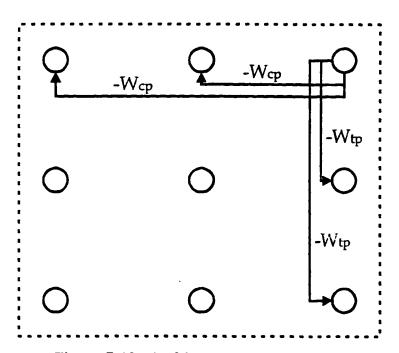

**Definition 4** The combined storage associated to all data patterns  $\{T_k:0 \le k \le q\}$  is a matrix M of dimension  $m \times n$  such that each vector (i,j) is stored into memory location  $Mx^b$ , where  $2^m$  is the number of memory modules and n is the number of distinct vectors in the union of all pattern bases.

The combined storage matrix M can be seen as a collection of columns vectors, i.e.  $M = [C_{n-1}, ..., C_0]$ , where  $C_u$  is an  $m \times 1$  column vector. There is one-to-one correspondence between each canonical vector  $t_u \in B$  and column  $C_u$  of M. The column vector  $C_u$  is the image by M of  $t_u$  for  $0 \le u \le m$ . As  $B(T_k) \subset B$ , then each

column vector  $C_u$  of M is the image by M of some canonical vector  $t_{k,u} \in B(T_k)$ . For example, the combined storage matrix M for the data patterns  $T_1, T_2$ , and  $T_3$  is a  $3 \times 6$  matrix because  $B = \{f_2, f_1, f_0, g_2, g_1, g_0\}$ . If one choose arbitrary data for the matrix M, we obtain:

$$Mx^{b} = \begin{pmatrix} 1 & 0 & 1 & 1 & 1 & 1 \\ 0 & 1 & 0 & 0 & 1 & 0 \\ 0 & 0 & 1 & 1 & 0 & 0 \end{pmatrix} \cdot \begin{pmatrix} i_{2} \\ i_{1} \\ i_{0} \\ j_{2} \\ j_{1} \\ j_{0} \end{pmatrix}$$

**Definition 5** The restricted matrix  $M_{T_k}$  of M to pattern  $T_k$  is defined by the m columns of M that are the images by M of all canonical vectors of basis  $B(T_k)$ .

The storage matrix M is  $m \times n$  and there are m columns in  $M_{T_k}$ , then  $M_{T_k}$  is an  $m \times m$  matrix. For example, the restricted matrices  $M_{T_1}$ ,  $M_{T_2}$ , and  $M_{T_3}$  are the following:

$$M_{\tau_1} = \begin{pmatrix} 1 & 0 & 1 \\ 0 & 1 & 0 \\ 0 & 0 & 1 \end{pmatrix} \qquad M_{\tau_2} = \begin{pmatrix} 1 & 1 & 1 \\ 0 & 1 & 0 \\ 1 & 0 & 0 \end{pmatrix} \qquad M_{\tau_3} = \begin{pmatrix} 1 & 1 & 1 \\ 0 & 1 & 0 \\ 1 & 0 & 0 \end{pmatrix}$$

In the following we summarize our analysis. For some array A, we consider a set  $T = \{T_1, ..., T_q\}$  of data patterns that will be accessed by some program at run-time. Each pattern has  $2^m$  elements and there are  $2^m$  parallel memories. We are interested in finding a storage scheme so that each of these pattern can be accessed in one memory cycle. This

requires that the elements of each pattern be distributed over the memories so that parallel access can occur to all the memories. Each power of 2 pattern  $T_k$  can be uniquely associated a basis  $B(T_k)$ . While each pattern basis has m canonical vectors, the set B of all distinct canonical vectors of all bases has  $n \ge m$  canonical vectors because some of these vectors cannot be shared among patterns. To define the storage scheme, the address (i,j) of array element A(i,j) is restricted to its components over B and this restricted vector is denoted by  $x^b$ . A storage matrix M  $(m \times n)$  is used to find the memory module  $Mx^b$  where element A(i,j) of array A should be stored.