# AUTOVLSI: A Layout System for General-Cell VLSI Design

by

Hazem Muhebbadin Ahmad Naji Abu-Saleh

A Thesis Presented to the

### FACULTY OF THE COLLEGE OF GRADUATE STUDIES

### KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

### DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

### MASTER OF SCIENCE

In

### **COMPUTER ENGINEERING**

February, 1995

### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 313/761-4700 800/521-0600

AUTOVLSI SYSTEM: A LAYOUT SYSTEM FOR GENERAL-CELL VLSI DESIGN BY Hazem Muhebbadin Ahmad Naji Abu-Saleh A Thesis Presented to the FACULY OF THE COLLEGE OF GRADUATE STUDIES (MG FAHD UNIVERSITY OF PETOLEUM & MINERALS DHAHRAN, SAUDI ARABIA In Partici Fulfillment of the Requirements for the Degree of In COMPUTER ENGINEERING FEBRUARY 1995

**UMI Number: 1375120**

UMI Microform 1375120 Copyright 1995, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

# UMI

300 North Zeeb Road Ann Arbor, MI 48103

# AUTOVLSI SYSTEM: A LAYOUT SYSTEM FOR GENERAL-CELL VLSI DESIGN

By Hazem Muhebbaddin Ahmad Naji Abu-Saleh

February 1995

# KING FAHD UNIVERSITY OF PETROLEUM AND MINERALS DHAHRAN 31261, SAUDI ARABIA COLLEGE OF GRADUATE STUDIES

This thesis, written by

### Hazem Muhebbaddin Ahmad Naji Abu-Saleh

under the direction of his thesis advisor and approved by his Thesis Committee, has been presented to and accepted by the Dean of the College of Graduate Studies, in partial fulfillment of the requirements for the degree of

### MASTER OF SCIENCE IN COMPUTER ENGINEERING

**Thesis Committee:** Icdiq Sait · M. Dr. Sadiq M. Sait (Chairman)

Dr. Mg tmad S.T. Benten (Member)

Dedicated to

# My Parents Wife, and Brother

whose support and prayers led to this achievement.

### Acknowledgments

All praise be to Allah for his limitless help and guidance. Peace and blessings of Allah be upon his prophet Muhammad.

Acknowledgment is due to King Fahd University of Petroleum and Minerals, Dhahran, Saudi Arabia, for the generous help and support for this research.

I would like to express my profound and appreciation to my advisor, Dr. Sadiq M. Sait, Associate Professor of Computer Engineering, for his guidance and patience throughout this thesis.

I would also like to thank co-chairman, Dr. Habib Youssef Associate Professor of Computer Engineering, whose continuous encouragement can never be forgotten, and Dr. Mohammad S.T. Benten Associate Professor of Computer Engineering for his consistent support and valuable suggestions.

Thanks also to the faculty of the Computer Engineering Department; Department Chairman, Dr. Sameer Abdul-Jauwad for their consistent encouragement and support.

Help in printing, encouragement and good wishes of the following friends is also worthy of acknowledgment. They are: Ammar Al-Akel, Ayman Altounji, Samer Al-Sayed, and Rashad Bahsaly.

Finally, special thanks must be given to my family for their encouragement and moral support.

# Contents

|   | List              | ist of Figures                        |            |  |  |

|---|-------------------|---------------------------------------|------------|--|--|

|   | Abs               | Abstract (English) ix                 |            |  |  |

|   | Abstract (Arabic) |                                       |            |  |  |

| 1 | Intr              | troduction 1                          |            |  |  |

|   | 1.1               | Logic Design                          | 4          |  |  |

|   | 1.2               | Hardware Programming Languages (HPLs) | 6          |  |  |

|   | 1.3               | VLSI Technology                       | 7          |  |  |

|   |                   | 1.3.1 Layout Styles                   | 9          |  |  |

|   |                   | 1.3.2 Generating VLSI Layouts         | 10         |  |  |

|   |                   | 1.3.3 VLSI Layout Programs            | 13         |  |  |

|   | 1.4               | Auto VLSI                             | 14         |  |  |

|   | 1.5               | Description of Contents               | 15         |  |  |

| 2 | Log               | ic Assignment                         | 18         |  |  |

|   | 2.1               | Logic Assignment for UAHPL Gates      | 19         |  |  |

|   |                   | 2.1.1 Auto VLSI Library of VLSI Cells | <b>2</b> 1 |  |  |

|   | 2.2 | A uto V       | <i>'LSI</i> General-cell Library                     | 2 |

|---|-----|---------------|------------------------------------------------------|---|

|   |     | 2.2.1         | Rules of Designing a VLSI Cell for AutoVLSI System   | 2 |

| 3 | Pla | cement        | t                                                    | 3 |

|   | 3.1 | Introd        | uction                                               | ç |

|   |     | <b>3.1.</b> 1 | Definition                                           | ŝ |

|   |     | 3.1.2         | Cost Function                                        | ç |

|   |     | 3.1.3         | Complexity of the Placement Problem                  | 4 |

|   | 3.2 | Techni        | ques of Placement                                    | 4 |

|   |     | 3.2.1         | Constructive Placement Algorithms                    | 4 |

|   |     | 3.2.2         | Iterative Improvement Algorithms                     | 4 |

|   | 3.3 | Placen        | nent in AutoVLSI                                     | 4 |

|   |     | 3.3.1         | Phase I: Linear Ordering of Cells                    | 4 |

|   |     | 3.3.2         | Phase II: Folding Cells in Two-dimensional Plane     | Ę |

| 4 | Glo | bal Ro        | uting                                                | 6 |

|   | 4.1 | Introd        | uction                                               | ( |

|   |     | 4.1.1         | Definitions and New Terms                            | ŧ |

|   |     | 4.1.2         | Tasks of the Global Routing Stage                    | e |

|   | 4.2 | Task I        | Channel Identification                               | ŧ |

|   |     | 4.2.1         | Procedure for Channel Identification                 | e |

|   |     | 4.2.2         | Merging Channels                                     | 7 |

|   | 4.3 | Task I        | I: Constructing CCG and Determining Wires Paths      | ٤ |

|   |     | 4.3.1         | Construction of the Channel Connectivity Graph (CCG) | ٤ |

|   |     | 4.3.2         | Determination of Wires Paths                         | ſ |

•

.

ii

|   | 4.4 | Task I  | III: Routing Regions Adjustment                          | 104 |

|---|-----|---------|----------------------------------------------------------|-----|

|   |     | 4.4.1   | CHCs Adjustment                                          | 105 |

|   |     | 4.4.2   | CVCs Adjustment                                          | 107 |

| 5 | Det | ailed H | Routing                                                  | 112 |

|   | 5.1 | Maze    | Routing                                                  | 112 |

|   |     | 5.1.1   | Phases of Lee Algorithm                                  | 113 |

|   |     | 5.1.2   | Routing Layers                                           | 117 |

|   |     | 5.1.3   | Not Found Paths                                          | 117 |

|   | 5.2 | Extrac  | cting Nets in AutoVLSI                                   | 120 |

|   |     | 5.2.1   | Mapping Between Design Interconnections and Ports on VLS | I   |

|   |     |         | cells                                                    | 121 |

|   |     | 5.2.2   | Finding Shortest Paths                                   |     |

|   | 5.3 | Detail  | ed Routing in AutoVLSI                                   |     |

|   |     | 5.3.1   | Running the Router Software                              |     |

|   |     | 5.3.2   | Non-Routed Segments                                      |     |

|   | 5.4 | Buildi  | ng the Layout                                            |     |

|   |     | 5.4.1   | Creating MAGIC Cells File                                |     |

|   |     | 5.4.2   | Creating MAGIC Routes File                               |     |

|   |     |         | Combining the Cells and the Routes Files                 |     |

|   | 5.5 |         | ctness & Simulation of the Layout                        |     |

|   |     |         |                                                          | 101 |

| 6 | Con | clusio  | n & Future Work                                          | 132 |

|   | 6.1 | Layou   | t Compaction                                             | 133 |

|   | 6.2 | Future  | e Work                                                   | 134 |

| A | Summary of AutoVLSI System Components. 1 |       |  |

|---|------------------------------------------|-------|--|

|   | A.1 Main Software Modules                | . 137 |  |

|   | A.2 Utility Software Modules             | . 142 |  |

| B | Flow-chart of AutoVLSI System.           | 145   |  |

|   | Bibliography                             | 146   |  |

|   | Vita                                     | 149   |  |

iv

•

.

# List of Figures

| 1.1  | Diagram of UAHPL system                                                 | 7  |

|------|-------------------------------------------------------------------------|----|

| 1.2  | Stages of AutoVLSI system including their tasks                         | 16 |

| 2.1  | Logic assignment for a 10-input AND gate                                | 20 |

| 2.2  | VLSI circuits of the cells in AutoVLSI library                          | 23 |

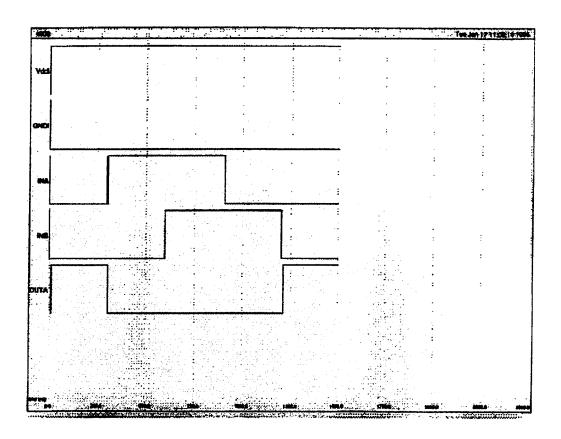

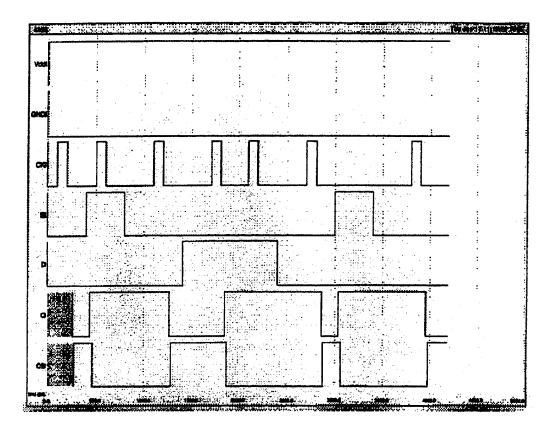

| 2.3  | RSIM simulation output for cell 4102.MAG (i.e., INVERTER gate)          | 24 |

| 2.4  | RSIM simulation output for cell 4205.MAG (i.e., 2-input NOR gate).      | 25 |

| 2.5  | RSIM simulation output for cell 4336.MAG (i.e., D Flip-Flop with        |    |

|      | SET control)                                                            | 26 |

| 2.6  | Table of predefined gates' type numbers.                                | 27 |

| 2.7  | List of GATES.LIB file.                                                 | 27 |

| 2.8  | Illustration of the rules of designing a VLSI cell for AutoVLSI system. | 30 |

| 2.9  | Files names of VLSI cells in <i>AutoVLSI</i> system library             | 31 |

| 2.10 | List of AGHW.DAT file.                                                  | 32 |

| 2.11 | Records of 2-input NOR cell and D Flip-Flop with ENABLE control         |    |

|      | cell in POC.DAT file                                                    | 36 |

| 3.1  | An example of a standard cell style layout                              | 38 |

| 3.2  | Algorithm for estimating layout area                                    | 40 |

|      |                                                                         |    |

| 3.3  | An example to illustrate $m$ and $m$ ' in the algorithm for estimating      |    |

|------|-----------------------------------------------------------------------------|----|

|      | layout area                                                                 | 41 |

| 3.4  | Different techniques of estimating the wire length                          | 42 |

| 3.5  | Illustration of a grid cell and VLSI design rules                           | 47 |

| 3.6  | Actual size of a cell.                                                      | 48 |

| 3.7  | Illustration of <i>terminated</i> , <i>continuing</i> , and <i>new</i> nets | 49 |

| 3.8  | Linear Ordering algorithm                                                   | 51 |

| 3.9  | Execution table of Example 3.1 [2]                                          | 53 |

| 3.10 | A graphical representation of the ordered cells of Example 3.1              | 54 |

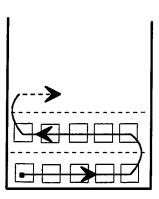

| 3.11 | Different techniques of folding a sequence of cells                         | 55 |

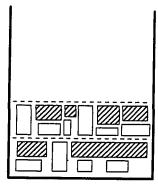

| 3.12 | Row-folding example for standard-cell layout.                               | 56 |

| 3.13 | Row-folding example for general-cell layout.                                | 56 |

| 3.14 | Algorithm for the modified version of Row-folding technique                 | 58 |

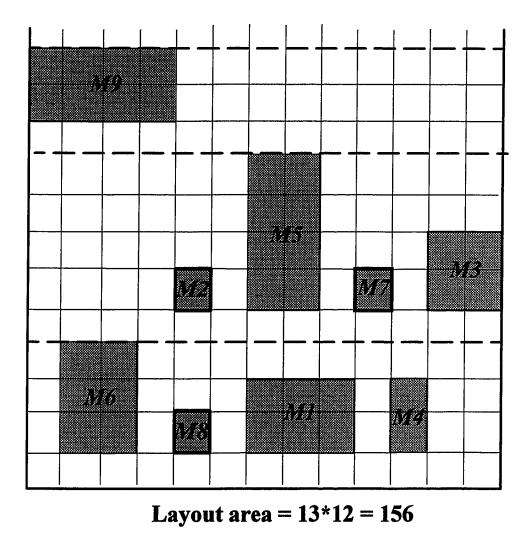

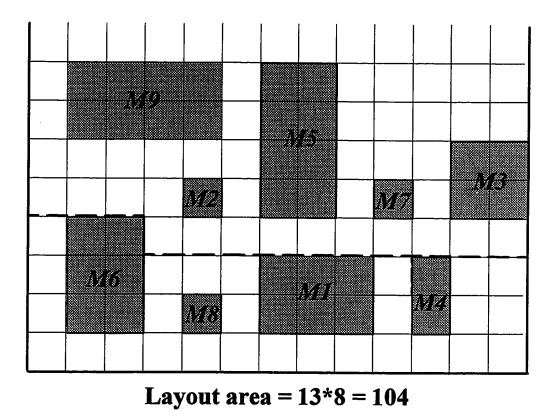

| 3.15 | The layout of Example 3.2 generated by Row-folding algorithm                | 60 |

| 3.16 | The layout of Example 3.2 generated by the modified version of Row-         |    |

|      | folding algorithm                                                           | 62 |

| 4.1  | Illustration of the ports of a VLSI cell. The cell represents a 2-input     |    |

|      | <i>NOR</i> gate                                                             | 65 |

| 4.2  | Illustration of Horizontal and Vertical channels.                           | 66 |

| 4.3  | Algorithm for identifying channels.                                         | 71 |

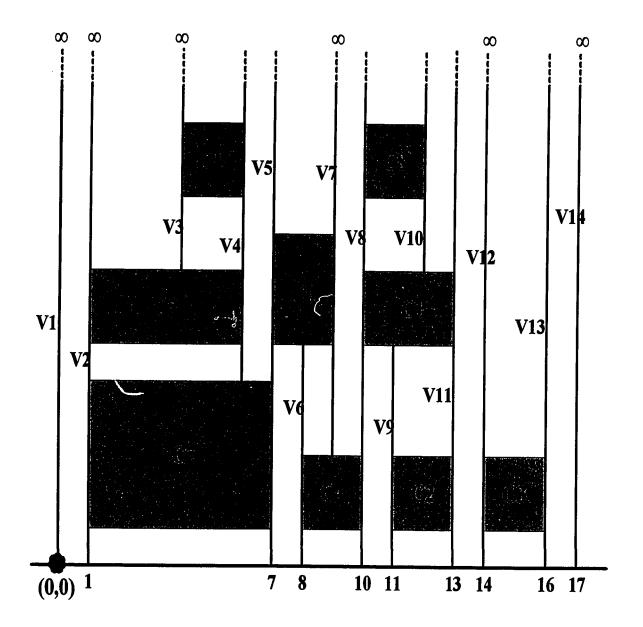

| 4.4  | Vertical lines lists for Example 4.1                                        | 74 |

| 4.5  | Illustration of vertical lines for the layout of Example 4.1                | 75 |

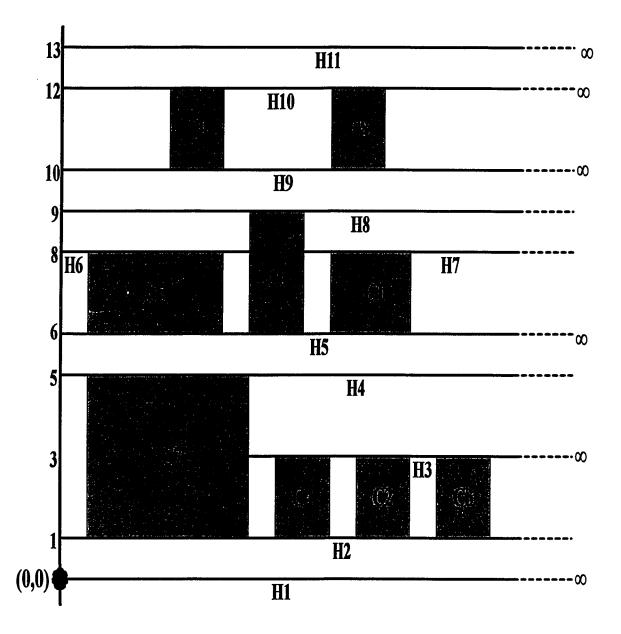

| 4.6  | Horizontal lines list for Example 4.1                                       | 76 |

| 4.7  | Illustration of horizontal lines of the layout of Example 4.1               | 77 |

.

.

•

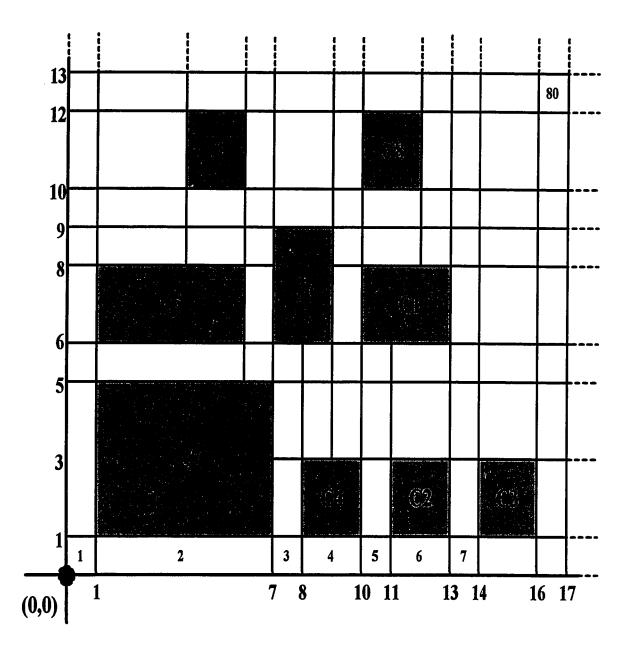

| 4.8                  | Complete list of channels identified from the layout in Example 4.1       | 80 |

|----------------------|---------------------------------------------------------------------------|----|

| 4.9                  | Graph of the layout in Example 4.1 showing final set of channels          | 81 |

| 4.10                 | Channels list of the layout in Exampl 4.1 showing final set of channels.  | 82 |

| 4.11                 | Merging-Channels algorithm                                                | 83 |

| 4.12                 | Execution table for Example 4.2                                           | 86 |

| <b>4</b> .1 <b>3</b> | List of channels for the layout in Example 4.2.                           | 87 |

| 4.14                 | Layout of Example 4.2 showing the resulting unified channels              | 38 |

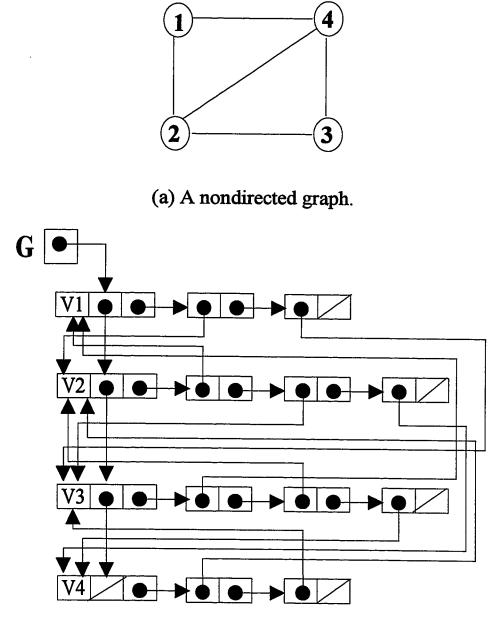

| 4.15                 | Example to clarify Adjacency Structure                                    | 91 |

| 4.16                 | Creating-CCG algorithm                                                    | €2 |

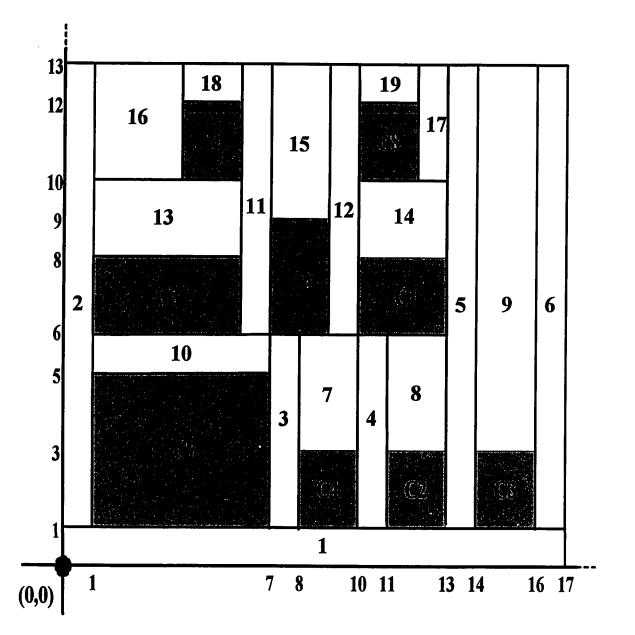

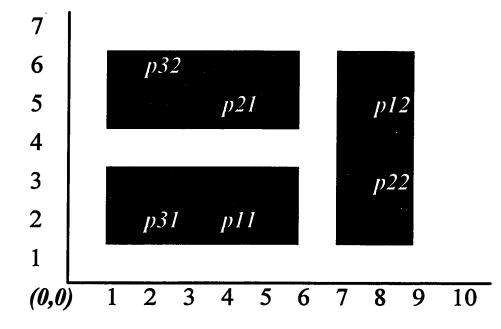

| 4.17                 | Illustration for Example 4.3                                              | 94 |

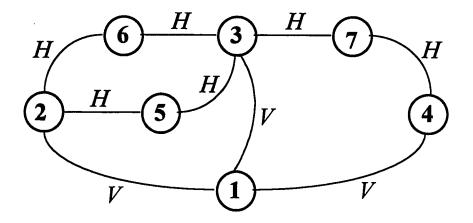

| 4.18                 | Final Adjacency Structure and CCG for Example 4.3                         | 96 |

| 4.19                 | The algorithm of Predicting-Wires-Path procedure.                         | 99 |

| 4.20                 | The layout of Example 4.4                                                 | 00 |

| 4.21                 | Graphical representation of the channels of the layout in Example 4.4 .10 | )1 |

| 4.22                 | Channel list for the layout in Example 4.4                                | 01 |

| 4.23                 | Channel Connectivity Graph for the layout in Example 4.4 10               | )2 |

| 4.24                 | List of channels in Example 4.4 after applying Predicting-Wires-Paths     |    |

|                      | algorithm                                                                 | )4 |

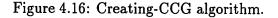

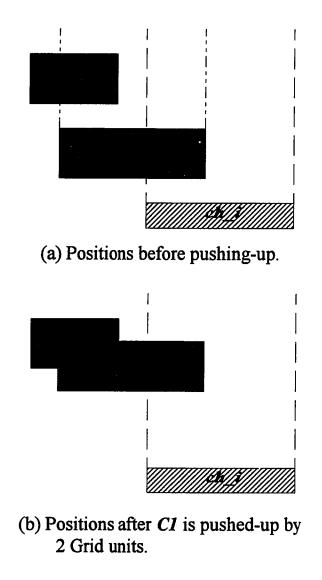

| 4.25                 | An example to illustrate the pushing operation                            | )6 |

| 4.26                 | Adjust-Layout algorithm. Continued in Figure 4.27                         | )8 |

| 4.27                 | Continuation of Figure 4.26                                               | )9 |

| 4.28                 | The new coordinates for cells in Example 4.5 after applying Adjust        |    |

|                      | Layout algorithm                                                          | 1  |

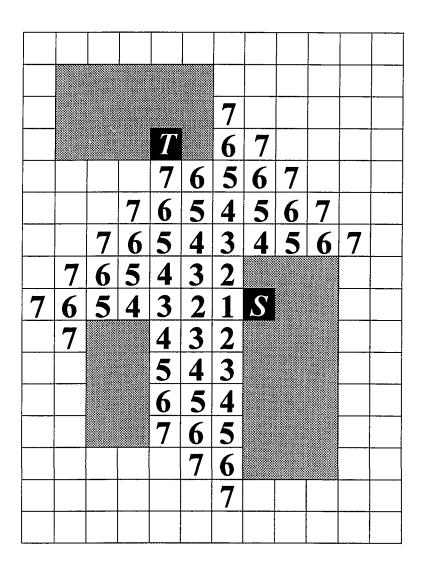

| 5.1                  | Small layout example to illustrate the filling phase in Lee algorithm 11  | 15 |

| 5.2 | Retrace phase for the example in Figure 5.1                         |

|-----|---------------------------------------------------------------------|

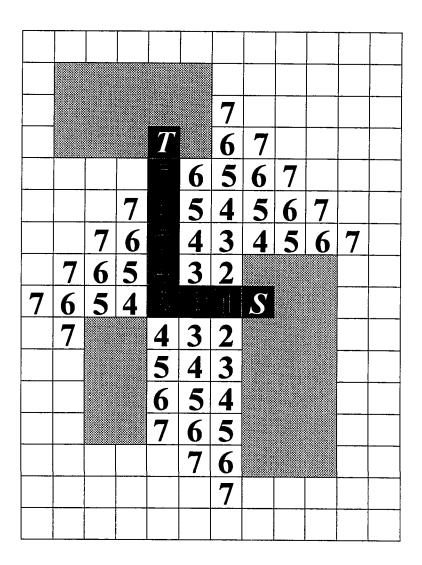

| 5.3 | Illustration of the two layers used for routing                     |

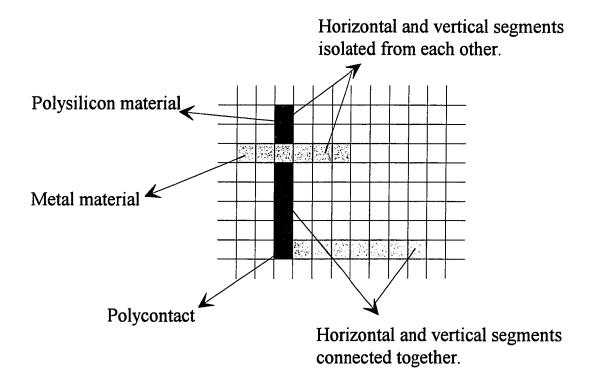

| 5.4 | Path blocking example solved by switching the order of nets when    |

|     | routed                                                              |

| 5.5 | Path blocking example as a result of inadequate space               |

| 5.6 | The algorithm for GMSTADJ batch program                             |

| 5.7 | The Flow-Chart of the Detailed Routing stage in AutoVLSI system 128 |

| 6.1 | Statisical data as a result of running AutoVLSI system on four dif- |

|     | ferent examples                                                     |

•

### **Thesis Abstract**

Name: Hazem Muhebbaddin Ahmad Naji Abu-Saleh.

Thesis Title: AutoVLSI SYSTEM: A Layout System for General-Cell

VLSI Designs.

Major Field: Computer Engineering.

Date of Degree: February 1995.

Designing complex digital systems from hardware description languages (HDL) models has been in vogue in the last decade.

The task of translating an HDL description to silicon can be divided into two stages. The first stage consists of the translation of the language model to an intermediate logic level description (hardware compilation), and the second stage is the translation of logic level description to VLSI layouts (physical design).

Physical design consists of tasks such as logic assignment, placement of layout cells, global routing, and detailed routing, etc. In this work, we address the physical design stage. Efficient algorithms were selected, modified where needed, and implemented for the different tasks of the physical design stage.

The proposed work will enable a complete automation of VLSI layouts from hardware description models.

Master of Science Degree King Fahd University of Petroleum and Minerals Dhahran, Saudi Arabia February 1995 خلاصة الرسالة

الإســـــم: حازم محب الدين أحمد ناجي أبوصالح. عنوان الرسالة: نظام AutoVLSI : نظام تصميم المخططات التفصيلية -ذات العدد المرتفع جدا من الدوائر المتكاملة- باستخدام خلايا عامة. الــتخــصص: هـندســة الحــاســب الآلــي. تاريخ الشههادة: فـبر ايـر ١٩٩٥.

إن تصميم أنظمة رقمية معقدة باستخدام لغات وصفية لتصميم الحاسب الآلي أصبح موضوعاً دارجا منذ عشر سنوات مضبت.

مهمة تحويل نظام رقمي موصوف بإحدى هذه اللغات إلى مخطط تفصيلي -ذي عدد مرتفع جدا من الدوائر المتكاملة- على شريحة سليكونية تتقسم إلى مرحلتين؛ في المرحلة الأولى: يتم تحويل الوصف إلى وصف منطقي متوسط يعرف باسم القائمة الشبكية. و المرحلة الثانية: هي تحويل هذه القائمة الشبكية إلى مخطط تفصيلي -ذي عدد مرتفع جدا من الدوائر المتكاملة- و تعرف هذه المرحلة بالتصميم الفعلي.

مرحلة التصميم الفعلي تتكون من عدة مهام منها تحديد الخلايا، و وضع الخلايا على المخطط التفصيلي، و تحديد قنوات التوصيل بين هذه الخلايا (التوصيل العالمي)، و التوصيل الفعلي فيما بين الخلايا الموضوعة (التوصيل المفصل). نقوم في هذا العمل بدراسة الحلول الأوتوماتيكية لمرحلة التصميم الفعلي. و قد تم إختيار مخططات البرامج الفعالة، و تعديلها عند الحاجة، و أخيرا برمجتها لتنفيذ مهام مرحلة التصميم الفعلي.

إن العمل المقدم سوف يمكن توليد المخططات التفصيلية –ذات العـدد المرتفـع جـدا مـن الدوائـر المتكاملة– أوتوماتيكيا بدءا من الوصف المنطقي بأسلوب القائمة الشبكية لنظام رقمي.

> درجة الماجستير في العلوم جامعة الملك فهد للبترول و المعادن الظهران ، المملكة العربية السعودية فـبراير ١٩٩٥

# Chapter 1

# Introduction

With its high speed, high reliability and compact implementation, digital technology has infiltrated every field of modern electronics, and used in assembling computers, Hi-Fi systems, camcorders, audio-visual devices, security systems, washing machines, microwave ovens, and even video toys.

The design of modern digital systems requires contributions from several engineering specialists. First, a system designer, or system architect, determines the described characteristics for the final system and prepares a detailed specification that should define all inputs, outputs, environmental conditions, operation speeds, etc. A logic design engineer translates the system specification into a logic design that can meet the functional requirements. The task of the *circuit engineer* is to design circuits that provide the required logic functions. He has the option of designing the complete circuit using available off-the-shelf digital components (integrated circuits), or designing some parts of the circuit using VLSI (very large scale integration) technology and implementing his own IC (integrated circuit) [22].

Digital circuits have attracted international attention. Different nations using

different languages had to deal with them, so instead of using a bulky schematic description of a digital circuit, hardware description languages (HDL's) were invented to ease understanding of digital circuits specifications by different language speakers. HDL's were used in different fields of digital research and teaching.

Before 1970, digital circuits were analyzed and designed almost exclusively by hand. However, designing a digital system by hand is not easy. It requires three different engineers. Each of them has to make a lot of decisions and spend enough time that is practical in terms of days or months –depending on the complexity of the system- to accomplish his task.

As digital circuits increased in complexity and variety of use, there was a need for inventing fast ways of developing these circuits. This was the motive for finding what is known as a hardware programming language (AHPL), which is an integrated environment of an HDL and a hardware compiler that translates the description of the circuit into a logic design that meets the functional requirements. This compiler was to replace the task of the *logic design engineer*, because the compiler works much faster, more accurate, and produces more optimized designs. Designing complex digital systems using hardware programming languages has been in vogue in the last decade.

The task of translating HDL descriptions to silicon can be divided into two stages. The *first stage* consists of the translation of the language model to an intermediate logic level description (*hardware compilation*), and the *second stage* is the translation of logic level description to VLSI layouts (*physical design*).

The project implemented in this thesis (called *AutoVLSI*) addresses the physical design stage. Universal AHPL (UAHPL), an extension of A Hardware Programming

Language (AHPL), with its built-in hardware compiler is used for generating the logic level description of the digital circuit. AutoVLSI receives the logic description of a circuit generated by UAHPL and generates a VLSI layout for this description. The logic level description is characterized by two lists. The first shows what digital gates are used in the design, and the second gives details about the interconnection between inputs and outputs of these gates. This is called a netlist description of the circuit.

AutoVLSI system is not restricted to UAHPL as the generator of the circuit netlist description. It accepts any netlist description whose gates are all available in the system library of VLSI cells. However, AutoVLSI supports logic assignment for the types of gates used by UAHPL and does not have VLSI cells representing them in the system library. Suppose, for example, that UAHPL uses in its generated netlist an 8-input AND gate which is not available in the system library, then AutoVLSI assigns four 2-input AND gates and one 4-input AND gate -assuming of course that both types of gates exist in the system library- to replace the 8-input AND gate used by UAHPL.

Physical design problem can be broadly divided into two stages. *Placement stage* which gives the exact place of each VLSI cell on the layout plane, and *detailed routing* stage which wires the interconnection of these placed cells. Achieving complete routing for all nets is a must. One net which is not completely routed results in a malfunction in the circuit. Usually an intermediate stage called *global routing* is inserted in between the above two stages to predict the paths of wires and facilitate the *detailed routing stage*. Each stage of the physical design process consists of many tasks and will be described later in this chapter.

The detailed routing stage, was studied earlier at King Fahd University of Petroleum and Minerals (KFUPM) in 1987. A maze router that follows Lee algorithm was implemented in FORTRAN [23].

In this thesis work, we address the other two stages of physical design, namely placement and global routing plus integrating the whole work of logic assignment, placement, global routing and detailed routing into a complete digital automation system that automatically produces VLSI design layouts for digital circuits described in UAHPL. The proposed system will also produce additional data for simulation and verification of the generated layouts.

Many heuristics and algorithms related to these above mentioned topics have been carefully studied, analyzed, and examined. Finally, a subset of them were adopted, modified as needed, and implemented to generate AutoVLSI system. All programs except those for the *detailed routing stage*, were implemented in the Turbo C programming language from Borland company using an 80486-microprocessor IBM personal computer. Many other supporting utility programs were also implemented. Some of them find an estimate for the chip area and compute space utilization. Others, plot a symbolic graph of the layout showing the relative placement and the paths of routes. A brief description of every software used in *AutoVLSI* system is given in Appendix A. Moreover, the system flow-chart is illustrated in Appendix B.

### 1.1 Logic Design

A *digital system* is any system for transmission or processing information that is represented by physical quantities (signals) that can take only one of the two discrete values: 0 or 1.

A logic designer translates the system specification into a logic design that can meet functional requirements. The task of the *circuit engineer* is to design circuits that provide the required logic functions. Digital circuits differ in terms of difficulty. They might consist of a few gates, or they can have Arithmetic/Logic units, multiplexers, buffers, and even microprocessors. The first choice when implementing a digital circuit is to use some ready-made integrated circuits (ICs). A definition of an IC is quoted from [22]:

A circuit consisting of active and passive elements fabricated on a single semiconductor chip and mounted in an individual package.

Digital circuits can be implemented using only SSI (small scale integration) ICs if they are very simple, MSI (medium scale integration) and LSI (large scale integration) ICs or a combination of them, if they are more complicated. Once the designer decides upon what ICs the circuit needs, he lays them out on a PCB (printed circuit board) and makes the external interconnections between different pins of each IC to complete the design.

Regardless of the kind of ICs by which the circuit is implemented, there could be some ICs that are not 100% utilized while taking space on the PCB. Moreover, the external interconnections decrease the reliability of the circuit and might introduce some timing problems. And, finally, every digital circuit of adequate size will have components such as arithmetic/logic units, shift registers, multiplexers, buffers, and so on. Some of these components might not be available as off-the-shelf components. Therefore, for one or more of the above reasons, the designer might have to choose implementing the special part of his digital circuit on a VLSI chip. In such a case, he might prefer to integrate all of the digital circuit he is designing into one chip.

In summary, there are many reasons that push a designer to use VLSI technology and fabricate his own IC instead of completely depending on *off-the-shelf* components to design his circuit (or part of it).

## **1.2 Hardware Programming Languages (HPLs)**

To aid communication between digital circuit designers, computer description languages(HDLs) evolved from the research field. HDLs were initially designed to describe digital circuits at the behavioral level. Later on, other applications for HDLs emerged. They have been used as input to a simulator at the register transfer level, and as input to a hardware compiler that automatically translates the high level description to logic design.

As digital circuits increased in complexity and the variety of uses, the benefits of HPLs increased more and they started to be a universal tool for designing digital circuits. An example of a hardware programming language that supports HDL, a hardware compiler and a register transfer level simulator is UAHPL (Universally A Hardware Programming Language).

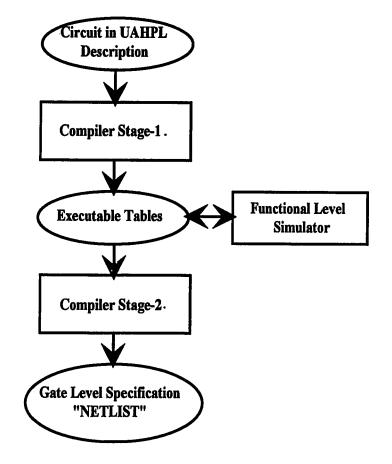

UAHPL, an extension of A Hardware Programming Language (AHPL), is used as the register transfer language for specifying a digital design. It is a simple language yet sufficient to model highly complex digital systems such as parallel processors and data flow machines. It has a compiler that converts the circuit specifications into an intermediate representation in form of tables after performing syntax and semantic analysis. This intermediate form can be used by the supplied simulator to verify whether the specification exhibits the desired behavior described in the

Figure 1.1: Diagram of UAHPL system.

specification. Another compiler translates the intermediate tabular form to logical netlist that gives details about the gates needed for the design and their relative interconnections. A diagram of UAHPL system can be seen in Figure 1.1.

## 1.3 VLSI Technology

VLSI or Very Large Scale Integration, refers to a technology through which it is possible to implement large circuits -circuits with up to a million transistors- in silicon. VLSI has been successfully used to build microprocessors, memory controllers, I/O controllers, and interconnection networks. It can also be used to implement complete digital systems in silicon as opposed to using MSI and LSI off-the-shelf components [2].

There exist many advantages for implementing digital systems in silicon such as:

- Achieving additional complexity in silicon. VLSI allows complexity to be included on a single silicon substrate. This means that complex digital functions, requiring tens of ICs, can fit onto a single silicon die and be integrated in one IC. This will enormously reduce board space requirements.

- Increasing reliability. Board design reliability increases as fewer parts are placed on a circuit board. This reliability continues to improve as a lower parts count contributes to a reduction in connections and traces on the circuit board.

- Maximizing performance. Timing problems will be reduced by using as less ICs as possible on the circuit board. The same goes for power requirements.

- Providing security for new designs. Using off-the-shelf ICs provide the designers with a very little security for their designs. The only way of securing their designs is by clearing the IC title from the top side of the case. On the other side, no one can predict the circuit implemented by a private IC. Thus, designs that uses at least one private IC will be protected from illegal copies.

Designing a VLSI circuit involves a trade-off between cost, performance, ease of design, time, and many other factors. A good layout is one which occupies minimum area, uses short wires for interconnection, and uses as few *vias* as possible [2].

Since the complexity of VLSI circuits is in the order of millions of transistors, designing a VLSI circuit is a complex task. Clearly it is not possible to sit down with paper and pencil to design a million-transistor circuit. Instead, there evolved many styles for designing a VLSI layout that extensively reduce the amount of effort and time exerted by the engineer. Also many computer software were implemented to aid the design of a VLSI layout.

### **1.3.1 Layout Styles**

There are several styles for a VLSI layout. Mainly, the style of the layout is determined by the way it is designed, and by the type of VLSI cells used. Some of these layout styles are:

- Full custom,

- Gate array,

- Standard-cells,

- General-cells,

- PLA (Programmable Logic Arrays),

- FPGAs (Field Programmable Gate Arrays).

The complexity of implementing a VLSI layout decreases from top to bottom for these styles. *Full custom layouts* are completely designed by hand using a layout editor. The concept of VLSI cells does not exist in such style. The designer has to implement all VLSI circuits that represent the digital components of the circuit. In standard- and general-cell styles, a set of pre-designed VLSI circuits are used to represent different digital components. These VLSI circuits are called macro-cells (cells for short) or modules<sup>1</sup>. The difference between these two styles is the type of cells they use. In standard-cell style, usually all different cells have fixed height, as opposed to cells of the general-cell style which can be of varying heights.

A detailed description, merits, and shortcomings of each of these styles can be found in [2], [5].

### **1.3.2 Generating VLSI Layouts**

Physical design of a VLSI circuit is the phase that precedes the fabrication of the circuit. The performance, area, and reliability of the circuit depends critically on the way the circuit is physically laid out. As a conclusion, physical design is a complex optimization problem. It is therefore customary to subdivide the problem into more manageable subproblems. A common subdivision is as follows

- Logic assignment

- Cells Placement

- Nets Routing

### Logic Assignment

The compiler of the hardware description language (HDL) used to generate the design of a digital system represented in netlist format will have its own set of gates which are used to specify the logic design. For example, it could have a 20-input

<sup>&</sup>lt;sup>1</sup>The terms cell and module will be used interchangeably throughout the chapters of this thesis.

**AND** gate, 4-input **OR** gate, 3-input **NOR** gate, 5-input **AND** gate, etc. It is not practical to implement all VLSI cells to represent all different gates used by the hardware compiler. Moreover, some of these gates might not have a feasible VLSI design, while others could need special technology to be implemented.

Logic assignment is the process of unifying these parameters. A pre-specified set of universal gates is prepared for the system and during the assignment stage, all gates of the digital system's netlist are replaced by an equivalent design of gates in the system. A new netlist that has only gates available in the system library will be generated in the assignment stage. Each gate of the system library has a VLSI design that represents it. When creating the final VLSI layout, each gate or cell is replaced by its VLSI design that is already available and previously simulated and checked [19].

### Cells Placement

Placement is the task of finding the exact positions of each cell in the new netlist that are to be placed in the VLSI layout. Added to the two main objectives which are minimizing total wire length and layout area, placement has one major objective to satisfy and that is facilitating routing. A router uses the space area between placed cells to connect different pins of the cells with each other. In the placement stage, enough spacing must be afforded to allow routing of all nets.

Many techniques exist for the placement task. They can be broadly divided into two categories: *constructive* and *iterative*. A *constructive technique* will usually begin by placing one cell in the layout, then it starts picking other cells one at a time and tries to find the most suitable place for them. It is fast, but usually does not generate optimistic layouts [2], [5].

Iterative techniques begin by a complete initial layout that could have been acquired randomly or from a constructive algorithm, and improve upon this initial solution to reach a better one. They consume a lot of execution time, yet sometimes might not markedly improve the initial solution.

### Nets Routing

Routing is usually the most difficult and time consuming stage. Detailed routers connect all physical pins of a net on different cells to each other randomly using some connecting material like silicon or metal. From an electrical point of view, it means to keep them at the same potential.

A detailed router for the *general-cell style* is restricted to put these routes only in a space area between the cells of the layout. Since routing all nets of a VLSI design is a must, then insuring enough space ahead of the routing stage will save a lot of time. Thus, a step called global routing is usually done ahead of the detailed routing.

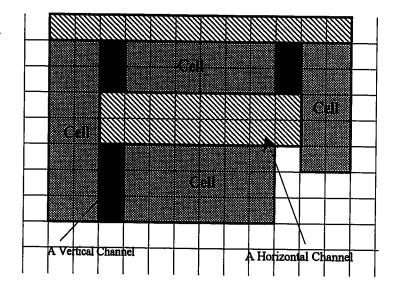

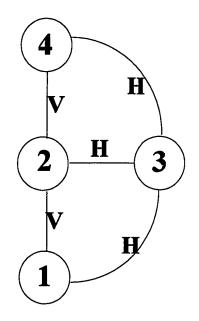

Global Router This task is usually inserted exactly after the placement stage to help achieve complete routing of the design. The space area between two cells that is parallel to the vertical borders of the cells is called *vertical channel*. If this space area is parallel to the horizontal borders of cells, then it is called a *horizontal channel*.

The placement stage can be modified so that it produces the data of the exact location and dimensions of every channel in the layout after the initial placement task. Global routing uses these data and the data of available nets according to the netlist and determines the exact channels used to connect different pins of different cells. Moreover, it can tell how many wire segments are to pass in each channel assuming that the router will always select the shortest path to connect pins of a net. This assumption is safe, and in fact supports the objective of minimizing the total wire length.

According to the information gained from the global routing task, spacing between cells can be exactly determined, and in most cases will be enough to route all nets. The initial layout acquired from the placement stage can be modified to support this amount of free space.

**Detailed Router** The detailed router receives data from the placement stage that has the exact locations of cells in the layout. According to the netlist, it connects every two pins at a time using the shortest available path. Global routing will certainly improve the routing process but there still could be some connections not accomplished due to the fact that the detailed router may not use the same channels that were predicted in the global routing stage. The detailed router will of course tell if any of these non-accomplished connections exist. A designer can finish these connections by hand using a layout editor.

### 1.3.3 VLSI Layout Programs

Many computer programs that aid the design of VLSI layouts were implemented by different universities, research institutes, and commercial companies. They support the process of designing a layout by tools that check the design correctness against VLSI rules and simulate the functionality of the final design [1], [3], [6]. One of these famous programs is MAGIC. It is a VLSI layout editor with a built-in simulator. It supports also a circuit extractor that saves the layout in many different formats used by other tools for electrical verification, simulation, or printing for example [3], [17].

### **1.4** AutoVLSI

AutoVLSI is an integrated system that automatically generates VLSI mask layout for any digital circuit described by a netlist. This netlist description can be obtained from the hardware compiler of any hardware programming language (HPL). For several years in KFUPM, a hardware programming language called UAHPL has been used to describe digital circuits, simulate them, and generate their corresponding netlists. The system proposed in this thesis was tuned to UAHPL type of netlists.

The system main objective is to minimize turn-around time. Other objectives are to minimize total wire length and total layout area. *AutoVLSI* system has a library of general VLSI cells. All these cells were designed and simulated to make sure that generated layouts using these cells will be correct by construction.

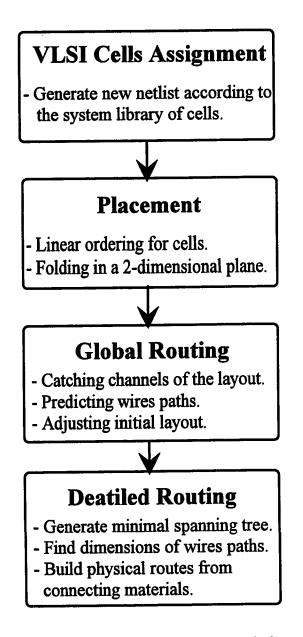

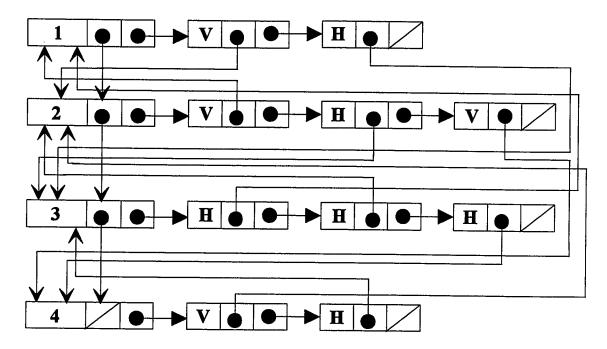

AutoVLSI system can be broadly divided into four basic stages. The first stage assigns VLSI cells from the cell library of the system to gates of the layout netlist description. The second stage is placement. It finds the best position of each cell according to its size and the connectivity relation between it and all other cells in the layout. The third stage which is global routing, predicts where the detailed router is expected to run wires on the layout and adjusts the layout such that enough space is supplied between cells of the layout. Finally, the fourth stage is the detailed routing. A software that uses Lee algorithm is used to connect different pins of cells which belongs to the same net by wire segments of different materials. Segments are placed in a way that each different net is electrically isolated from any other net.

Each one of these stages has several tasks (see Figure 1.2). Many heuristics and algorithms were studied, modified as needed, and then implemented to achieve a system that best accomplishes its objectives.

### **1.5** Description of Contents

**Chapter 2** addresses logic assignment. It explains the methodology of general cell library and the rules of designing general cells to be used by *AutoVLSI* system. A sample set of VLSI cells used by *AutoVLSI* are described in this chapter, and a procedural algorithm which assigns these cells to gates used by UAHPL is given.

**Chapter 3** is about the placement stage. It starts by giving an introduction about placement problem, how it is defined, the complexity of the problem, and how a layout quality is found. Then different techniques of placement are discussed, and finally how placement is done in *Auto VLSI* is explained.

Chapter 4 explains how global routing is done to predict wires' paths on the layout plane ahead to the detailed routing stage. The global routing algorithm adopted by *AutoVLSI* is explained, and the complete operation is illustrated by a small layout example.

**Chapter 5** starts by giving an overview about the function of detailed routers. It focuses on maze routing, and finally explains how the router program that was earlier implemented is integrated with other software to form the *AutoVLSI* system.

Chapter 6 is the conclusion of this thesis. It summarizes the work, and shows some results and statistical data. It explains how compaction can be applied and

Figure 1.2: Stages of AutoVLSI system including their tasks.

finally gives some ideas about future work.

.

# Chapter 2

# Logic Assignment

The problem of designing general-cell style layout, is very much similar to that of designing a PCB (Printed Circuit Board). However, instead of selecting off-the-shelf SSI or MSI components, we have to select components from a pre-designed VLSI cell library. And, instead of placing the components on a PCB, we place the cells in silicon. A common advantage is that designs can be completed quickly [2].

If we assume that there exist for every gate in every possible netlist description – generated by the HPL used- a VLSI circuit (or cell) that matches the gate's function, inputs, and outputs, then there is no need for any logic assignment. The designer must only be concerned about where to place each VLSI cell on the layout floor and how to interconnect different pins of the cells according to the netlist description.

However, the above assumption does not apply for UAHPL and many other HDLs. A stage called *logic assignment* is needed to transform the input netlist into a netlist of cells available in the system library.

## 2.1 Logic Assignment for UAHPL Gates

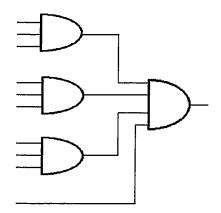

Not all gates used by UAHPL have a corresponding cell in the library. For example, UAHPL could use a 10-input AND gate in its generated netlist. The solution depends absolutely on available VLSI cells in the system's library of cells. If there exist 3-input and 4-input AND VLSI cells, then the 10-input AND gate will be replaced by three 3-input AND cells and one 4-input AND cell (see Figure 2.1 (a)).

In general, it is not possible to try matching all possible gates used by an HPL. The alternative is to have in the library of VLSI cells the modules for the universal logic gates which are 2-input NAND cell or 2-input NOR cell. If we want to replace the 10-input AND gate, then we would need six 2-input NAND cells and three 2-input NOR cell as the circuit shows in Figure 2.1 (b).

AutoVLSI system first reads the types of VLSI cells available in the system library. Then it checks for every gate if an equivalent cell exists with the same number of inputs. If so, it does not take any action for such a gate. On the other hand, if there does not exist an equivalent cell for one of the gates, then it substitutes that gate by universal cells (NAND/NOR) as needed.

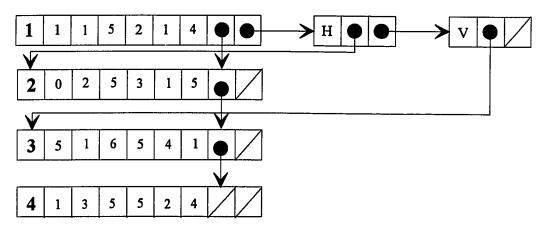

The software that does the logic assignment is called COOKNET. It receives three input files. The first is GATES.LIB which is prepared by the user and contains the data for the VLSI cells available in the system library. The other two input files are the ones generated by the hardware compiler of UAHPL and represent the netlist description of the design. They should have been extracted from a file that has the extension "ERD". These two files are to be named G1.DAT & IO1.DAT. COOKNET produces two output files, namely G2.DAT & IO2.DAT. All gates

(a) 10-input AND gate using 3-input and 4-input AND cells.

(b) 10-input AND gate using universall-input NAND and 2-input NOR cells.

Figure 2.1: Logic assignment for a 10-input AND gate.

represented in G2.DAT file have equivalent VLSI cells in the system library as was imposed by the user.

Beside performing logic assignment, **COOKNET** will also eliminate buffers used in the design, redundant inverters, and any isolated gates which neither their inputs nor output are connected to other gates.

## 2.1.1 AutoVLSI Library of VLSI Cells

A very small library of primitive VLSI cells was prepared while developing Auto VLSI system. The current library has ten different cells that are needed by the logic assignment stage to replace different gates of netlist descriptions generated by UAHPL for any digital design. These are:

- 1. Ex-input (External Input) cell.

- 2. Ex-output (External Output) cell.

- 3. 1-input NAND cell, to work as an INVERTER.

- 4. 1-input NOR cell, to work as an INVERTER (same as the cell in 1).

- 5. 2-input NOR cell.

- 6. 3-input NOR cell.

- 7. 2-input XOR cell.

- 8. D Flip-Flop cell with SET control.

- 9. D Flip-Flop cell with **RESET** control.

10. D Flip-Flop cell with ENABLE control.

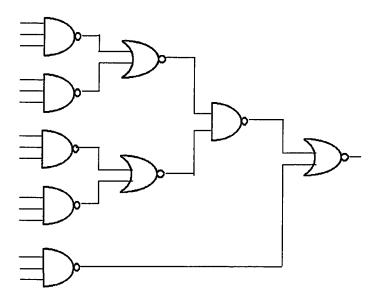

Each VLSI cell is carefully hand designed using the MAGIC layout editor, and simulated using both its built-in RSIM simulator and RNL [1],[17]. The cells layouts are given in Figure 2.2.

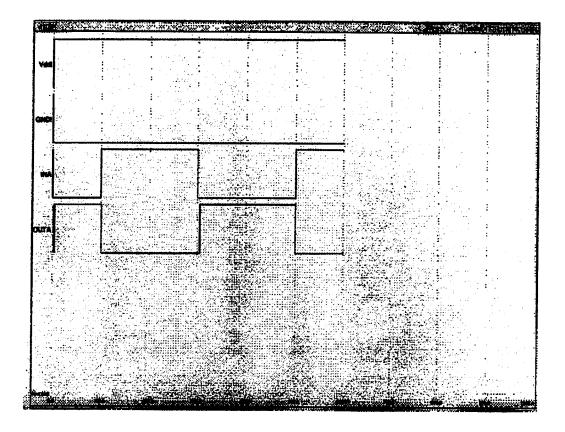

Simulation outputs of the INVERTER (1-input NAND gate), 2-input NOR, and D Flip-Flop with SET control cells using MAGIC built-in RSIM simulator are given in Figures 2.3, 2.4, and 2.5 respectively.

The data file *GATES.LIB* for the above library of VLSI cells have five records only. The first two cells (*Ex-input/output*) and the last three cells (*D Flip-Flop's*) do not need to be specified since their existence is mandatory to UAHPL for all designs. Each record representing a cell would consist of three pieces of information: cell name, type number, and number of inputs of the cell. Cell name can be any combination of letters or numbers, while type numbers are predefined according to the gate type and they are given in Figure 2.6. These type numbers are the ones used by UAHPL to identify the gates used in the netlist description. They can be seen in *G1.DAT* file. *GATES.LIB* file for the above list of cells is given in Figure 2.7.

**COOKNET** software modifies the type numbers of all cells in its output files. It replaces the second digit from the left of the type number by the number of inputs of the cell as found in *GATES.LIB* file. For example, the *1-input NAND* cell would have a type number 4102, while the *2-input NOR* cell would have a type number 4205. These modified type numbers are very important to be understood since actual cells files will be named after them.

Figure 2.2: VLSI circuits of the cells in AutoVLSI library.

Figure 2.3: RSIM simulation output for cell 4102.MAG (i.e., INVERTER gate).

.

.

Figure 2.4: RSIM simulation output for cell 4205.MAG (i.e., 2-input NOR gate).

.

Figure 2.5: RSIM simulation output for cell 4336.MAG (i.e., *D Flip-Flop* with **SET** control).

| TYPE NUMBER | GATE TYPE | TYPE NUMBER | GATE TYPE |

|-------------|-----------|-------------|-----------|

| 3998        | PASS      | 4017        | BUSEST    |

| 3999        | WIRE      | 4018        | EXOUTPUTS |

| 4001        | AND       | 4019        | EXOUTPUTS |

| 4002        | NAND      | 4020        | EXBUSES   |

| 4003        | OR        | 4021        | EXBUSESO  |

| 4004        | XOR       | 4022        | EXBUSESA  |

| 4005        | NOR       | 4023        | EXBUSEST  |

| 4006        | DFCS      | 4024        | CLUNIT    |

| 4007        | DFF       | 4025        | CLUI      |

| 4008        | AUX       | 4026        | CLUO      |

| 4009        | MEMCK     | 4027        | CTERMS    |

| 4010        | MEMEN     | 4028        | FNREG     |

| 4011        | МЕМЈК     | 4029        | CND       |

| 4012        | INPUTS    | 4030        | ORCS      |

| 4013        | OUTPUTS   | 4031        | CLAND     |

| 4014        | BUSES     | 4032        | CLNAND    |

| 4015        | BUSESO    | 4033        | CLOR      |

| 4016        | BUSESA    | 4034        | CLXOR     |

Figure 2.6: Table of predefined gates' type numbers.

| NAND1 | 4002 | 1 |

|-------|------|---|

| NOR1  | 4005 | 1 |

| NOR2  | 4005 | 2 |

| NOR3  | 4005 | 3 |

| XOR2  | 4004 | 2 |

Figure 2.7: List of GATES.LIB file.

## 2.2 AutoVLSI General-cell Library

The general-cell layout style relaxes a lot of the restrictions imposed by standard-cell layout style. Cells can have any rectangular shape resulting in a better arrangement and a more compact floorplan. The main advantage of the general-cell style is the ability of storing larger blocks such as arithmetic/logic units, registers, and memories in the cell library. Such blocks can be designed to have efficient layout characteristics [2].

However, there are some rules when designing a *general-cell* used by *AutoVLSI* system. These rules are explained in the following subsection.

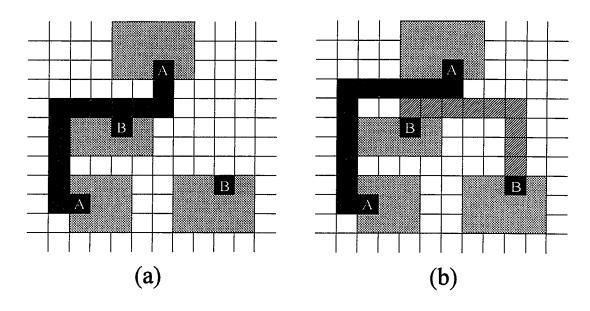

## 2.2.1 Rules of Designing a VLSI Cell for AutoVLSI System

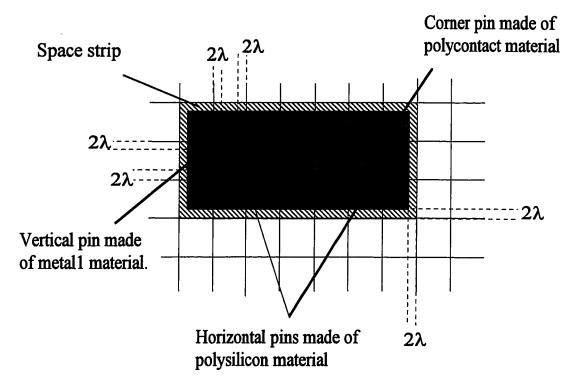

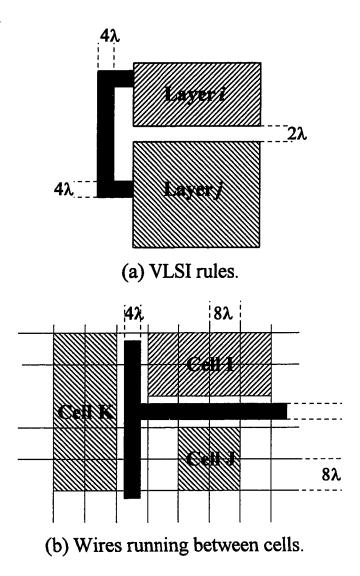

As mentioned above, AutoVLSI imposes some rules on the VLSI cells used. Some of these rules are mandatory while others are optional. However, they are very easy to apply and do not violate the relaxation of general-cell style. These rules are listed below and illustrated in Figure 2.8.

- Cells must be of rectangular shape.

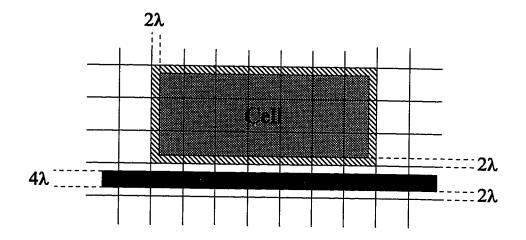

- For the purpose of satisfying VLSI design rules explained in Section 4.3, Auto VLSI assumes the layout to be a 2-dimensional grid plane where a grid size is  $(8 \times 8)\lambda$ , and the minimum allowed spacing between any two cells is  $4\lambda$ . Every cell must be centered in between  $h \times w$  grid units such that space strips, considered as part of the cell, of width equal to  $2\lambda$  are left empty all around the cell (see shaded area in Figure 2.8). By doing so, Auto VLSI satisfies the limitation of leaving at least  $4\lambda$  of space between any two cells placed on the

floor even if they were placed next to each other. Each cell's height or width will be a multiple of 8 plus  $4\lambda$ . For example, if a cell occupies one grid unit such as *Ex-input* or *Ex-output* cells, then actual cell height and width will be  $4\lambda$ . A cell occupying 5-vertical grid units will have actual height equals to  $[(5-1)\times 8] + 4 = 36\lambda$ . Also a cell occupying 3-horizontal grid units will have actual width equals to  $[(3-1)\times 8] + 4 = 20\lambda$ .

- Pins of a cell [inputs, outputs, clock (Clk), power (Vdd), or ground (Gnd)] must lie on the borders of the cell. If on a horizontal border then they must be of *polysilicon* material, else if they are on a vertical border then they must be of *metal1* material. If a port resides on a corner then it must be a contact point between *polysilicon* and *metal1* materials.

- The material of a pin should at least cover the middle  $4\lambda$  of the grid they are laid on.

- It is preferable that every pin has two or more occurrences on different borders of the cell since this will offer the router several choices to reach that pin in order to connect it to other pins.

- Pins on a cell can be named individually for the purpose of clearance and simulation. However, we suggest to name the clock pins as CK!, the power pins as Vdd!, and the ground pins as GND!. Putting an exclamation mark after these names will indicate them as global pins (i.e., all pins named Vdd! are supposed to have the same value at all times).

- Once a VLSI cell design is completed, it should be simulated individually to make sure that it is functioning correctly as expected.

Figure 2.8: Illustration of the rules of designing a VLSI cell for AutoVLSI system.

• A cell must be saved in MAGIC format and named according to the type numbers which COOKNET software adopts. The file names for the above listed library of cells are given in Figure 2.9. Cells files should be available in a sub-directory called "mag" which branches from the design main directory.

#### Saving the Data of VLSI cells

After designing the VLSI cells to be used by AutoVLSI system, the user has to create two data files which hold the information about the cells. The first file should be named AGHW.DAT which stands for "Actual Gates Heights & Widths", and will be used in the placement stage. While the second file should be named POC.DAT which stands for "Pins on Cells", and will be used

| CELL DESCRIPTION                | FILE NAME |

|---------------------------------|-----------|

| EX-INPUT                        | 4018.MAG  |

| EX-OUTPUT                       | 4013.MAG  |

| 1-input NAND                    | 4102.MAG  |

| 1-input OR                      | 4105.MAG  |

| 2-input NOR                     | 4205.MAG  |

| 3-input NOR                     | 4305.MAG  |

| 2-input XOR                     | 4204.MAG  |

| D Flip-Flop with SET control    | 4336.MAG  |

| D Flip-Flop with RESET control  | 4346.MAG  |

| D Flip-Flop with ENABLE control | 4309.MAG  |

Figure 2.9: Files names of VLSI cells in AutoVLSI system library.

in both global and detailed routing stages.

The Format of AGHW.DAT File

Every cell in the library should have a corresponding record in the file AGHW.DAT. A record would consist of three pieces of information: cell type, cell height, and cell width. Cells' height and width values should be in terms of grid units rather than  $\lambda$ .

AGHW.DAT file created for the above mentioned library of cells is given in Figure 2.10.

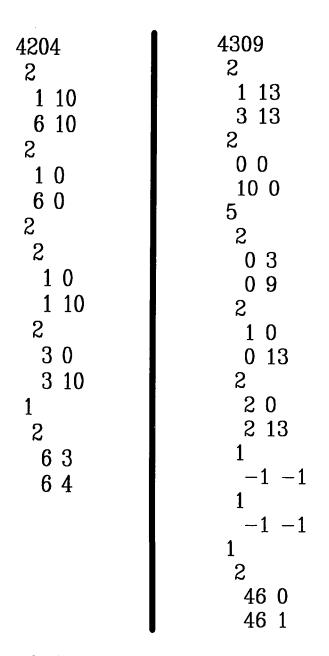

#### Format of POC.DAT File

This file should include all cells and define the coordinates in grid units for their pins with respect to the cell origin (0,0). There is a standard format for

| 4018 | 1  | 1         |

|------|----|-----------|

| 4013 | 1  | 1         |

| 4102 | 6  | 3         |

| 4105 | 6  | 3         |

| 4205 | 9  | 4         |

| 4305 | 9  | 6         |

| 4204 | 11 | 7         |

| 4309 | 14 | 47        |

| 4336 | 14 | <b>48</b> |

| 4346 | 14 | <b>48</b> |

Figure 2.10: List of AGHW.DAT file.

defining the coordinates of pins for every cell. The format is as follows:

Cell Type #

NUMBER OF PINS FOR THE VDD

Coordinates for the first Vdd pin

.

.

Coordinate for the last Vdd pin

NUMBER OF PINS FOR THE GND

Coordinates for the first Gnd pin

Coordinates for the second Gnd pin

.

•

Coordinate for the last Gnd pin **Number of Input pins** NUMBER OF PINS FOR THE FIRST INPUT Coordinates for the first pin of the first Input Coordinates for the second pin of the first Input

•

•

.

.

•

•

•

.

•

Coordinates for the last pin of the first Input NUMBER OF PINS FOR THE THIRD INPUT

NUMBER OF PINS FOR THE LAST INPUT Coordinates for the first pin of the last Input Coordinates for the second pin of the last Input

Coordinates for the last pin of the last Input Number of Output pins NUMBER OF PINS FOR THE FIRST OUTPUT Coordinates for the first pin of the first Output Coordinates for the second pin of the first Output

•

.

•

.

•

.

•

•

.

.

Coordinates for the last pin of the first Output NUMBER OF PINS FOR THE SECOND OUTPUT Coordinates for the second pin of the second Output Coordinates for the second pin of the second Output

Coordinates for the last pin of the second Output NUMBER OF PINS FOR THE THIRD OUTPUT

NUMBER OF PINS FOR THE LAST OUTPUT Coordinates for the last pin of the last Output Coordinates for the last pin of the last Output Coordinates for the last pin of the last Output

For the *Ex-Input* and *Ex-Output* cells, there is no Vdd or Gnd pins. Thus, the first two lines of their records in *POC.DAT* file have 0. For the *D Flip-Flops*, there are five inputs as imposed by UAHPL language. The first input stands for **D**, the second stands for **CLK**!, and the third input is either **ENABLE**, **SET**, or **RESET** control pins. The last two inputs are each assigned to one pin whose coordinates are (-1,-1) to indicate that it is not used. Each of these Flip-Flops has one output which stands for **Q**. The records for both, *2-input NOR* cell and *D Flip-Flop* with **ENABLE** control cell are given in Figure 2.11.

Figure 2.11: Records of 2-input NOR cell and D Flip-Flop with ENABLE control cell in POC.DAT file.

# Chapter 3

# Placement

## 3.1 Introduction

#### 3.1.1 Definition

In most general terms, placement consists of assigning rectangular modules to locations on a two-dimensional surface while satisfying given constraints and optimizing a given objective. Examples of constraints are to have all modules of standard shape and size. An example of an objective would be to minimize wire length.

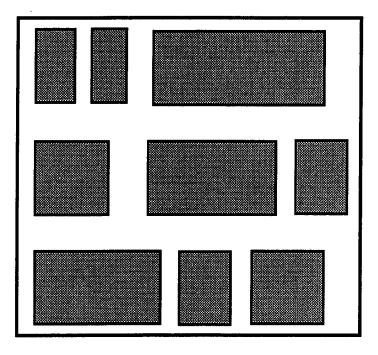

Constraints on modules affect to a certain extent the complexity of placement. If the modules are of standard shape and size, then it will be easy to place them in fixed row/column fashion as in the standard-cell layout style (Figure 3.1).

However, when the size of modules is allowed to be different while conserving the same shape as in the general cell layout style, the problem becomes more difficult. Modules in the last case can no more fit in row/column fashion without wasting a lot of space. Obviously, the worst case is when both size and shape of modules can

Figure 3.1: An example of a standard cell style layout.

vary.

#### **3.1.2 Cost Function**

The overall objective of placement is to facilitate routing. Other objectives are minimizing turn-around time (i.e., the time needed to finish generating the layout), minimizing overall area of the layout, and finally minimizing the total estimated wire length to be used later for routing nets. Facilitating routing objective is given the first degree of interest since placing blocks without being able to route them will result in a useless design. Chip area is important to be optimized in order to be able to put more functionality into a given chip. Minimizing the wire length will reduce the capacitive delays associated with longer nets and speed up the operation of the chip.

#### **Turn-around Time**

Turn-around time is the execution time needed for AutoVLSI system to generate the required layout. In many occasions, it is more important to the designer to accomplish the layout as fast as possible rather than producing a highly optimized layout nor a very short wired one. In AutoVLSI system, turn-around time is given a higher priority than both minimizing layout area and total wire length.

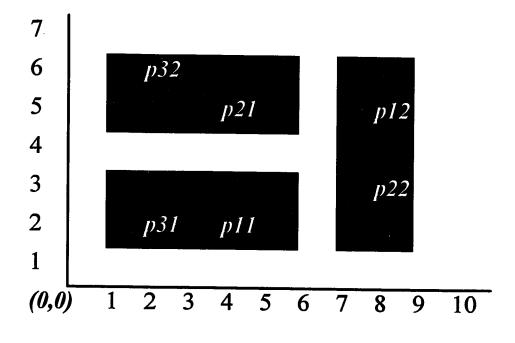

#### **Estimating Total Chip Area**

The layout is a grided two-dimensional plane that has a positive X-Y coordinate system (i.e., the lower left corner of the layout has 0,0 coordinate). In the general cell layout style, modules are defined to be rectangular boxes of different sizes. Each

## Algorithm for finding an estimate for the chip area

- 1 Find the Module *m* which has the maximum h(m) + y(m)

- 2 Find the Module m' which has the maximum w(m)' + x(m)'

- 3 Estimate area to be = [h(m)+y(m)] \* [w(m)'+x(m)']

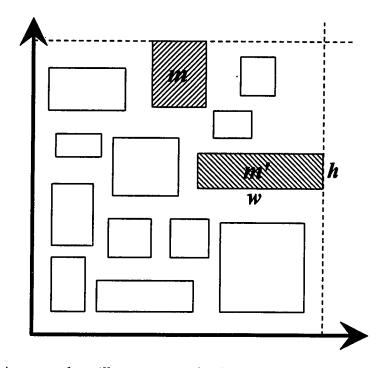

Figure 3.2: Algorithm for estimating layout area.

module m would have four characteristics:  $w_m$  module width,  $h_m$  module height,  $x_m$  the X coordinate of the module when placed, and  $y_m$  the Y coordinate of the module when placed. The chip area is the sum of modules area and the spacing left between placed modules for the purpose of routing. In *AutoVLSI*, a conservative assumption that no wiring is to be done above the highest module placed on top of the layout nor wiring is done to the right of the widest module placed in the most right boarder, will allow us to find an estimate for the chip area according to the algorithm in Figure 3.2.

Figure 3.3 shows an example of m and m' in a general cell layout.

#### **Estimation of Total Wire Length**

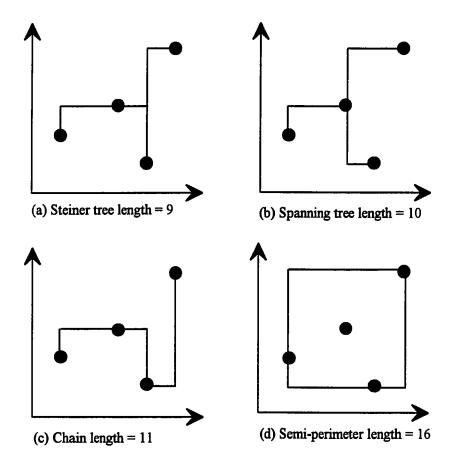

In estimating total wire length, we assume Manhattan geometry. The estimation procedure must be as quick as possible since circuits usually contain hundreds of multi-point nets. Next we briefly describe several techniques used for wire length estimation.

The shortest route for connecting a set of pins together is *Steiner tree* (Figure 3.4 (a)). In this method, a wire can branch at any point along its length. This method is usually not used by routers because of the complexity of computing both the optimum branching points (the Steiner points). *Minimal spanning tree* connections

Figure 3.3: An example to illustrate m and m in the algorithm for estimating layout area.

(Figure 3.4 (b) ), allow branching only at the pin locations. Algorithms exist for generating a minimal spanning tree given the netlist and modules' coordinates. An example of a minimal spanning tree algorithm is Kruskal. Such algorithm has a polynomial time complexity and requires long time to execute. *Chain connections* technique (Figure 3.4 (c) ) does not allow any branching. Each pin is connected to the next one in the form of a chain. Algorithms for accomplishing such connections are simpler to implement and faster but result in slightly longer interconnections. The most widely used technique for its simplicity, ease of implementation and speed of execution is the *semi-perimeter* approximation (Figure 3.4 (d)). The technique is to find the smallest bounding rectangle for all points to be connected by the wire, and estimate the wire length by half the length of the perimeter of this bounding rectangle.

Figure 3.4: Different techniques of estimating the wire length.

For Manhattan wiring, this method gives the exact wire length for all two-pin and three-pin nets. For four-pin nets, the semi-perimeter estimate will predict a wire length 33% less than both the chain connection and spanning tree techniques. However, in practical circuits, two- and three-pin nets are most common. This technique was adopted by *AutoVLSI*.

#### The Cost Function

It is common practice to define a cost function or an objective function, which consists of the sum of turn-around time, total chip area, and total estimated wire length. It has been stated that all these three objectives need to be minimized in order to achieve high quality layouts in a reasonable amount of time. The cost function used by *AutoVLSI* to evaluate the generated layout quality is as follows:

$$Cost = \alpha T + \beta A + \gamma W$$

where  $\alpha, \beta$  and  $\gamma$  are factors for turn-around time, chip area, and wire length relatively. These factors constitute the weight for each of the function objectives. They are set to 3, 2, and 1 relatively. These values indicate that turn-around time is the most expensive objective while area of the layout comes next in order. Finally, wire length is the cheapest and the objective to minimize it is given the lowest priority.

#### 3.1.3 Complexity of the Placement Problem

The placement problem is an NP-complete problem and, therefore, can not be solved in polynomial time. Even for the simplest placement style, namely standard-cell placement where modules are of fixed size and are to be placed in row/column fashion, there exist as many as n! different layouts for placing n modules [2]. Therefore, it is not practical to try all possible layouts to find the best solution. Instead, many heuristic techniques were developed to give good solutions for the problem, not necessarily the best solution but they reduce the time of generating the layout a lot. Some of these heuristics are discussed in the following section [8].

### **3.2** Techniques of Placement

The placement problem involves the assignment of building blocks of the layout to specific locations. This includes the assignment of logic gates within a gate array, the placement of cells in a standard cell layout, or the placement of macro cells in a general cell layout [2], [5].

Placement algorithms may be subdivided into two basic categories: constructive placement and iterative improvement. *Constructive placement* algorithms build a placement from initial data such as sizes of the cells to be placed and the netlist (i.e., the interconnections between cells). *Iterative improvement* algorithms start with a given initial placement (which can be given by the user or obtained by a constructive placement algorithm) and modify the layout to improve its quality [5].

## 3.2.1 Constructive Placement Algorithms

A constructive placement algorithm constructs a solution by placing one module at a time. Two decisions have to be made and these are:

- 1. which module to pick from the unplaced list of modules, and

- 2. where to place the selected module.

Most constructive placement algorithms are based on primitive connectivity rules. Typically, a seed module is selected and placed in the chip layout area. Then another module is selected according to the connectivity between it and the placed modules (most connected first) and is placed at a vacant location close to the placed modules, such that the wire length is minimized. These algorithms are generally very fast, but usually results in poor layouts. They take a very small amount of computation time compared to iterative algorithms.

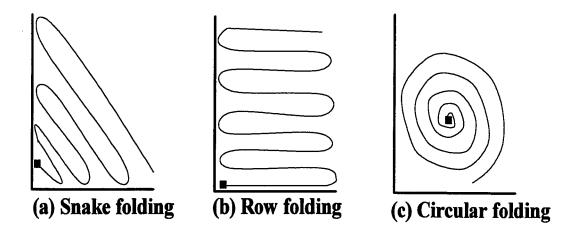

Some constructive placement algorithms are: linear placement & folding, numerical optimization, placement by partitioning, and force-directed technique. A full description of each can be found in [5], [3].

### 3.2.2 Iterative Improvement Algorithms

Iterative improvement algorithms produce good placement but require enormous amount of computation time. They start by a given placement solution that could be user defined, randomly built, or an output from a constructive placement algorithm, and try to improve layout cost by running several iterations.

The simplest iterative improvement strategy interchanges randomly selected pairs of modules and accepts the interchange if it results in a better cost. The algorithm terminates when no improvement is observed after a given large number of trials, or after running the algorithm for some maximum given amount of execution time. Currently popular iterative improvement techniques include simulated annealing, genetic algorithm, and some force-directed techniques.

### **3.3** Placement in AutoVLSI

The placement procedure used in *AutoVLSI* system to place general cells is constructive and consists of two phases. Its objective is to compromise between the speed of generating the layout, layout area, and total wire length; plus of course assuring full routibality. The first phase is to linearly order the cells in terms of their interconnection, in order to minimize wire length. Linear ordering of cells produces a one-dimensional layout as if a matrix consisting of one row or one column. The second phase is to fold these ordered cells on the two-dimensional layout in a manner that minimizes the layout area. It does so by leaving the minimum allowed spacing between each cell and its neighbors.

How much space to leave between a module and its neighboring modules is determined by the VLSI design rules. Auto VLSI deals with the layout as a rectangular array of grid cells. Every module when placed will occupy one or more grid cells. Routing material is supposed to run in the space between modules to connect different pins of different modules. In SCMOS technology, the common factor of the minimum allowed distance between any two layers is  $4\lambda$ , and the common factor of the minimum width of a routing material (metal or polysilicon) is also  $4\lambda$  (Figure 3.5 (a) ). Thus, we restrict our grid unit size to  $(8 \times 8) \lambda$ . This means that leaving one grid unit between any two modules will be sufficient to run one wire (whose width is  $4\lambda$ ) in between them while leaving a space of  $4\lambda$  between the wire and its neighboring cells (Figure 3.5 (b) ). From now on, the dimensions of a module are

Figure 3.5: Illustration of a grid cell and VLSI design rules.

Figure 3.6: Actual size of a cell.

relative to grid cells rather than  $\lambda$ . If a module's width equals to 3, and height equal to 2 then it is assumed to occupy a box whose width equals 3 grid cells, and whose height equals 2 grid cells, but the actual size of the module in terms of lambda is  $(28 \times 12) \lambda^2$ , since we leave  $2\lambda$  from each side of the cell to afford the  $4\lambda$  spacing constraint if a wire is to pass close to it (Figure 3.6).

## 3.3.1 Phase I: Linear Ordering of Cells

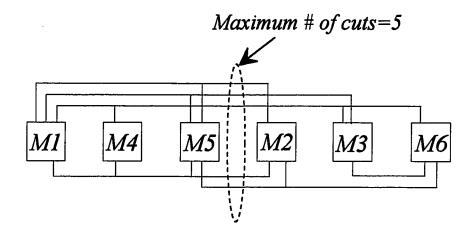

Linear ordering can be defined as follows: given a circuit consisting of modules interconnected with nets, put the modules in a linear sequence such that the number of nets cut by a plane separating two adjacent modules is minimized [2], [16].

The circuit will be described in this section by a set of modules and a set of nets. A net is a set of modules which are interconnected by one wire. The algorithm starts by selecting a seed module which will be the first module in the order, then

Figure 3.7: Illustration of terminated, continuing, and new nets.

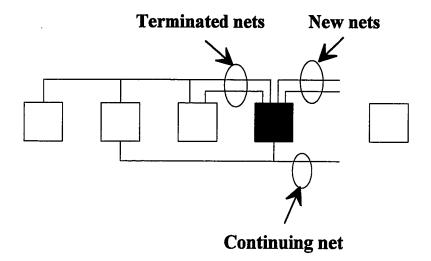

enters a **Repeat** loop. In each iteration of this loop a gain function is computed for every module in the set of unordered modules. The module with maximum gain is selected, removed from the set of the unordered modules, and added to the sequence of ordered modules. Before explaining how a seed module is selected, and how the gain is computed, let us define the terms *terminated net*, *continuing net*, and *new net*.

A net n is said to be terminated by module m and called *terminating net* if module m was the only remaining unordered module included in the set of modules of n. On the contrary, if none of the modules in the set of modules of net n is ordered, then n is a *new net* for all its modules. If some of the modules of a net nare ordered and **more than one** unordered modules belong to the set of modules of n, then n is a *continuing net* for those remaining unordered modules. Figure 3.7 illustrates graphically these three types of nets.

Now we can define the gain function for module m to be:

$gain_m$  = number of nets terminated by m-number of new nets started by m.

When computing the gain for the unordered modules in order to select the next one in sequence, a tie (i.e., more than one module having the same gain) could exist. A tie is solved by selecting the module which terminates the largest number of continuing nets. If another tie exist, the module that is connected to a larger number of continuing nets is preferred. If we have another tie, the most lightly connected module is selected. In case of another tie, the module that has the lowest index (was encountered first in the set of unordered modules) is selected. A Pascal like description of the linear ordering algorithm is given in Figure 3.8.

The following example (taken from [2]) is used to illustrate the linear ordering algorithm.

**Example 3.1** Given the following netlist with 6 modules [M1, M2, M3, M4, M5, M6] and 6 nets  $N1 = \{M1, M3, M4, M6\}$ ,  $N2 = \{M1, M3, M5\}$ ,  $N3 = \{M1, M2, M5\}$ ,  $N4 = \{M1, M2, M4, M5\}$ ,  $N5 = \{M2, M5, M6\}$ ,  $N6 = \{M3, M6\}$ , linearly order the cells so that the number of cut nets by a plane between any two cells is minimized. Assume M1 to be the seed cell.

- Solution:

- The linear ordering heuristic of Figure 3.8 will produce the following sequence [M1, M4, M5, M2, M3, M6]. At the first step, M1 is placed in the first location of the order since it is the seed cell. Then every module gain is computed and M4 comes to have the maximum gain, so it is placed in the second location. At the second step, we have a tie between modules M2, M3, and M5 having all a gain equal to -1. All three cells do not terminate any net. However, module

## Linear\_Ordering Algorithm

S:=Set of all modules;

Order:=Sequence of ordered modules; (\* initially empty \*)

Begin

Seed:=Select seed module;

Order:=[seed];

S:=S-{seed};

## Repeat

ForEach module m in S Do

Compute m gain as follows:

gain = number of terminated nets by m - number of new nets starting by m;

End ForEach

Select the module m\* with maximum gain;

If there is a tie Then

Select the module that terminates the largest nymber of nets;

If there is a tie Then

Select the module that has the largest number of continuing nets;

If there is a tie Then

Select the module with the least number of connections;

If there is a tie Then

Select the module that satisfies the previous " If" and has lowest index; End If;

End If;

```

End If;

```

End If;

Order:=[Order,m\*];

S:=S-{m\*};

Until S is empty;

End.

Figure 3.8: Linear Ordering algorithm.

M5 has the largest number of continuing nets and therefore it is selected in the second If statement of the algorithm and placed in the third location of the order. At the third step, M2 has a maximum gain and placed in position 4 of the order. At the fourth step we have a tie between the remaining modules M3 and M6 since they both have a gain equal to 0. The first If statement in the algorithm fails because both terminate one net. The second If statement also fails because they have the same number of continuing nets, and the third If statement fails also because they are both connected to the same number of nets. The Else statement of the algorithm directs to select M3 since it has the lower index. Finally, at the fifth step only M6 is left and so it has the maximum gain and selected to occupy position 6 in the order. A step-by-step execution of the algorithm showing how cells were selected in order is given in Figure 3.9.

A graphical representation of the ordered cells with their interconnection is shown in Figure 3.10.

In AutoVLSI system, N9.DAT is a file that has the data about each cell and the nets it participates in. In order to achieve linear ordering for cells, we need this data in a format of nets and their participated cells. The **GNETS** software, reads in N9.DAT file and produces NETS.GNE file that follows such format. Every net, followed by the cells participating in, reserves one entry in this file. The **LOC** software reads NETS.GNE file, and GP2.DAT file which shows the type of each cell. The **LOC** software starts by sorting all cells according to their index number. Then it sequentially moves input cells of the type "4018" from the main list of cells to put them at the beginning of the sequence of ordered cells since they are to be