Unlimited Pages and Expanded Features

Your complimentary use period has ended. Thank you for using PDF Complete.

# Computer Engineering Department Research Profile

Dr. Sadiq M. Sait Computer Engineering Department King Fahd University of Petroleum & Minerals

Your complimentary use period has ended. Thank you for using PDF Complete.

## **Ingineering Faculty**

### 20 Professorial Rank faculty members

- 2 Full Professor

- 2 Associate Professor

- **16 Assistant Professor**

- 6 lecturers

Unlimited Pages and Expanded Features

Your complimentary use period has ended. Thank you for using PDF Complete.

### rch Areas

- Data Communications & Computer Networks.

- Computer Applications: Robotics, Interfacing, Data acquisition, Machine learning, Data Mining.

- Digital Design Automation & VLSI System Design & Test.

- Computer Architecture & Parallel Processing.

- Computer Arithmetic & Cryptography.

Click Here to upgrade to Unlimited Pages and Expanded Features

### Research Projects: Data ions & Computer Networks

- Wireless Multi-hop Voice over IP over Wi-Fi using Client-Server UDP (user datagram protocol).

- Mobile Patient using sensor network.

- Wireless Local Area Networks Integration for Mobile Networks Operators.

- eTourism Promoter An Internet Assisted Location Tracker and Map Reader for Tourists.

- A Framework for Integration of Web-based Network Management and Management by Delegation.

- Radio Resource Management and QoS Control for Wireless Integrated Services Networks.

- Adaptive TCP Mechanisms for Wireless Networks.

- Engineering Modern Iterative Heuristics to Solve Hard Computer Network Design Problems.

### **Research Projects: Computer**

Click Here to upgrade to Unlimited Pages and Expanded Features

- Design of a wireless safety system for smart kitchen.

- Predicting log properties from seismic data using abductive networks.

- Design of an Intelligent Tele-robotic System.

- Designing and building a mobile emergency warning system for patients under health care.

- Context aware energy management system.

Click Here to upgrade to Unlimited Pages and Expanded Features

### Research Projects: Design VLSI System Design & Test.

- Iterative Heuristics for Timing & Low Power VLSI Standard Cell Placement.

- Parallelization of Iterative Heuristics for Low Power VLSI Standard Cell Placement.

- Efficient Test Relaxation Based Static Test Compaction Techniques for Combinational and Sequential Circuits.

- Efficient Test Data Compression Techniques for Testing Systems-on-Chip.

- Segmented Addressable Scan Architecture for Effective Test Data Compression.

Click Here to upgrade to Unlimited Pages and Expanded Features

### Research Projects: Design VLSI System Design & Test.

- Development of Digital Circuit Techniques for Clock Recovery and Data Re-Timing for High Speed NRZ Source-Synchronous Serial Data Communications.

- Fast context switching configurable architectures supporting dynamic reconfiguration for computation intensive applications.

- Development of Integrated Micro-electronic Heavy Metal Sensors for Environmental Applications.

- Multi-objective Finite State Machine Encoding using Non-Deterministic Evolutionary Algorithms targeting area, low power and testability.

- Design and Implementation of Scalable Interconnect Efficient LDPC Error Correcting Codes.

Click Here to upgrade to Unlimited Pages and Expanded Features

### Non-Deterministic Iterative Solve VLSI CAD Problems

- CAD Problems such as Floorplanning, Placement, Routing, Scheduling, etc., require an enormous amount of computation time.

- Iterative Heuristics such as Genetic Algorithms, Tabu Search, Simulated Evolution, and others have been found effective in solving several NP-hard optimization problems.

- Objective: To use a cluster of PCs to solve multiobjective VLSI CAD problems in order to improve quality and reduce run-time.

Unlimited Pages and Expanded Features

Your complimentary use period has ended. Thank you for using PDF Complete.

### D employ a Cluster of PCs to mputationally Intensive Tasks

- Clusters of low end PCs are easy to build.

- Tools such as MPI and PVM are available for message passing.

- Tools such as gprof, Intel's VTUNE Performance Analyzer, etc., are used for generating profiles for serial codes and determining the part of the code that has the bottlenecks.

- Iterative algorithms are non-deterministic, and dividing work load, i.e. partitioning the search space, is a challenge.

- The parallelizing model (i.e., Partitioning, Communication, Agglomeration and Mapping) is very well-defined for numerical problems, which are mostly deterministic. This is not the case for Iterative heuristics, which are non-deterministic.

Unlimited Pages and Expanded Features

Your complimentary use period has ended. Thank you for using PDF Complete.

# in our Current Cluster

- MPICH Library provides a flexible implementation of MPI for easier message-passing interface development on multiple network architectures.

- Intel® Trace Collector 5.0 applies event-based tracing in cluster applications with a low-overhead library. Offers performance data, recording of statistics, multi-threaded traces, and automatic instrumentation of binaries on IA-32.

- Intel® Trace Analyzer 4.0 provides visual analysis of application activities gathered by the Intel Trace Collector.

- TotalView (MPICH) is also used for observing communication between processors.

- Also used in Condor (for scheduling jobs on the cluster).

Unlimited Pages and Expanded Features

Your complimentary use period has ended. Thank you for using PDF Complete.

### p to Intel's R&D

- COE Department has faculty experienced in VLSI Design.

- Two books in the area of iterative algorithms and VLSI Design have been authored by the department faculty.

- The Technology Center being proposed in RI will have the state-of-art tools and equipment.

- Faculty and students currently interested in HPC and parallelization of heuristics can work together to address industrial and real-world problems.

Click Here to upgrade to Unlimited Pages and Expanded Features

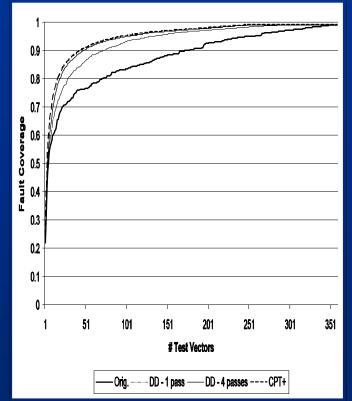

### Compaction & Compression or Comb. & Seq. Circuits

SOC Testing Challenges

Reduce amount of test data.

Reduce time a defective chip spends on a tester.

Test Compaction & Compression

Reduce the size of a test set as much as possible.

Test vector reordering for combinational circuits.

Steepen the curve of fault coverage vs. number of test vectors.

Click Here to upgrade to Unlimited Pages and Expanded Features

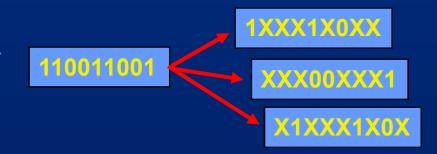

# Compaction & Compression or Comb. & Seq. Circuits

110011001

- Efficient Test Relaxation for Combinational & Sequential circuits

- Enabling technology for test Compaction & Compression Test power reduction

- Developed efficient test compaction techniques based on test relaxation.

- Test Vector Decomposition

- Maximizes test compaction by vector clustering techniques Maximizes test width-based compression techniques.

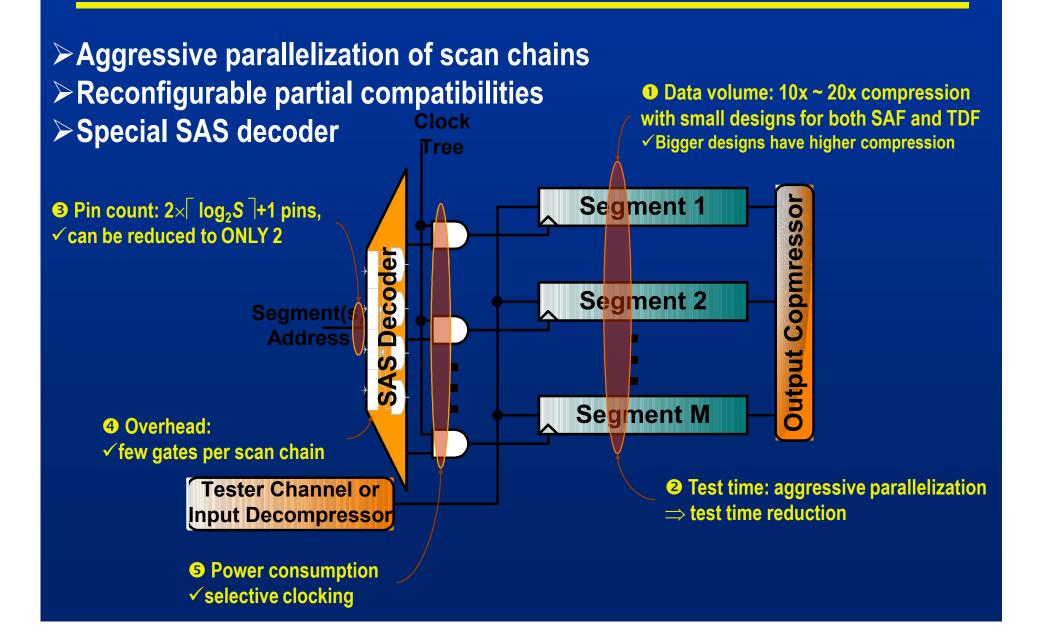

### ddressable Scan: Scan Test

Click Here to upgrade to Unlimited Pages and Expanded Features

- Test data volume challenge

- Limited IOs & unlimited increase in transistors Exponential increase in test data volume

### Tester pin count challenge

Tester cost is almost linear in number of pins

### Test time challenge

Critical path Hard to parallelize test loading massively

### Test power challenge

High activity leading to high power consumption.

Unlimited Pages and Expanded Features

Your complimentary use period has ended. Thank you for using PDF Complete.

### Addressable Scan

Your complimentary use period has ended. Thank you for using PDF Complete.

### lume & Test Time (Delay test)

| Total Data Volume  |              | 98 Mb  | Compression<br>Ratio |

|--------------------|--------------|--------|----------------------|

| SAS Data<br>Volume | 32 Segments  | 7.7 Mb | 12x                  |

|                    | 64 Segments  | 5.3 Mb | 17x                  |

|                    | 128 Segments | 4.5 Mb | 22x                  |

|                    | 256 Segments | 3.6 Mb | 27x                  |

### **\$Ms of annual test cost savings**

Click Here to upgrade to Unlimited Pages and Expanded Features

### Research Projects: Computer & Parallel Processing

- Load Balancing for Parallel Visualization of Blood Head Vessel Angiography on Cluster of PCs.

- Shared Channels in Interconnection Networks.

- Study of modified Multistage Interconnection Networks for Networks-on-Chips.

- Design of a Simulator for a Class of Dynamic Execution Processors.

- Beyond Instruction-Level Parallelism in Processor Architecture.

- Design and Performance Evaluation of a Distributed Crossbar Scheduler.

- Software Pipelining for Reconfigurable Instruction Set Processors.

Click Here to upgrade to Unlimited Pages and Expanded Features

### Research Projects: Computer Cryptography

- High-Performance Arithmetic for Cryptographic Applications.

- Design of efficient integrated circuits for the inverse computation in different finite fields.

- Design of Elliptic Curve Cryptography Architectures using parallel multipliers.

- Secure reliable storage system.

- Design, Analysis, and FPGA prototyping of High-Performance Arithmetic for Cryptographic Applications.

#### Click Here to upgrade to Unlimited Pages and Expanded Features

# Computer Engineering Faculty Research Profile