# Parallel Optical Architectures For Some Comparison-Based Problems

by

## Mahmood Hossain

A Thesis Presented to the

FACULTY OF THE COLLEGE OF GRADUATE STUDIES

KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

MASTER OF SCIENCE

In

**COMPUTER SCIENCE**

January, 1992

## **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

## Order Number 1354052

Parallel optical architectures for some comparison-based problems

Hossain, Mahmood, M.S.

King Fahd University of Petroleum and Minerals (Saudi Arabia), 1992

## PARALLEL OPTICAL ARCHITECTURES FOR SOME COMPARISON-BASED PROBLEMS

李泽李李李李李李李李李李李

PARALLEL OPTICAL ARCHITECTURES FOR SOME COMPARISON-BASED PROBLEMS

BY

MAHMOOD HOSSAIN

A Thesis Presented to the

FACULTY OF THE COLLEGE OF GRADUATE STUDIES

KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the

Requirements for the Degree of

MASTER OF SCIENCE

In

COMPUTER SCIENCE

JANUARY 1992

## KING FAHD UNIVERSITY OF PETROLEUM & MINERALS DHAHRAN, SAUDI ARABIA

This thesis, written by MAHMOOD HOSSAIN under the direction of his thesis committee, and approved by all the members, has been presented to and accepted by the Dean, College of Graduate Studies, in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE IN COMPUTER SCIENCE

| Т | h  | Δ | c  | ic       | C     | Λ  | n |   | 7 | • | ÷ | f | ŧ | Δ | Δ |

|---|----|---|----|----------|-------|----|---|---|---|---|---|---|---|---|---|

|   | 11 | C | -2 | <u> </u> | <br>L | ŧ, | ш | ı | ł |   | ŧ | Ł | ŧ | C | 드 |

| Cha | irman ( <i>Dr</i> . | SUBBA   | ARAO  | GHANT  | r <sub>A</sub> |

|-----|---------------------|---------|-------|--------|----------------|

| 1   | hohsan              | G       | LuZi  | )      |                |

| Men | nber ( <i>Dr.</i> ) | MOHSI   | Ŋ GUI | ZANI)  |                |

|     | Jehn                |         | lur   | ld     | _              |

| Mer | nber (Dr.           | VII)MAZ | ZANY  | ILDIZ  | )              |

|     | 7                   | 7       | ا ا   | ノ<br>  |                |

| Mei | nber ( <i>Dr</i> .  | NAŜIR   | AL-D  | ARWISE | <i>I</i> )     |

Dr. MOHAMMED AL-TAYYEB

Department Chairman

Dr. ALA H. AL-RABEH

Dean College of Graduate Studies

Date: 19.1.92.

### **ACKNOWLEDGEMENT**

Acknowledgement is due to King Fahd University of Petroleum and Minerals, specifically the Information and Computer Science Department for providing the opportunity to carry out this research work.

I gratefully acknowledge the guidance of my thesis supervisor Dr. Subbarao Ghanta and the help of the thesis committee members Dr. M. Guizani, Dr. Y. Akyildiz and Dr. N. Al-Darwish. I also express my gratitude to all the members of the Optical Computing Group at CCSE. I must render my sincere thanks to my friend Husni Al-Muhtaseb who translated and typeset the thesis abstract in Arabic.

Lasily but not least let me mention my sincere appreciation to my friends and well-wishers home and abroad who helped and encouraged me throughout: Abdullah, Adel, Hitu, Garout, Ismail, Jaweed, Limalia, Khalid, Kornel, Noman, Moazzem, Moshiur & Rita, Monti, Mukul, Murad & Dolly, Purushothaman, Rana, Rashed, Said, Salah, Shantanu & Shangita, Dr. Shafique, Shelly, Dr. Tayyeb, Yahya, Zia; they have been a constant source of support.

## TABLE OF CONTENTS

| Chapter                      | rage                                                                 |

|------------------------------|----------------------------------------------------------------------|

| ACKNOWLEDGEMENT              | iv                                                                   |

| LIST OF FIGURES              | ix                                                                   |

| ABSTRACT (English)           | xi                                                                   |

| ABSTRACT (Arabic)            | xii                                                                  |

| 1. INTRODUCTION              |                                                                      |

| 1.1 Objective of the Study   | 1                                                                    |

| 1.2 Thesis Organization      | 5                                                                    |

| 2. BACKGROUND WORK           | -                                                                    |

| 2.1 Optical Computing        | 6                                                                    |

| 2.2 Optical Architectures    | 8                                                                    |

| 2.3 Inter-processor Intercon | nection                                                              |

| 2.4 Conclusion               | 14                                                                   |

|                              | TION OF CLOS NONBLOCKING-BROADCASD WITH CONSTANT TIME NETWORK CONTRO |

| 3.1 Introduction             | 15                                                                   |

| 3.2 Multistage Interconnecti | ion Network with Broadcast Capability                                |

| 2.2 Describes Describe                                                                                                                                                       |                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 3.3 Previous Results                                                                                                                                                         | 19                  |

| 3.4 Proposed Optical Multistage Nonblocking Broadcast Network                                                                                                                | 20                  |

| 3.4.1 Switch Module                                                                                                                                                          | 20                  |

| 3.4.2 Optical Fiber Inter-stage Links                                                                                                                                        | 22                  |

| 3.5 Network Controller                                                                                                                                                       | 24                  |

| 3.5.1 Optical Vector Processor Primitive Operations                                                                                                                          | 24                  |

| 3.5.2 Control Algorithm                                                                                                                                                      | 30                  |

| 3.6 Conclusion                                                                                                                                                               | 37                  |

|                                                                                                                                                                              | 000                 |

| 4. OPTICAL REALIZATION OF CONSTANT TIME SORTING ALON A PROCESSOR MATRIX WITH A RECONFIGURABL PROCESSOR BUS SYSTEM                                                            |                     |

| ON A PROCESSOR MATRIX WITH A RECONFIGURABL                                                                                                                                   | E INTER             |

| ON A PROCESSOR MATRIX WITH A RECONFIGURABL PROCESSOR BUS SYSTEM                                                                                                              | E INTER38           |

| ON A PROCESSOR MATRIX WITH A RECONFIGURABL PROCESSOR BUS SYSTEM  4.1 Introduction                                                                                            | E INTER3840         |

| ON A PROCESSOR MATRIX WITH A RECONFIGURABL PROCESSOR BUS SYSTEM  4.1 Introduction  4.2 Proposed Optical vector Processor Matrix Architecture                                 | E INTER3840         |

| ON A PROCESSOR MATRIX WITH A RECONFIGURABL PROCESSOR BUS SYSTEM  4.1 Introduction  4.2 Proposed Optical vector Processor Matrix Architecture  4.2.1 Optical Vector Processor | E INTER 38 40 40 42 |

| Chapter                                                                                                      | Page        |

|--------------------------------------------------------------------------------------------------------------|-------------|

| 4.3 Computing the sum of a binary sequence on a Reconfigurable Processor  Array in constant time             | 48          |

| 4.4 Sorting N numbers on a Reconfigurable Processor Matrix of NxN Optica  Vector Processors in constant time |             |

| 4.5 Conclusion                                                                                               | 56          |

| 5. BINARY-TREE-COMPUTATION ON OPTICAL RECOVECTOR PROCESSOR ARRAY                                             | )NFIGURABLE |

| 5.1 Introduction                                                                                             | 58          |

| 5.2 Optical Reconfigurable Bus System                                                                        | 59          |

| 5.2.1 Optical Vector Processor                                                                               | 60          |

| 5.2.1.1 Connecting Local Bus                                                                                 | 61          |

| 5.2.1.2 Data Broadcast                                                                                       | 62          |

| 5.3 Binary Tree Computations on ORBS                                                                         | 62          |

| 5.4 Conclusion                                                                                               | 67          |

| 6. PARALLEL SELECTION AND PARALLEL QUICKSORT AL ON ORBS                                                      | GORITHMS    |

| 6.1 Introduction                                                                                             | 70          |

| 6.2 Preliminaries                                                                                            | 71          |

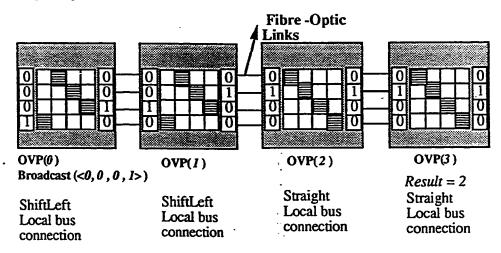

| 6.2.1 Shifting a binary sequence                                                                             | 71          |

| 6.3 Some useful procedures                                                                                   | 72          |

| Cnapter                                                       | rage |

|---------------------------------------------------------------|------|

| 6.3.1 Computing unary prefix sum of a binary sequence on ORBS | 74   |

| 6.3.2 Unary subtraction on ORBS                               | 74   |

| 6.4 Parallel Select Algorithm                                 | 76   |

| 6.5 Parallel Quicksort Algorithm                              | 82   |

| 6.6 Conclusion                                                | 86   |

| 7. CONCLUSION AND FUTURE WORK                                 | 87   |

| REFERNECES                                                    | 89   |

## LIST OF FIGURES

| Fig  | ure                                           | Page           | е  |

|------|-----------------------------------------------|----------------|----|

| 3.1  | NxN Nonblocking Clos Network                  |                | 7  |

| 3.2  | Switch Module                                 | 2              | 20 |

| 3.3  | Vector Copy                                   | 2              | 24 |

| 3.4  | Compliment of a vector                        |                | 25 |

| 3.5  | Bitwise UNION of a vector                     |                | 26 |

| 3.6  | Bitwise ANDing of a vector                    |                | 27 |

| 3.7  | UNION of two vectors                          |                | 27 |

| 3.8  | Intersection of two vectors                   |                | 28 |

| 3.9  | Masking out trailing $I$ 's from a vector     |                | 29 |

| 3.10 | Example: Network ststus befor an input requ   | est            | 36 |

| 3.1  | Example: Network status after the request has | been processed | 36 |

| 4.1  | 4x4 Reconfiguarble Processor Marix            |                | 41 |

| 4.2  | 3- D view of the local bus connection .       |                | 46 |

| 4.3  | Establishing local bus connection             |                | 47 |

| 4.4  | Unary sum of a binary sequence                |                | 49 |

| 4.5  | Example: sorting 4 numbers on ORBS            |                | 56 |

| 5.1  | Optical Reconfigurable Processor Array        |                | 58 |

| Figi | ure                                | Page |

|------|------------------------------------|------|

| 5.2  | Local bus connection between ports | ·60  |

| 6.1  | Shifting Binary Sequence           | 70   |

| 6.2  | Unary PrefixSum                    | 71   |

| 6.3  | Unary subtraction                  | 72   |

-

•

## THESIS ABSTRACT

NAME OF THE STUDENT: MAHMOOD HOSSAIN

TITLE OF THE STUDY : PARALLEL OPTICAL ARCHITECTURES FOR

SOME COMPARISON-BASED PROBLEMS

MAJOR FIELD : COMPUTER SCIENCE

DATE OF DEGREE : JANUARY, 1992

Parallel computing requires architectures that are radically different from the inherently sequential computer architectures of today. In addition to processor-level parallelism of parallel computation models, where many processors collectively and concurrently work on a given task, parallelism at the basic instruction-level within each individual processor, is equally sought. While the former objective is achievable through different parallel computation models i.e., SIMD, MIMD models, the latter is difficult to achieve in the electronic domain. Optics provides parallelism at the basic instruction-level due to its massive inherent parallelism, large space-bandwidth product, and cross-talk-free free-space connectivity.

In this study, attempts have been made to combine the field of *Parallel Computing* and *Optical Computing* to solve some comparison-based problems. Some parallel optical architectures along with an *Optical Vector Processor* and associated algorithms are developed to solve problems that are based on comparison. Optical implementation of Clos Nonblocking-Multicast-Switching Network and an O(1) network control algorithm have been developed. Optical Reconfigurable Bus System has been developed to solve unary-sorting problem in O(1) time. The class of Binary-Tree-Computations has been simulated on optical architectures along with algorithms for *Parallel Select* and *Parallel Quicksort* problems.

## MASTER OF SCIENCE DEGREE

KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

JANUARY, 1992

## خلاصة الرسالة

اسم الطالبي: محمود حسين

عنوان الدراسة: بناء ضوئى متوازي لبعض المسائل المعتمدة على المقارنة

التخصـــص: علوم الحاسب الآلي

تاريخ الدرجة: يناير (كانون الثاني) ١٩٩٢م

يتطلب تصميم الحسابات المتوازية هندسة بناء تختلف عن تلك المستخدمة في الحسابات المتوازية. فبالإضافة الى التوازي على مستوى المعالجات في نماذج الحسابات المتوازية حيث يعمل عدة معالجات في نفس الوقت لتنفيذ عمل معين فإن التوازي على مستوى الأوامر الأساسية مطلوب أيضا.

ومع أن التوازي على مستوى المعالجات يمكن الحصول عليها بستخدام نماذج عديدة منها SIMD و MIMD فإن التوازي على مستوى الأوامر الأساسية من الصعب الحصول عليها في مجال الالكترونيات.

أما في مجال الضوئيات فإن التوازي على مستوى الأوامر الأساسية يمكن الحصول عليه لأسباب عديدة منها خاصية التوازي في الضوء والمنتجات عريضة الموجة جدا وإمكانية الوصل العالية لعدم التأثير السلبى لتقاطع الضوء.

يقدم هذا البحث محاولة لجمع الحسابات المتوازية مع الحسابات الضوئية لمعالجة بعض المسائل المعتمدة على المقارنة. وقد تم اقتراح بناء ضوئي متوازي مع معالج ضوئي متعدد اضافة الى الخوارزميات التي تعالج بعض المسائل التي تعتمد على المقارنة. كما تم تطوير شبكة مفتاح متعدد الارسال دون توقف مع خوارزمية للتحكم بالشبكة بدرجة تعقيد مقدارها ١. وكذلك تم حل مسألة الترتيب بنفس درجة التعقيد وذلك بتطوير نظام ضوئي خاص. اضافة الى انه قد تم محاكاة الحسابات الشجرية الثنائية بخوارزميات الاختيار المتوازى والترتيب المتوازى.

درجة الماجستير في العلوم جامعة الملك فهد للبترول والمعادن الظهران - المملكة العربية السعودية كانون الثاني (يناير) ١٩٩٢م

## Chapter 1

## Introduction

## 1.1 Objective of the Study

Over the past four decades of computing history, dramatic increases in computing speed were achieved. As we went from relays to vacuum tubes to transistors and from small to medium to large and then to very large scale integration, we witnessed the geometric growth of computational speed and hence increasingly greater problem-solving capability. We would be happy if this progress continues. Unfortunately, this trend has its peak due to fundamental limits. The problem is not with the computational speed (switching speed to be more precise) but the communication limitations, namely, propagation delays, interconnection constraints associated with the resistance and capacitance of electronic interconnects, inadequate space-bandwidth product and finally, undesired interactions between electrons due to miniaturization of components beyond the lowest physical limit. State-of-the-art computing machines, from stand-alone desk-top PC to the largest supercomputer, are basically similar in their computation models: their hardware is based upon processing units fabricated on VLSI chips, that operate on instructions and data kept in memory. They run sequential programs that specify exactly what to do at each step. Broadly speaking, these are the Von Neumann machines. The high speed gain in electronic switching does not cope with the ever-increasing demand for computational power because of the drag caused by the low communication capability. This is the so-called Von Neumann bottle-neck. This limitation of conventional computers has initiated research efforts in two different directions, one in the field of Parallel and Distributed Computing and the other in the newly emerged field of Optical Computing.

In Parallel and Distributed computation—models, several uniprocessors, random access machines (RAM) work independently either with proper synchronization among themselves or without any synchronization at all. Given a problem to be solved, it is broken into a number of subproblems.

All of these subproblems are now solved simultaneously, each on a different processor. The results of all the subproblems are then combined to produce the solution to the original problem. This is a radical departure from Von Neumann-machine-model, namely, the sequential uniprocessor machine. The declining cost of VLSI chips has made it possible to assemble machines with millions of processors. The inter-processor communication is handled through a sophisticated, well-defined interconnection network. Much work has been done in developing efficient interconnection networks[SEIG 91]. Though we might get large speed-up in terms of time needed to solve a particular problem on a parallel computational model, we are still faced with the problem that inter-processor communication lags behind the computational speed of individual electronic processor.

In their search for universal parallel computer models, researchers explored a new field called Optical Computing. The field of Optical Computing is quite broad and includes different ideas and possibilities. Essentially, computation and communication using optics for information processing is termed as Optical Computing[FEIT 88]. Optics has a proven superiority to electronics when compared in terms of communication performance. While it appears feasible to improve switching speed by several order of magnitude (to perhaps 10 ps [ANDO 89]), it does not appear possible to make an electronic interconnect which can support such short pulses through a long distance but the shortest gate-to-gate paths. It is, however, possible to transmit a 10 ps optical pulse through an optical fiber or free-space with minimal distortion ANDO 89]. Commercially available optical fibers have bandwidths in excess of 1000 Gb/s, which remains unused due to the lack of fast tapping devices. Again, the number of interconnects required by an electronic VLSI chip scales in proportion to the chip area. The perimeter grows only as the square root of the area. As a chip gets larger, the space available for each interconnect on the perimeter becomes restricted. This problem can be overcome by multiplexing signals on a small number of interconnects. This, however, incurs a time penalty. An alternative solution is to make interconnections within the whole chip area. This is not as possible in electronics as in optics.

Following is a list of points that make optics superior to electronics:

## · Direct Image Processing.

Certain image processing functions can be carried out by specific optical systems directly on the image, with no need for sampling, quantization and such. These optical systems operate much faster and with better resolution than their electronic counterparts.

## · Massive Inherent Parallelism and Connectivity...

The problems restricting the ultimate speed-up of the conventional computers do not arise from the inadequate speed of the basic elements. Rather, interconnection is the limiting factor. Optical communication allows new ideas unheard of before: millions of data channels may operate in parallel, each with a bandwidth much greater than that of any electronic link.

## Speed.

The possibilities of special purpose systems and massive parallelism give rise to high speed in data processing. This is important in modern applications like oil exploration, satellite image processing, weather forecasting, biomedical analysis, modelling fusion reactors, cryptanalysis, solution of very large systems of differential equations arising from numerical simulations in disciplines as diverse as seismology, aerodynamics, atomic, nuclear and plasma physics. No computer exists today that can deliver the processing speeds required by these applications( in the order of 10<sup>13</sup> operations per second [AKL 89]). Even the so-called supercomputers peak at a few billion operations per second.

## Immunity to EMI.

The electrons circulating in a VLSI chip are susceptible to electromagnetic interference(EMI). In electrically noisy environments electronic VLSI chips may malfunction. Optics is completely free from EMI.

## • Free Space Connectivity.

Since light beams do not interact with each other, an optical computer can exploit this feature to have free space interconnections between its components.

The above list is quite impressive and calls for extensive research efforts towards *Optical Computing*, where computation and communication coexists. The marriage between the fields of *Parallel Computing* and *Optical Computing* appears to provide a desired and suitable alternative to the Von Neumann model of sequential computation. In this study, issues related to optical computation and communication on a parallel computation model to solve some basic comparison problems are addressed.

## 1.2 Thesis Organization

The results of this thesis are distributed into different chapters starting from Chapter 2 to Chapter 7. Chapter 2 reviews the related background work both in *Optical Computing* and *Parallel Computation Models* to solve some of the representative comparison-related problems that includes general interconnection network to sorting network.

Chapter 3 presents an Optical implementation of Clos nonblocking-broadcast-network. An O(1) control algorithm on a proposed Optical Parallel architecture is proposed. The optical nonnumeric processing unit,  $Optical\ Vector\ Processor(OVP)$  with some primitive optical operations on binary vectors is also presented.

Chapter 4 proposes an Optical Reconfigurable Processor Matrix architecture to sort n numbers in constant time i.e., in O(1) time.

In Chapter 5, Arbitrary *Binary-tree-computations* are simulated on Optical Reconfigurable Processor Array architecture.

Chapter 6 presents parallel algorithms to solve *Parallel Selection Problem* and *Parallel Quicksort* on an Optical Reconfigurable Processor Array.

Finally, in Chapter 7 conclusion and recommendations for future work are presented.

## Chapter 2

## **Background Work**

## 2.1. Optical Computing

Optical computers are based on phenomena related to optics and light. The ancient history of Optical computing is linked to a large extent, to that of radar systems [LEIT 77]. The need to process vast amounts of data supplied by radars used in mapping was the motivating force behind early optical signal processing research efforts. Optical Computing received a great push from the invention of the LASER in 1960. The characteristics of this light source allowed numerous new operations to be realized by optical means. These operations were analog in nature, and are best described by the term "signal processing". Unlike electronic signal processing systems, which have one (temporal) degree of freedom, typical optical processors have two (temporal and spatial) degrees of freedom; the data is a 2-D image. One of the basic operations that can be performed on images in laser light is the Fourier Transform. Numerous applications grew out of this ability.

During the time when conventional electronic computers grew tremendously in speed, power and, in miniaturization, sporadic efforts were also made to realize digital logic by optical means. These efforts did not succeed mainly for two reasons. One was the success of Von Neumann computers. They answered the world's computational needs. They are well-developed both theoretically and practically. They gave results that were accurate to any desired degree. When this is compared to the basically analog optical systems with their new and immature technology and potentially problematic operations, it is clear why research in optical computing took a back seat. The second reason was the absence of substantial research projects to find an alternative to sequential machines. Electronic computers received a great push from the invention of transistors and then the development of integrated circuits. The need for any alternative and/or radical change to the electronic computing has not been too great until recently. The so-called Von Neumann bottleneck of sequential computation resumes the interests in Optical Computing in search for true

## parallel computers.

There are two distinct trends in optical computing: that of special purpose analog systems and that of general purpose digital optical computers. Special purpose analog optical computers are again divided into two classes: those that deal with image and signal processing, and those that deal with numerical processing. In image and signal processing analog systems, we are talking about optical systems that accept one beam of light as input, manipulate it, and finally produce an output beam of light. These systems exploit various physical phenomena from the field of optics, such as the ability to perform 2-D Fourier Transforms. In contrast, numerical processors do not manipulate beams of light, rather they deal with arrays of numbers, represented by multiple points of light.

General purpose digital optical computers have been a major research topic recently. They are usually based on nonlinear optical effects. The invention of first nonlinear electrical device (where electron controls electrons) back in 1907, namely *vacuum tube*, made it possible to implement logic circuits. Logic circuits are the backbone of conventional digital electronic computers. Similarly, the invention of optical nonlinearity (where light controls light) and nonlinear devices [FEIT 88] promises the opportunity to realize optical logic circuits. This led research towards realizing digital optical computers [JORD 91]. These research efforts devote to develop and realize optical devices that mimic their existing electronic counterparts: logic gates, memory elements( optical flip-flop), integrated optical circuits [FEIT 88]. The goal is to create a general purpose digital computer (either hybrid i.e., optoelectronic or all-optical) that will be comparable to electronic ones, but better in some significant way, e.g., it might be faster.

Optical computers use light to convey information. Light is an electromagnetic wave that is characterized by its frequency, wavelength, amplitude, phase, polarizatrion, and degree of coherence. Light sources used in optical computers are semiconductor LEDs and LASERs. Information is imposed on a light beam by modulation of its cross-section; this is done by spatial light modulators (SLM, a new addition to optical devices that are used in information processing) [FEIT 88]. Light beams are manipulated by various optical elements, e.g., beam-splitters,

diffraction gratings, lenses, polarizers, holograms and holographic optical elements. The intensity of a light beam is detected by photodiode detector with various threshold levels [FEIT 88]. Feitelson [FEIT 88] has done an excellent task of surveying the various optical devices, and phenomena, their capabilities and limitations and in indicating the role they can play in computing from the point of view of Computer Science. In optical computing, two types of memory are discussed. One is more or less equivalent to primary memory, and consists of one-bit-store elements, the other is mass storage, which is implemented by optical disks or by holographic storage systems. This type of memory promises very high capacity and storage density on line. Holographic memory consists of a set of carrier and position multiplexed phase transmission holograms recorded on a silver halide emulsion. It is used to store a number of patterns in the same small emulsion area. The recordings are made with plane wave object and reference beams.

## 2.2. Optical Architectures

Broadly speaking, the architecture of conventional electronic computers supports the Von Neumann model: a CPU manipulates the contents of the memory by executing a sequential program; for each instruction data is loaded from the memory to the CPU's internal registers, and the computed result is stored back in the memory. The technology used to implement these computers is based on planar integrated circuits. A possible approach to choosing an architecture for optical computers is to simply copy the very successful electronic precedence, replacing electronic logic elements by optical ones, and interconnection wires by optical fibers or optical waveguides [WEST 87], [JORD 91]. The goal of these research efforts is centered around the design and construction of an optical version of general purpose, stored program, digital computer. The design of Digital Optical Computer (DOC) at Boulder [JORD 91], a prototype, is bit-serial to minimize the number of active devices. This bit-serial design uses bandwidth or time domain capacity to achieve processing power. Optical fibers form all memory and interconnection. Fiber delay lines or loops are used as storage. Due to time division multiplexing and due to the use of fiber delay loops as memory, the terabits per second information capacity of fiber channel is not utilized fully. This approach is merely a transfer of conventional electronic computer model to optics without any major change in the underlying model. However, this approach requires each optical element to be highly superior to the functionally equivalent electronic counterparts in order to justify the transition to optics. Specifically the optical elements should be faster by at least two orders of magnitude [RHOD 86]. As it is not clear whether such expectations are practical, many researchers feel that a radically different architecture should be pursued.

The architecture of a computer should be related to the capabilities of the underlying technology. In the case of optical computers, the possibility of dense interconnections coupled with interference free propagation, implies that parallel architectures might be fitting. A beam of light may contain millions of resolvable pixels, each of which may be used as a distinct data channel. Two primary factors limit the density of optical interconnects. They are the resolvable spot size for free-space interconnects and the required size of a waveguide. Single mode fibers with core diameter of I µm are commonly available and it is possible to fabricate optical guides on the order of I µm as is routinely done in integrated optics. Free-space propagation is fundamentally limited by the diffraction-limited spot-size of image systems. Even with this restriction, however, it is possible theoretically to pack optical waveguides(fibers) or free-space channels on the order of 10,000 to 50,000 per mm<sup>2</sup> [HAUG 86]. As the beam traverses an optical system, various operations are performed on all the points in parallel. Therefore the parallel architecture that seems most suitable to an optical computer is that of an SIMD( Single Instruction-stream Multiple Datastream) machine. The basic data element in this architecture is not a byte or word but rather a vector or matrix of pixels or binary digits. This brings parallelism at the component level (within a single optical processor) as well as processor level (within an interconnected multiprocessors). Processors are connected through a generalized optical interconnection network (capable of broadcast facility). Intra-processor and Inter-processors interconnections by optical means provide the following lucrative advantages:

#### Large Bandwidth and Space-Bandwidth Product

The use of light as a carrier of information is a step in use of carrier of higher and higher frequencies. The need for carriers with higher frequencies stems from the need for larger bandwidth.

If the carrier frequency is of the order of  $10^{14}$  cps(cycles per second), a bandwidth near  $10^{13}$  cps should be available. This implies possible data rate in access of  $10^{12}$  bps [FEIT 88]. Such rates are 3 orders of magnitude faster than the fastest data rate of today. Communication at a data rate of  $10^{12}$  bps means that the modulation of the carrier changes  $10^{12}$  times every second. Electronic switching devices fall at least 2 orders of magnitude short of the objectives. In optics, large number of independent channels can propagate together in parallel, resulting in large space-bandwidth product.

## · High Speed Propagation

Electrical signals propagate two orders of magnitude slower than light [WILK 83]. The reason is that the electronic conductor has a capacitance that has to be charged—it can be described as a pipe that has to be filled in before anything arrives at the other end. Therefore, the propagation time increases with the length of the connection and also with the fan-out. With light these problems do not arise; it always propagates at the speed of light (scaled down by the refractive index of the medium).

#### • Non Interference Propagation

Electronic interconnects must be laid some distance apart, so as to prevent cross-talk. Electrons in a metallic conductor also interact with electromagnetic radiation: conductor simply serves as an antenna. Thus electronic interconnects are susceptible to electromagnetic interference. Photons on the other hand, do not interact with each other or with other radiation. This is a major asset in optical interconnects.

## · Density and Parallelism

As light beams do not interact, optical interconnections need not be guided at all within the vicinity of optical processor or integrated optical chip. Light beams can propagate freely in space, with

different communication channels crossing each other. Pin lay-out problem encountered in VLSI technology is reduced. The interconnection density in optics is much higher [HAUG 86].

#### Dynamic Reconfigurability

Optical interconnection are often controlled by holograms and mask patterns. If these elements are implemented by spatial light modulators(SLMs) or dynamic grating pattern, they can be dynamically reconfigured. Thus the interconnection mapping patterns are modified in real time(within ms) [SCHU 87], [SAWC 86].

## Optical Interconnection Media

#### Optical Fibers

An optical fiber is a conductor or waveguide for light. The propagation of light in optical fibers is explained by the phenomenon of *Total Internal Reflection* [KAPA 60]. Fiber optics are already being used in telecommunication with great success. It has been suggested that they may be used at a smaller scale, for connections between boards and chips [GOOD 84]. A Typical optical fiber has information capacity in excess of *1000* GHz.

#### Free Space Interconnections

Within the confines of an optical computer, there is actually no reason to conduct the light in optical fibers; as the distances are short. As the light beams do not interact with each other, there is no danger of cross-talk. The advantages of the so-called free-space interconnection scheme stem from the fact that the third dimension of space is utilized, instead of confining the interconnection topology to a 2-D surface. This alleviates many topological difficulties. The main issue in free-space interconnection scheme is how to direct many beams of light and focus them on the right ports. The technique that has been used is through holographic optical elements.

A hologram is a mechanism that can be used to modify and redirect a light beam that is incident upon it. Because of this capability, a hologram or collection of holograms can be thought of as photonic switches. A simple hologram, similar to a diffraction grating, can deflect its light in any desired direction (depending on the orientation of the grating pattern imposed on it) and focus it on a detector. In general, we have a set of sources, a set of detectors and an arbitrary mapping pattern on hologram. In order to implement this mapping, the hologram is divided into subholograms one for each source-detector mapping [SCOT 88], [FEIT 88], [KOST 87]. The interconnection pattern on the hologram can be dynamically reconfigured resulting in dynamic reconfiguration of the interconnection [SCHU 87].

For the realization of the holographic interconnection scheme it is important to know what spatial resolution can be achieved directing incoming light beams to different distinct spots. With the Reyleigh criteria,-it can be shown [SCHU 87] that the minimum resolvable distance h between two spots, which can be addressed by a hologram of size  $L \times L$  is given by

$$h = \lambda S / L$$

where  $\lambda$  denotes the wavelength, S is the distance of the surface from the hologram where the spot is focused. For an optical interconnect using laser source with  $\lambda = 1.3 \ \mu m$  and a hologram aperture  $L \times L = 1 \times 1 \ \text{mm}$  and a distance of 20 mm of the hologram from the detectors, the minimum separation h between two adjacent detectors is:

$$h = 1.3 \times 20 / 1 = 26 \,\mu m$$

.

If  $h = 50 \ \mu m$ , an area of  $l \ mm^2$  enables one to carry  $20 \times 20$  detectors. This packing density of detectors is sufficient in most cases [SCHU 87].

### 2.3. Inter-Processor Interconnection

A SIMD model of multiprocessor computer model best suits the potential and the inherent capabilities provided by optics. In electronic multiprocessor/multicomputer environment, interprocessor communication is handled by different interconnection networks. They range from a common bus on one side of the spectrum to a crossbar network on the other extreme. In the middle lies the set of multi-stage interconnection networks: Clos, Shuffle-Exchange, Omega, Benes, Hypercube, Banyan and so on. Much work has been done on multistage interconnection networks [SEIG 91] with different objectives. Optical multiprocessor computer can adapt any one of these well-defined interconnection networks suited to its underlying capability and characteristics. Optical implementation of some of these interconnection networks have been proposed using optical elements; such as, Crossbar network [FRAC 90], Perfect Shuffle [LOHM 86], [HEIN 88], [BIAN 91], and Banyan network [JAHN 90].

## • Bus

A bus is a common transmission medium, used by the communicating entities. At each moment, at most one user is transmitting a message on the bus, while all others listen. The optical implementation of a bus is simply an optical fiber link, running through all the communicating processors. Different modules access the information flowing in the fiber by means of special couplers. These couplers are curved pieces of fiber that touch the main fiber; their operation is similar to that of directional couplers [MILT 76].

#### Crossbar Switch

The Crossbar is a general switching device that can connect any one of N inputs to any one of N outputs (I to I connection). A generalized crossbar allows I to many inputs to outputs mapping (broadcasting). A generalized crossbar is the most desirable type of interconnection to be used in optical parallel computers because it is rearrangeable (any permutation of input to output

ports can be realized) and *nonblocking* (connection between input and output ports can be established independently without disturbing the other connections). In optics, a matrix of holographic mask pattern realizes a crossbar function where connections can be controlled dynamically in real time [ SCHU 87], [FRAC 90], [McAU 86], [SAWC 86].

## Clos Multistage Interconnection Network[ Clos 74]

Clos multistage interconnection network is based on a number of interconnected crossbar switches of smaller sizes as basic building blocks spread over different stages. This network has great potential for parallel optical multiprocessor architecture. Clos multistage interconnection network with broadcast capability, has been studied extensively [YANG 90].

#### 2.4 Conclusion

The success of optical computing depends on how efficiently-the inherent parallelism and enormous communication capabilities of optics is explored in new computer architectures. A simple transfer to optics from electronics without a radical change in the underlying computational model, may fail to justify the transition of technology. Optics demands parallel architectures to match with its capabilities. To be more specific, optical computer architecture is expected to be SIMD ( if not MIMD) machine and the basic optical processing unit must exploit the natural parallelism provided by optics. The result is two-fold gain in parallelism — parallelism at the processor level and parallelism at the basic instruction level.

## Chapter 3

## Optical Realization of CLOS Nonblocking-Broadcast-Switching Network with constant time Network Control Algorithm

#### 3.1 Introduction

A generalised and efficient switching network is an absolute necessity for the success of parallel computing and processing. Switching networks provide a set of interconnection or mapping between two sets of nodes; the input and the output ports. For N input ports and M output ports there are  $N^M$  well-defined mappings from inputs to outputs. The term well-defined means that each output is defined in terms of one and only one input port. A network performing all  $N^M$  such mappings is called Generalised Connection Network (GCN). If we limit the mapping function only to the class of one-to-one, then N! such mappings are well defined. This is the set of all possible permutations over the input set which does not include the broadcast assignments. A network with broadcast capability from any input port to a set of output ports is called Broadcast Network.

An obvious and easy way of implementing arbitrary collections of broadcast requests is with a complete crossbar network. A crossbar is the most desirable type of interconnection topology to connect processors with processors and/or with memories because it is rearrangeable (any one of N! permutations of input ports to output ports can be realized) and nonblocking (connections between input and output ports can be established independently without disturbing the existing connections). Unfortunately, as the number of input ports, N grows, the number of crosspoints also grows as  $N^2$ , making it uneconomical to realize large systems.

Multistage networks provide a cheaper alternative to the complete crossbar switch. They are based on a number of interconnected crossbar switches of smaller sizes as basic building blocks, spread over different stages. A 3-stage Clos network is a good example. The trade-off here is between cost and complexity of control. Much work has been done along the line of multistage interconnection networks with different objectives [SEIG 91]. Recently, Yang and Masson [YANG90] proposed a design framework for nonblocking broadcast switching networks. Their work was based on Clos network topology. They analysed Clos network's characteristics mathematically and found out a nonblocking condition on the number of middle stage switches to realize arbitrary broadcast requests.

We adapt and extend the work of Yang and Masson to the domain of optics. Since optics provide natural parallelism, higher space-bandwidth product and immunity from mutual interference, we exploit these attributes of free space optics to implement the multistage nonblocking broadcast network. Further we propose a constant time algorithm for the network control, in contrast to the linear time algorithm proposed in [YANG 90].

## 3.2 Multistage Interconnection Network with Broadcast Capability

Multistage switching networks, which consist of multiple cascaded stages of switching elements, are networks with a dynamic topology. They differ in the interconnection pattern between stages, the type and operation of individual switching elements, and the control scheme for setting up the switching elements. Some of them realize all the possible permutations of input sets whereas some do not [LAXM 90]. Example of such networks are: Clos network, Benes network, Baseline network, Omega network, Shuffle Exchange network, Banyan network [SEIG91] etc. Clos 3-stage network is based on crossbar switches of smaller sizes. Our interest lies in the Clos network topology with additional broadcast capability.

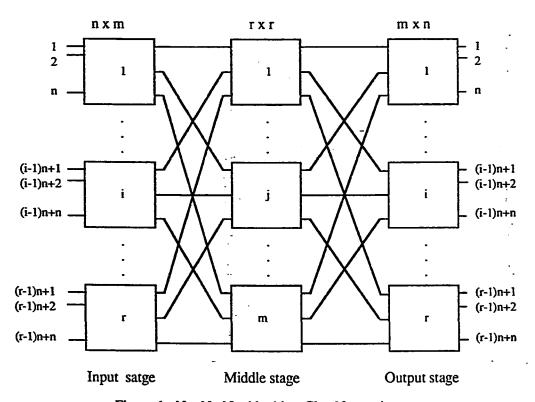

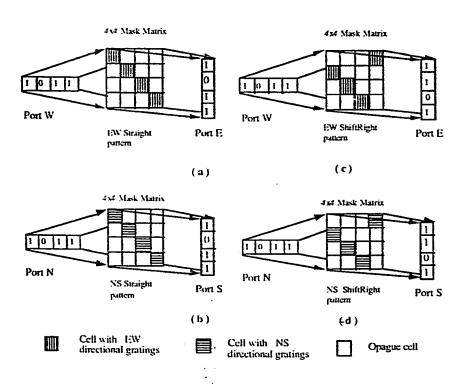

Figure 1: N x N Nonblocking Clos Network

In an NxM Multistage Interconnection Network with Broadcast capability (MINB), N input ports are mapped onto M output ports in a one-to-many broadcast fashion. The switching elements are grouped into smaller modules called SWITCH MODULES (SM). Each SM is of the size nxm; n< N, m< M and provides broadcast connections for n input ports to m output ports, that is, any input can request connections to any subset of available outputs. Switch modules are the basic building blocks. SMs are grouped into different stages. Each SM in stage i has dedicated links to all SMs of stage (i+1). An  $N_1xN_2$  3-stage MINB has  $r_1$  SMs of size  $n_1xm$  in the input stage, m SMs of size  $r_1xr_2$  in the middle stage and  $r_2$  SMs of size  $mxn_2$  in the output stage where  $N_1 = r_1xn_1$ ,  $N_2 = r_2xn_2$ . Without loss of generality and for notational convenience we assume  $N_1=N_2$  i.e., number of input and output ports to be equal. It turns out that if we choose  $n_1=n_2$  then  $r_1=r_2$ .

In a Nonblocking broadcast network any broadcast request from an input port to a set of free output ports can be realized without any disturbance to other existing connections.

#### 3.3 Previous Results

Much work has been done on multistage interconnection networks [SEIG 91]. To realize a connection path between inputs and outputs in a multistage interconnection network a network controller is needed. A network controller executes a control algorithm that sets the required switches in various stages to set up the requested path. Until recently, the best control algorithm that could be achieved was of O(NlogN). Yang and Masson[YANG90] gave a linear time O(N) algorithm. They have found a lower bound on the number of middle stage switches to ensure nonblocking broadcast connection from any arbitrary input to a set of output ports. According to Clos, the nonblocking condition for permutation assignment requires that  $m \ge 2n - 1$ . Although it works fine for point-to-point connections, it does not necessarily satisfy all broadcast assignment. Masson [MASS71,72] first proposed a design for strictly nonblocking and rearrangeable multistage switching network for broadcast assignment. For broadcast assignment in a 3-stage network it was shown that if m > n(r+1) - 1, the network is strictly nonblocking, and if  $m \ge nr$ , the network is rearrangeable.

The inherent characteristics of Multistage Nonblocking Broadcast Networks have been studied [YANG 90]. For a 3-stage Clos broadcast network to be nonblocking it has been shown that,

$$m > \text{Min } \{ (n-1)(x+r) \} \text{ for } 1 \le x \le \min \{ n-1, r \}$$

(3.1)

where m = number of middle switch modules (SM)

- r = number of output switch modules (SM)

- = maximum fanout for each input request.

- x = number of available middle stage switches for an input connection request to be satisfied for certrainity.  $(x \ge 1)$

Given this nonblocking condition on m, a linear time O(N) algorithm has been proposed to satisfy any input broadcast request. We will be using this nonblocking condition on m (3.1) to implement a reconfigurable Nonblocking Optical Broadcast Network. Our control algorithm given in section 5.2 takes O(1) time.

## 3.4 Proposed Optical Multistage Nonblocking Broadcast network

In this section, we explain the design of the proposed optical nonblocking broadcast network from the basic switch modules to the dedicated inter stage links.

#### 3.4.1 Switch Module (SM)

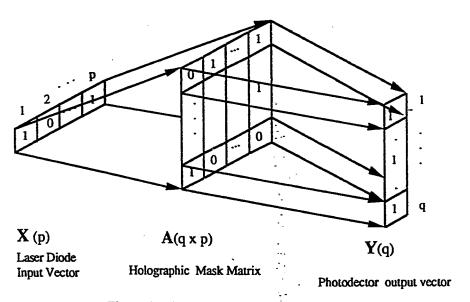

Each SM of size nxm is the basic building block. It is realized as an optical crossbar switch. Essentially it performs a vector-matrix multiplication as: Y = AX

Figure 2: Switch Module Design

where X = Bit-vector of size Ixp representing the input lines,

Y = Bit-vector of size lxq representing the output lines,

and A = Interconnection binary mask matrix of size qxp. Its entries are either 0' s or 1' s. An entry of 1 in row i and column j of A means input j is connected to output i.

Schulze [SCHU87] has proposed an optical crossbar switch where the connection can be controlled dynamically. The input vector X is a laser diode array and the output vector Y is an array of photodetectors. The interconnection mask matrix A is a matrix of phase holograms. Its interference pattern can be changed dynamically using optical control. He has shown that to accomplish such holographic switching technique, dynamically changeable holographic phase gratings are imposed onto very high resolution spatial light modulators (SLMs). The interference patterns necessary to build the holograms can be obtained by an optical interference process. For notational convenience we assume that each entry of I in matrix A represents a closed switch and that of a zero an open switch. In addition, each entry of I in vector X represent a laser diode source or optical fibre port.

To realize broadcast connection, each column of A can have more than one I (closed switch). The matrix A is phase grated such that

If

$$A(i,j)=l$$

for  $1 \le i \le n$ ;  $1 \le j \le m$

then  $X(j)$  is connected to  $Y(i)$  for all  $i, l \le i \le m$ .  $(n \le m)$

We denote each SM in different stage as  $\alpha_{ij}(p,q)$

where i = stage number and

j = switch position within the stage

$p \times q = \text{size of the switch module}$

The proposed network has 3 stages; input, middle and output stage (Figure 1).

#### Input Stage:

There are r SM's of size  $n \times m$ . Each one is denoted as:  $\alpha_{lk}(n \times m)$ ;  $l \le k \le r$ . We can write connection between its input and output ports as:

$$X_{Ik}(Ixn)A_{Ik}(mxn) = Y_{Ik}(Ixm)$$

equivalently,

$$X_{lk}A_{lk} = Y_{lk}$$

;  $l \le k \le r$ .

#### Middle Stage:

This stage consists of m SM's of size rxr. They are denoted as:  $\alpha_{2k}(rxr)$ ;  $1 \le k \le m$ We can write connection between its input and output ports as:

$$X_{2k}(lxr)A_{2k}(rxr) = Y_{2k}(lxr)$$

equivalently,

$$X_{2k}A_{2k} = Y_{2k} ; l \le k \le m.$$

#### **Output Stage:**

This stage has again r SM's of size mxn. They are denoted as:  $\alpha_{3k}(nxm)$ ;  $1 \le k \le r$ We can write connection between its input and output ports as:

$$X_{3k}(1\times m)A_{3k}(n\times m) = Y_{3k}(1\times n)$$

equivalently,

$$X_{3k}A_{3k} = Y_{3k} \quad l \le k \le r.$$

All X and Y vectors are holographic memory. They store the logical contents of the laser diode input vectors and photodetector output vectors.

# 3.4.2 Optical Fibre Inter-stage Links:

Switch Modules (SMs) in stage 1 and 2 and those of stages 2 and 3 are statically connected by optical fibre links according to the Clos network.

Links between Stage 1 to stage 2 are denoted as:

$$\begin{aligned} &Y_{lk}(j) -----> X_{2l}(i) \\ &l \leq k \leq r \qquad l \leq l \leq m \\ &l \leq j \leq m \qquad l \leq i \leq r \end{aligned}$$

Links between Stage 2 to stage 3 are denoted as:

$$Y_{2l}(i)$$

-----> $X_{3k}(j)$

$1 \le l \le m$   $1 \le k \le r$

$1 \le i \le r$   $1 \le j \le m$

#### 3.5 Network Controller

To exploit the inherent parallelism of free space optics we propose a parallel architecture / algorithm for the control circuitry. The network controller is analogous to a SIMD machine model. It has r identical Optical Vector Processors (OVP) sharing a common memory. It has a control circuitry to execute the stored network control program to activate different OVPs. Each OVP performs some primitive nonnumeric vector operations using all optical elements. Processing is done by OVPs concurrently. Now we define these primitive hardware operations. All vectors are holographic memory elements. Each element has two phase gratings reflecting incoming light beams in two different directions. We call them grating1 and grating0 respectively. Grating1 represents binary 1 and grating0 represents binary 0. We first realize a number of primitive vector operations using all optical elements and use them in the network control algorithm.

#### 3.5.1 Optical Vector Processor Primitive Operations

Each OVP is capable of performing some nonnumeric processing on binary vectors using all optical elements. The following operations are defined. Even though each operation is illustrated by a simple example, its generality is well understood.

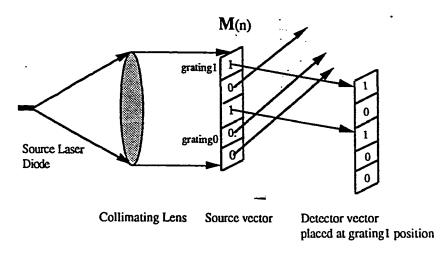

#### Vector Copy: COPY(M)

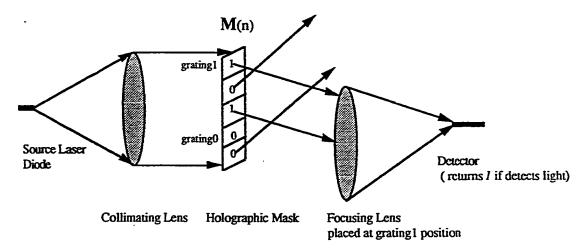

Figure 3: Copy of vector M

The COPY instruction makes a copy of a binary vector. The hardware realization is done by a laser light source, a collimating lens, the source vector, a detector vector and the destination vector. In one clock cycle the source is copied to the destination vector. The detector vector is aligned such that it collects all reflected lights from grating 1 of source vector. This is illustrated in figure 3.As an example consider a vector  $M = \langle 1,0,0,1,0,1 \rangle$ . Since the values in positions 2.3.5 are zero they would be reflected away from those with logical value of 1. The result vector,  $M_{new} = \text{COPY}(M) = \langle 1,0,0,1,0,1 \rangle$ .

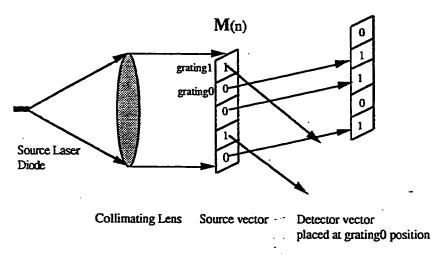

#### Vector Compliment : INV(M)

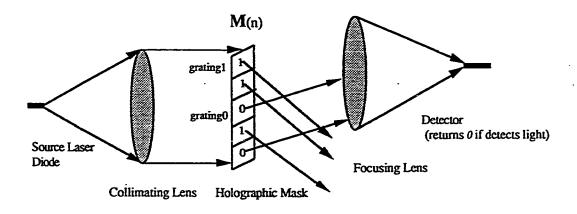

Figure 4: Compliment of vector M

The INV instruction takes the compliment of a binary vector. Its hardware realization is the same as the COPY except that the detector vector is aligned the other way so that it collects the light beams coming from elements of source vector with grating0. Thus bitwise compliment of a vector can be achieved in one clock cycle of the network controller. Let us take same vector  $M = \langle 1,0,0,1,0,1 \rangle$ . Here light reflected from position 2,3 and 5 are collected at the corresponding positions of the detector array and are set to logical I's and the rest of the positions are set to logical 0's. As a result we have,  $M_{new} = INV(M) = \langle 0,1,1,0,1,0 \rangle$ . The optical setup for this operation is depicted in Figure 4.

#### Intra Vector Bitwise UNION: BITUNION(M)

Figure 5: Bitwise Union Of M

BITUNION instruction takes a vector as input and finds the bitwise union of that vector in one clock cycle. Its hardware realization includes a laser source, two collimating lens and a photodetector. All the light beams coming from grating 1 elements of source vectors are focused at the detector point. If any one of the entries of the source vector is logical I i.e. graing I then the detector will detect a logical I. For the vector  $M = \langle 1,0,0,1,0,1 \rangle$ , BITUNION(M = I because M has at least one element with logical value of I. It is shown in Figure 5.

#### Intra Vector Bitwise AND: BITAND(M)

BITAND instruction takes a vector as input and returns the bitwise ANDing of that vector in one clock cycle. This unary operator can be realized using a laser source, two collimating lens and a detector. Unlike BITUNION this time the detector is placed such that it can detect the beams coming from grating0 of the source vector. If any one entry of the source vector is 0 i.e. grating0 then the detector detects it and takes its compliment as the output of the operation. This is shown in Figure 6. Consider the vector  $M = \langle 1,0,0,1,0,1 \rangle$ . Light reflected from positions 2,3,5 are focused at the detector and the result is set to logical value 0, that is, BITAND(M) = 0. If all the

elements of M are logical l's then all of them will be reflected away from the detector and the result is set to logical l, i.e.,  $M = \langle 1, 1, 1, 1, 1, 1 \rangle$  then BITAND(M) = l.

Figure 6: Bitwise ANDing of M

Vector Union: UNION(X,Y)

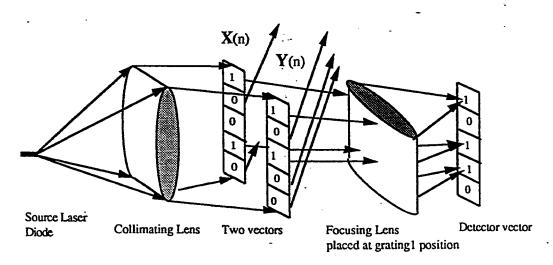

Figure 7: Union Of vectors X, Y

UNION instruction takes two/more vectors of equal length and returns their union. Its realization is the same as BITUNION except that a detector vector is used instead of a single detector and a cylindrical focusing lens or lenslet array is used instead of a single focusing lens. Figure 7 shows

the optical setup. Let us consider two vectors:  $A = \langle 1,0,0,1,0,0 \rangle$  and  $B = \langle 0,1,0,1,1,0 \rangle$ . Now  $C = UNION(A, B) = \langle 1,1,0,1,1,0 \rangle$

Vector Intersection: INTERSECTION(A, B)

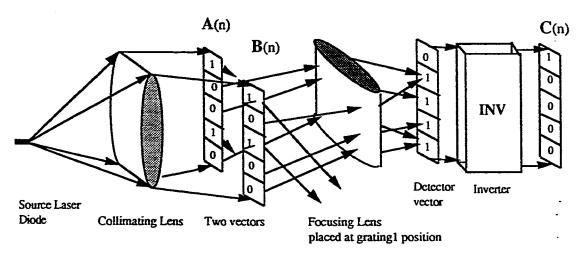

Figure 8: Intersection of vectors A, B

INTERSECTION instruction performs the binary AND operation of the corresponding bits of two vectors of equal length. Also its realization is the same as that of BITAND except that the detector is replaced by a detector vector and the focusing lens is replaced by a cylindrical lens or a lenslet array. The detector vector is then inverted by INV circuitry. So the INTERSECTION operation takes twice the time of INV. For example,  $A = \langle 1,0,0,1,0,0 \rangle$  and  $B = \langle 0,1,0,1,1,0 \rangle$ . The detector array detects logical value  $\langle 1,1,1,0,1,1 \rangle$ . This vector then gets inverted.  $C = INTERSECTION(A, B) = \langle 0,0,0,1,0,0 \rangle$ . The optical set up is given in Figure 8.

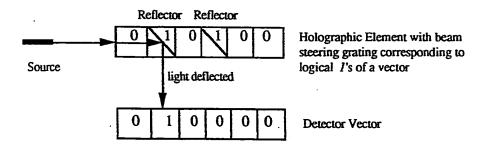

#### Masking Out All But The Leftmost 1: KEEPLEFTMOST(M)

To mask out all but the left most I of a vector, we use the operation KEEPLEFTMOST. Its optical implementation involves the holographic beam steering element with reflective type of real time holograms. The operand vector is written on a holographic mask element with O as transparent

Figure 9: Masking out trailing I's from a vector

#### 3.5.2 Control Algorithm

Given the nonblocking condition on the number of middle stage switches (m), our algorithm always satisfies a valid input broadcast request. If a network input port requests broadcast connection to more than one output port on the same output Switch Module (SM) then it only needs a link to that output SM. Connections to other ports within that particular SM could be broadcasted locally. So input broadcast request is expressed as a vector of output SMs.

Preliminaries for the algorithm:

-- Input broadcast request is denoted as

$$I_i$$

,  $i$  in  $< 1, 2, 3, ...., r > =$  Input Switch Modules Set and

$$I_i = <\alpha_{3k}/_{k in \{1,2,...,r\}}>$$

= Output Switch Modules Set

We assume  $I_i$  is expressed in terms output SMs. We also assume the requested ports are grouped into r ordered vectors of size n each. For example, an input broadcast request from port j in the i th. input-stage SM to output ports 1,3,5,8 is expressed as <1,0,1,0,1,0,0,1,0> and the individual request vectors for each output SMs are:  $O_1 = <1,0,1>$ ,  $O_2 = <0,1,0>$  and  $O_3 = <0,1,0>$ .  $I_i = <1,1,1>$ . We express the input request in terms of output SMs by  $I_i$  and in terms of output ports by vectors  $O_3$ .

— Associated with each input stage SM is a vector of available middle switches to which a free link is available.

AVAIL

$$_i = \langle d_j |_{1 \le j \le m} \rangle$$

where  $d_j = l$  if  $Y_{li}(j) = 0$  or  $d_i = 0$  if  $Y_{li}(j) = l$

clearly,

$$AVAIL_{i} = INV(Y_{li})$$

$$1 \le i \le r$$

— Associated with each output switch module is a *candidate* middle switch vector to which free links are available from that output SM.

CANDIDATE

$$_k = \langle a_j |_{1 \le j \le m} \rangle$$

where  $a_j = 0$  if  $X_{3k}(j) = 1$  or  $a_j = 1$  if  $X_{3k}(j) = 0$

clearly,

$$CANDIDATE_{k} = INV(X_{3k})$$

$$1 \le \varepsilon$$

— A bit vector of size (r) is required for the algorithm to check the feasibility of realizing any input broadcast request. This vector is called *CHECK* and initialized to all one's. If any of its entries, is found to be zero at the end of computation then that particular request could not be satisfied. The following three conditions sould be checked before any input broadcast request could be realized.

- (1) All the requested output ports must be free.

- (2) There sould be at least one middle stage SM available for the input request.

- (3) To establish a path from input stage SM to each and every required output stage SM there should be at least one middle stage SM available.

Now we give our algorithm. Any arbitrary input port issues a broadcast request  $I_i$ . Some of the steps in our algorithm are executed in parallel by different OVPs. To indicate the processor index on which certain step is executed we use its index in paranthesis after the step. Processors having the same index and satisfying the condition on index associated with the step are allowed to execute the step in parallel.

For example:

for

$$(k \text{ in } \{1,2,....,r\})$$

do in parallel  $A_k := COPY(B_k)$ ;  $(k)$

means that  $OVP_1,OVP_2,...,OVP_r$  each duplicates its local vector B to local vector A.

#### **ALGORITHM**

```

Step 1.

1.1 AVAIL_i := INV(Y_{Ii}); (i)

1.2 { Check if there is at least one middle stage SM available }

if BITUNION(AVAIL; i = 0 then return (unsuccessful); (i)

1.3 { Check if all the requested output ports are free }

for (j \text{ in } \{1,2,\ldots,r\} \text{ and } I[j]=l) do in parallel

CHECK[j] := BITAND(UNION(INV(O_i), INV(Y_{3i}))); (j)

1.4 if BITAND (CHECK) = 0 then return (unsuccessful); (i)

Step 2.

for (j \text{ in } \{1,2,\ldots,r\} \text{ and } I[j]=1) do in parallel

CANDIDATE_i := INV(X_{3i}); (j)

Step 3.

{ Compute the sufficient number of middle stage SMs }

for (j \text{ in } \{1,2,\ldots,r\} \text{ and } I[j]=1) do in parallel

S_j := INTERSECTION(AVAIL, CANDIDATE_j); (j)

<u>Step 4.</u>

Check if there is at least one middle stage SM available for each and every

required output SM }

4.1 for (j \text{ in } \{1,2,\ldots,r\} \text{ and } I[j]=1) do in parallel

if BITUNION(S_i) = 0 then CHECK[j] := 0; (j)

4.2 if BITAND (CHECK) = 0 then return (unsuccessful); (i)

{ Compute the necessary number of middle stage SMs }

<u>Step 5.</u>

for (j \text{ in } \{1,2,\ldots,r\} \text{ and } I[j]=l) do in parallel

T_i := KEEPLEFTMOST(S_i); (j)

```

```

<u>Step 6.</u> R := Union(T_i ; j in \{1,2,...,r\} and I[j]=1);(i)

```

{ The vector R of size m contains the set of sufficient and necessary (one and only one middle stage SM for each required output SM) number of middle stage switches through which the input broadcast request can be satisfied. So R contains at most r Is since there are r output stage SMs. If R(k) = 1,  $1 \le k \le m$  then SM  $\alpha_{2k}$  is to be connected to input switch i.}

{ Setting the connections for input broadcast request and updating the network state }

Step 7. for  $(k \text{ in } \{1,2,\ldots,m\} \text{ and } R \{k\}=1)$  do in parallel

- 7.1  $CSET_k := INTERSECTION(INV(Y_{2k}), I_i); (k)$

- 7.2 { Copy the vector CSET to the column i of mask matrix  $A_{2k}$  } { This will realize the connection through the kth middle stage SM }  $A_{2k}[*,i] := COPY(CSET_k); (k)$

- 7.3  $Y_{2k} := UNION(Y_{2k}, CSET_k); (\cdot k)$

Step 8. for  $(j \text{ in } \{1,2,....,r\} \text{ and } I[j]=1)$  do in parallel  $X_{3j} := UNION(X_{3j},T_j),(j)$

Step 9.

- 9.1  $Y_{Ii} := UNION(Y_{Ii}, R); (i)$

- 9.2 { Copy vector R to the pth. column of mask matrix  $A_{li}$  of input SM,  $\alpha_{li}$  } { where p is the position of the requesting input port within that SM } { This will realize the connection through i th input stage SM,  $\alpha_{li}$  }  $A_{li}[*,p] := UNION(A_{li}[*,p],R); (i)$

#### Explanation of the algorithm

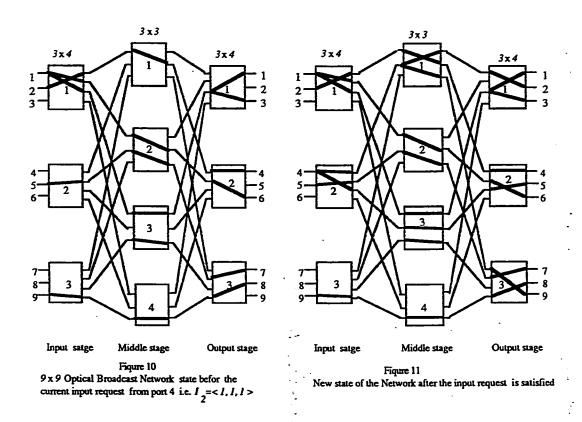

Let us consider two cases of input broadcast requests for the current state of the network at any given time as shown in figure 10.

Case 1: Input port 4 issues a broadcast request to output ports 2,5,9. In terms of SMs in the output stage this request is expressed as  $I_2 = \langle 1,1,1 \rangle$  and in terms of output ports it is expressed as  $O_1 = \langle 0,1,0 \rangle$ ,  $O_2 = \langle 0,1,0 \rangle$ ,  $O_3 = \langle 0,0,1 \rangle$ . We have the following vectors for the present state of the network.

$$\begin{split} Y_{1I} &= <1,1,1,0>, Y_{12} = <0,1,0,0>, Y_{13} = <0,0,0,1> \\ Y_{2I} &= <0,1,0>, \quad Y_{22} = <0,1,1>, Y_{23} = <1,0,1>, Y_{24} = <0,0,1> \\ Y_{3I} &= <1,0,1>, \quad Y_{32} = <1,0,1>, \quad Y_{33} = <1,1,0,> \\ X_{3I} &= <0,0,1,0>, X_{32} = <1,1,0,0>, X_{33} = <0,1,0,1> \\ \text{And the middle stage SM Mask Matrices are (columnwise):} \\ A_{2I} &= \left\{ <0,1,0>, <0,0,0>, <0,0,0> \right\} \\ A_{22} &= \left\{ <0,1,0>, <0,0,1>, <0,0,0> \right\} \\ A_{23} &= \left\{ <1,0,0>, <0,0,0>, <0,0,1> \right\} \\ A_{24} &= \left\{ <0,0,0>, <0,0,0>, <0,0,1> \right\} \end{split}$$

Now we walk through the algorithm. After Step 1,  $AVAIL_2 = \langle 1,0,1,1 \rangle$ , since there are available middle switches and also available output ports, we continue. Step 2 is done concurrently and we have the following vectors:  $CANDIDATE_1 = \langle 1,1,0,1 \rangle$ ,  $CANDIDATE_2 = \langle 0,0,1,1 \rangle$  and  $CANDIDATE_3 = \langle 1,0,1,0 \rangle$ . Step 3 is also done in parallel and it produces possible middle switch sets (set S's) for the request  $I_2$ , resulting in  $S_1 = \langle 1,0,0,1 \rangle$ ,  $S_2 = \langle 0,0,1,1 \rangle$ ,  $S_3 = \langle 1,0,1,0 \rangle$ . Union of these sets produces sufficient number of middle switches required. We need to find the necessary condition also. If any one of them were empty then clearly, the request could not be satisfied. Step 4 takes care of this case. Some of the output SMs could be reached by more than one middle stage SMs (as indicated by more than one entries of I in Ss). We choose one and only one middle stage SM for each output SM. Essentially, we do this by taking out all the I's but the left most one from each one of S's.

This is done concurrently by Step 5 and it results in:

$$T_1 = \langle 1,0,0,0 \rangle$$

,  $T_2 = \langle 0,0,1,0 \rangle$ ,  $T_3 = \langle 1,0,0,0 \rangle$ .

Step 6 computes the union of all T's, resulting in  $R = \langle 1,0,1,0 \rangle$ , which contains the <u>necessary</u> and <u>sufficient</u> number of middle stage SM's. In Step 7, OVP(1) and OVP(3) do the following in parallel:  $CSET_1 = \langle 1,0,1 \rangle$  and  $CSET_3 = \langle 0,1,0 \rangle$ .

Step 7 and Step 8 do the job of setting the connection and updating the network status. The new network status is shown in Figure 11. So after the update, the new vectors are:

$$\begin{split} Y_{11} &= <1, 1, 1, 0>, Y_{12} = <1, 1, 1, 0>, Y_{13} = <0, 0, 0, 1> \\ Y_{21} &= <1, 1, 1>, \quad Y_{22} = <0, 1, 1>, Y_{23} = <1, 1, 1>, Y_{24} = <0, 0, 1> \\ Y_{31} &= <1, 1, 1>, Y_{32} = <1, 1, 1>, Y_{33} = <1, 1, 1, > \\ X_{31} &= <1, 0, 1, 0>, X_{32} = <1, 1, 1, 0>, X_{33} = <1, 1, 0, 1> \end{split}$$

Mask Matrices of the middle stage SMs are (columnwise):

$$A_{21} = \{ < 0, 1, 0 >, < 1, 0, 1 >, < 0, 0, 0 > \}$$

$$A_{22} = \{ < 0, 1, 0 >, < 0, 0, 1 >, < 0, 0, 0 > \}$$

$$A_{23} = \{ < 1, 0, 0 >, < 0, 1, 0 >, < 0, 0, 1 > \}$$

$$A_{24} = \{ < 0, 0, 0 >, < 0, 0, 0 >, < 0, 0, 1 > \}$$

Case 2: Consider the network state of figure 10. Now input port 3 issues a broadcast request for output ports 5 and 9. So  $I_1 = \langle 0, 1, 1 \rangle$ . AVAIL  $I_1 = \langle 0, 0, 0, 1 \rangle$ . Since there is at least one available middle stage SM and also available output ports (CHECK contains no 0 's) we can proceed. Now OVP(2) and OVP(3) do the following in parallel:

$$CANDIDATE_2 = < 0.0, 1.1 >$$

$CANDIDATE_3 = < 1.0, 1.0 >$

$S_2 = < 0.0, 0.1 >$

$S_3 = < 0.0, 0.0 >$

$CHECK = < 1.1.0 >$ .

Now in Step 3 OVP(1) takes the bitwise union of the vector CHECK, which is 0. So the controller aborts the control algorithm with unsuccessful message to the requesting input port. The connection to SM 3 of output stage can not be satisfied as it is clear from the figure 10.

#### Complexity Analysis of the Algorithm

Each of the primitives used in the algorithm have O(1) time complexity as illustrated in section 5.1. Each and every step in the algorithm has O(1) time complexity. So the overall complexity of the network control algorithm is O(1).

# 3.6 Conclusion

We have extended the design of Nonblocking Broadcast Network proposed by Yang and Masson using free space optics. This led us to exploit the inherent parallelism provided by optics to come up with a constant time network control algorithm on a network controller, using nonnumeric computation.

# Chapter 4

# Optical Realization of Constant Time Sorting Algorithm on a Processor Matrix with a Reconfigurable Inter-Processor Bus System

#### 4.1 Introduction

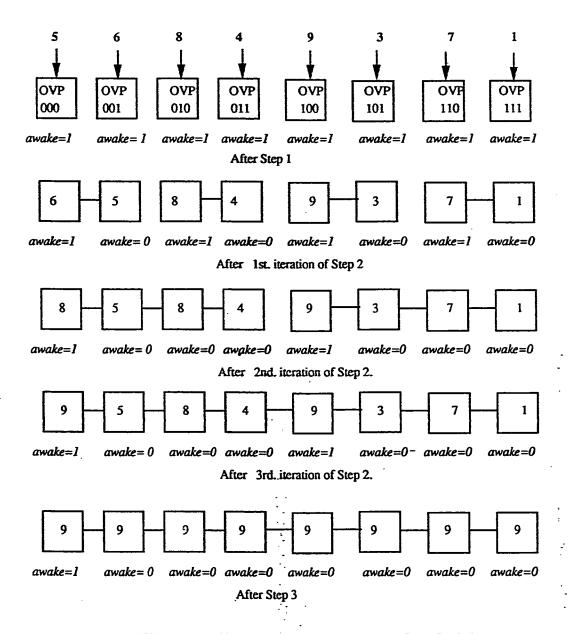

Sorting problem is one of the most studied problems in computer Science. Given N numbers, the problem asks the numbers to be arranged in nondecreasing or nonincreasing order. A good number of literature on different methodologies and using different algorithms on conventional Von Neumann machine is available[AHO 74, KNUTH 73]. The time complexity of the best algorithm on such sequential computing is O(NlogN). To seek for better solutions, parallel algorithms have been proposed on various parallel computation models[LAKS 84], [AKL 85], [AKL 89].

Theoretically, a constant time sorting can be achieved on an extremely powerful CRCW PRAM model (Concurrent-read-concurrent-write parallel random access machine). In this model concurrent access (read or write) to the same memory location is allowed and the write conflict is resolved by allowing all the processors to write the sum-of-all-writes only. Obviously this machine is too idealistic to be implemented with the state-of-the-art VLSI technology in terms of hardware complexity, cost and communication overhead required between processors.

Processor arrays interconnected by locally controllable global buses have attracted the attention of many researchers [KUMA 87, BOKH 84, AGGA 86]. Each processor within the grid structure can change the bus connection by reconfiguring the local buses dynamically. A bus connected system whose configuration can be changed by distributed control algorithm is called a *Reconfigurable Bus System (RBS)*.

Using the reconfigurable bus based grid structure of RAM machines or conventional processors, there have been two designs to sort N numbers in constant time, proposed in the literature. The first one [WANG89] proposes a constant time sorting algorithm with hardware complexity of  $O(N^3)$ , that is, using RAM processors of the order of  $N^3$ . The sorting is done by enumeration. In the second paper [NAKA90] a new technique is proposed to reduce the enormous hardware complexity to  $O(N^2log^2N)$ . The hardware complexity is still a concern when it comes to the question of implementation. Further more the reconfigurable bus system is more of a theoretical interest rather than a practical system as far as electronic implementation is concerned.

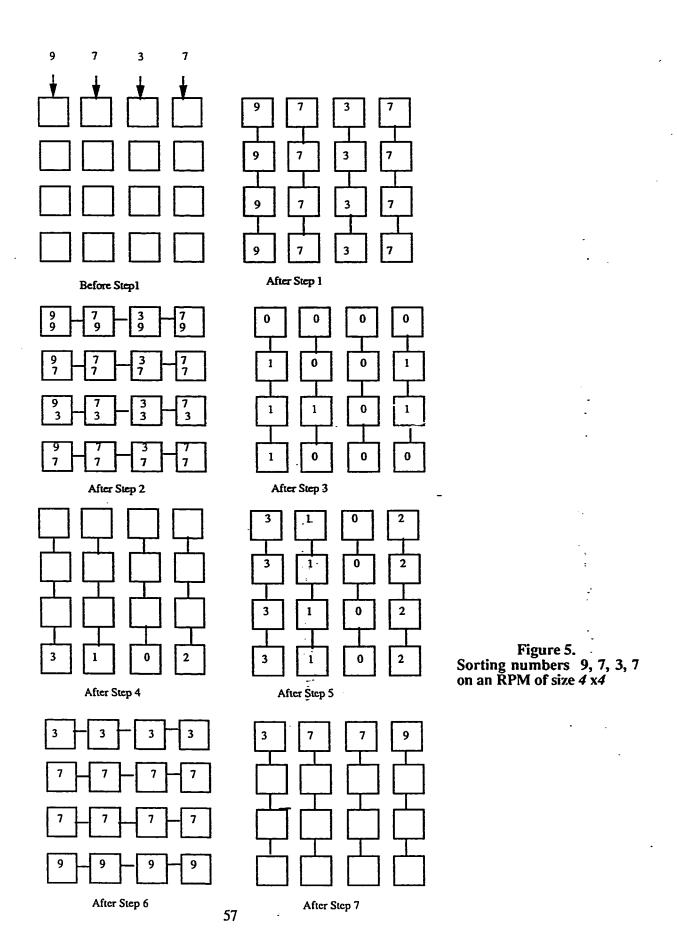

The capability of optics to do processing and communicating between points in parallel has a great potential for implementing a constant time sorter. In this Chapter, we propose a constant time sorting algorithm using all optical processing elements. We exploit the natural parallelism and the interference-free connectivity provided by free-space optics. Our proposed sorter has a hardware complexity of  $O(N^2)$  in terms of number of optical processors to be defined later.

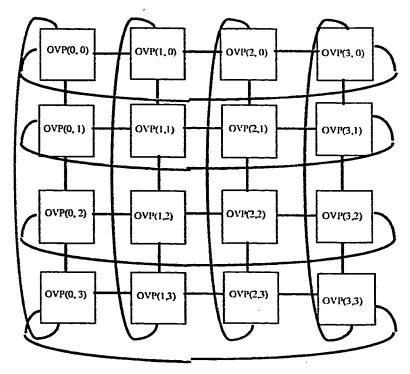

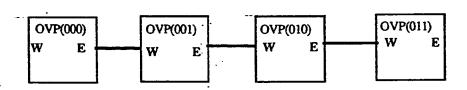

#### 4.2 Proposed Optical Vector Processor Matrix Architecture

A Reconfigurable Processor Matrix(RPM) consists of processors arranged in a two dimensional grid with wrap around connections (Figure 1). Each processor is an Optical Vector Processor (OVP)—(Appendix 1) with the extension that each has 4—parallel ports. These ports provide connections either to vertical or horizontal global bus. In an NxN—RPM, OVP(i, j)—stands for OVP in  $i^{th}$  row,  $j^{th}$  column,  $0 \le i, j \le N-1$ . These ports are denoted N,S,W,E and each port is capable of communicating  $W \ge N$  (W—is the word length of the processor) bits of information in parallel. The ports of the adjacent processors facing each other are connected by fixed buses, that is, S(OVP(i, j)) and  $N(OVP(i, (j+1) \mod N))$  are connected by fixed optical fibres. Similarly, E(OVP(i, j)) and  $W(OVP((i+1) \mod N, j))$  are also connected statically.

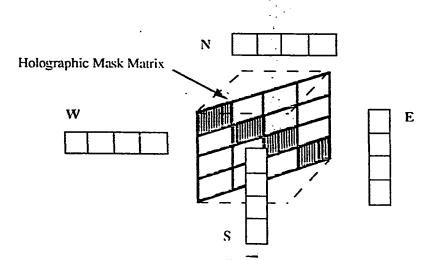

#### 4.2.1 Optical Vector Processor (OVP)

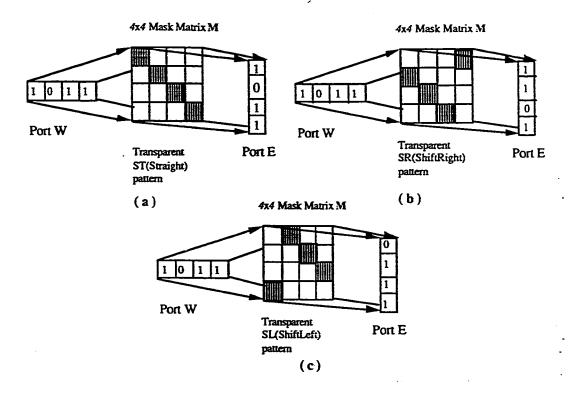

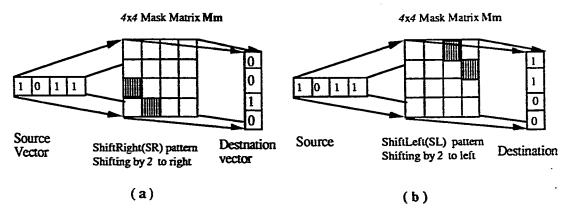

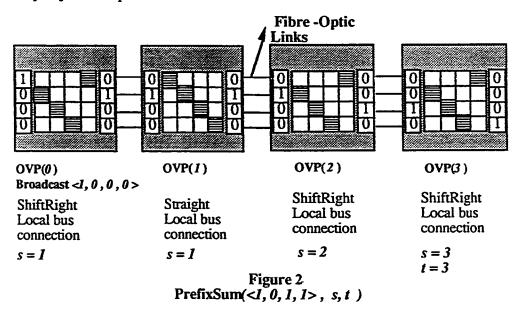

An OVP perform some primitive operations on binary vectors as discussed in Chapter III. We extend the design of OVP, adding  $4\ W$  -bit parallel ports, where W is the precision of the proposed processor. The 4 ports are: N,S,W and E. To indicate the ports on certain OVP(i, j), we use the index of that particular processor as argument with the port name. For example, port N on OVP(2,3) is to be denoted as N(2,3). Each processor can connect its ports W with E and ports N with S by writing the required grating patterns on a holographic mask matrix M. The mask matrix is of size WxW, where W is the vector-width or word-length of the OVP. To connect any two opposite ports (such as, N with S and W with E), the OVP records a fixed grating pattern on all the elements of the forward diagonal of the connection mask matrix, M, to create the required connection.

Figure 1

4 x4 Reconfigurable Processor Matrix with wrap around bus connection

Erasing an existing grating pattern and then writing a new one takes constant time, since there are W elements to be written and the patterns are fixed. So each OVP can change the local bus connection in constant time resulting in dynamic reconfuguration of the global bus. To establish the required local connection demanded by the global algorithm each OVP executes CONNECT instruction. This instruction is discussed later in this section.

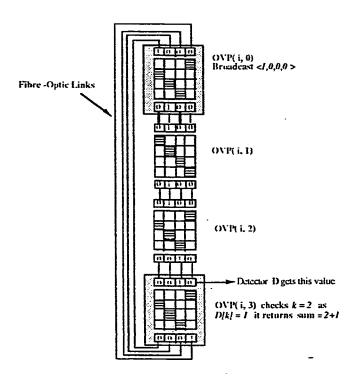

Associated with each OVP, there is a laser source vector C and a detector vector D. Vector C of source is used to send information to the global bus whereas vector D of photodetectors is used to read the value(binary vector) on the global bus. Sending to and receiving information from the bus are carried out by simple beam steering elements like Beam Splitters.

#### 4.2.1.1 Comparing Two Numbers on OVPs