### INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

# AN EFFICIENT TEST-PATTERN RELAXATION TECHNIQUE FOR SYNCHRONOUS SEQUENTIAL CIRCUITS

يخاعد اعداعد اعداعد

BY

### KHALED ABDUL-AZIZ AL-UTAIBI

A Thesis Presented to the DEANSHIP OF GRADUATE STUDIES

### KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

### **MASTER OF SCIENCE**

In

COMPUTER ENGINEERING

NOVEMBER 2002

**UMI Number: 1411740**

#### UMI Microform 1411740

Copyright 2003 by ProQuest Information and Learning Company.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

### KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

### DHAHRAN 31261, SAUDI ARABIA

### DEANSHIP OF GRADUATE STUDIES

This thesis, written by KHALED ABDUL-AZIZ AL-UTAIBI under the direction of his thesis advisor and approved by his thesis committee, has been presented to and accepted by the Dean of Graduate Studies, in partial fulfillment of the requirements for the degree of MASTER OF SCIENCE IN COMPUTER ENGINEER-ING.

Thesis Committee

Dr. Aiman El - Maleh (Chairman)

Alaaeldin Amin (Member)

Dr. Atef Al – Najjar (Member)

Department/Chairman

Dean of Graduate Studies

21/12/2000

Dedicated

to

the memory of my father

and

to my mother.

# Acknowledgments

Acknowledgement due to King Fahd University of Petroleum and Minerals for supporting this research.

I would like to express my appreciation to my thesis committee chairman Dr. Aiman El-Maleh for his guidance, patience, and sincere advice throughout this thesis. I acknowledge him for his valuable time, constructive criticism, and stimulating discussions. Thanks are also due to my thesis committee members, Dr. Alaaeldin Amin and Dr. Atef Al-Najjar for their comments and critical review of the thesis.

I am very thankful to the department chairman Dr. Sadiq Sait, for his cooperation and support.

I am also thankful to my fellow graduate students and all my friends especially Mr. Ali Al-Suwaiyan.

# **Contents**

|   | Acl  | knowledgments                                                      | i         |

|---|------|--------------------------------------------------------------------|-----------|

|   | List | t of Tables                                                        | •         |

|   | List | t of Figures                                                       | v         |

|   | List | t of Algorithms                                                    | vii       |

|   | Abs  | stract (English)                                                   | ix        |

|   | Abs  | stract (Arabic)                                                    | X         |

| 1 | Inti | roduction                                                          | 1         |

|   | 1.1  | Testing Systems-on-a-Chip (SOC)                                    |           |

|   | 1.2  | Motivation                                                         |           |

|   | 1.3  |                                                                    | 5         |

|   | 1.4  |                                                                    |           |

| 2 | Lite | erature Review                                                     | 8         |

|   | 2.1  | Compression/Decompression Techniques                               | 9         |

|   |      | 2.1.1 Line-Feed-Shift-Register-Reseeding (LFSR-Reseeding)          | 10        |

|   |      | 2.1.2 Run-length Coding                                            |           |

|   |      | 2.1.3 Statistical Coding                                           |           |

|   | 2.2  |                                                                    |           |

|   |      | 2.2.1 Compaction by Overlapping Self-Initializing Test Sequences . | 29        |

|   |      | 2.2.2 Compaction Based on Insertion, Omission, and Selection       |           |

|   |      | 2.2.3 Compaction Based on Vector Restoration                       | 37        |

|   |      | 2.2.4 Compaction Based on Inert Subsequence Removal                | 40        |

|   | 2.3  | Test-Pattern Relaxation Techniques for Combinational Circuits      | 45        |

| 3 |      | posed Test-Relaxation Technique                                    | <b>52</b> |

|   | 3.1  | Illustrative Examples                                              | 53        |

|   |     | 3.1.1 Single Value Justification                                         |

|---|-----|--------------------------------------------------------------------------|

|   |     | 3.1.2 Limitations of Single Value Justification                          |

|   |     | 3.1.3 Two Values Justification                                           |

|   | 3.2 | Formal Description                                                       |

|   |     | 3.2.1 Single-Value Justification                                         |

|   |     | 3.2.2 Two-Values Justification                                           |

|   | 3.3 | Selection Criteria                                                       |

|   | 3.4 | Worst Case Analysis                                                      |

|   |     | 3.4.1 Space Complexity                                                   |

|   |     | 3.4.2 Time Complexity                                                    |

| 4 | Exp | erimental Results 90                                                     |

|   | 4.1 | Comparison with Bitwise-Relaxation                                       |

|   | 4.2 | Experiments on Cost Functions                                            |

|   | 4.3 | Examining Different Aspects of the Two-Values Justification Technique 95 |

|   | Con | clusion 100                                                              |

|   | BIE | LIOGRAPHY 103                                                            |

# List of Tables

| 2.1  | Transition table for run-length coding                                | 19 |

|------|-----------------------------------------------------------------------|----|

| 2.2  | Variable to fixed length coding.                                      |    |

| 2.3  | Golomb codes $(m = 4)$                                                |    |

| 2.4  | FDR code                                                              |    |

| 2.5  | Extended FDR code                                                     |    |

| 2.6  | The test sequence of Example 2.1                                      |    |

| 2.7  | The fault detection of the test sequence in Example 2.1               | 34 |

| 2.8  | The test sequence of Example 2.1 after insertion                      | 34 |

| 2.9  | The fault detection of Example 2.1 after insertion                    | 35 |

| 2.10 | Fault detection of Example 2.2                                        | 38 |

| 2.11 | Test subsequences of Example 2.2                                      | 38 |

|      | Fault detection of Example 2.3                                        |    |

| 4.1  | Benchmark circuits                                                    | 91 |

| 4.2  | Test relaxation comparison between the two-values justification (TVJ) |    |

|      | technique and the bitwise-relaxation method                           | 93 |

| 4.3  | Cost function effect on the extracted percentage of X's               | 94 |

| 4.4  | Percentage of X's obtained by SVJ using different weights             | 97 |

| 4.5  | Test relaxation comparison between TVJ and SVJ                        | 98 |

| 4.6  | Percentage of X's obtained by GVCF using different weights            | 98 |

| 4.7  | Test relaxation comparison between TVJ and GVCF                       | 98 |

| 4.8  | Percentage of X's obtained by UACF using different weights            | 99 |

# List of Figures

| 1.1  | An example of test-sequence relaxation in sequential circuits          | 5  |

|------|------------------------------------------------------------------------|----|

| 2.1  | General structure of the single-polynomial LFSR                        | 12 |

| 2.2  | Decompression using a single-polynomial LFSR                           |    |

| 2.3  | An example of seed-computation in a single-polynomial LFSR             |    |

| 2.4  | General structure of the multiple-polynomial LFSR                      |    |

| 2.5  | An example of a Burrows-Wheeler transformation                         | 17 |

| 2.6  | Preparation of the matrix to be encoded                                |    |

| 2.7  | An example of the modified run-length coding                           |    |

| 2.8  | Structure of the cyclical scan chain                                   | 22 |

| 2.9  | An example of a Golomb coding.                                         |    |

| 2.10 |                                                                        |    |

| 2.11 | Construction of a Huffman tree                                         | 28 |

|      | Merging of two test sequences                                          |    |

| 2.13 | Examples of merging two test sequences                                 | 32 |

| 2.14 | Subsequence removal (Criterion 1)                                      | 41 |

| 2.15 | Subsequence removal (Criterion 2)                                      | 42 |

| 2.16 | Subsequence removal (Criterion 3)                                      | 43 |

| 2.17 | Circuit of Example 2.4                                                 | 45 |

| 2.18 | Circuit of Example 2.5                                                 | 47 |

|      | Circuit of Example 2.6                                                 |    |

|      | Limitation of the extended implication/justification                   |    |

|      | Circuit of Example 2.7                                                 |    |

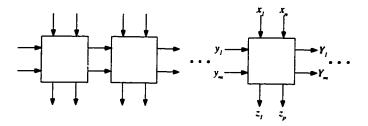

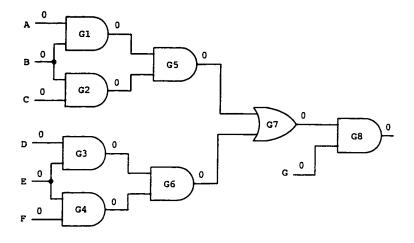

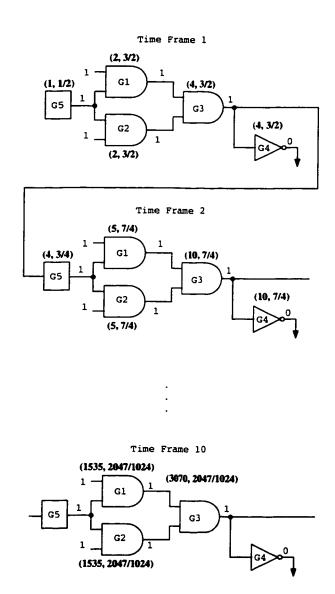

| 3.1  | Iterative array model for asynchronous sequential circuits             | 54 |

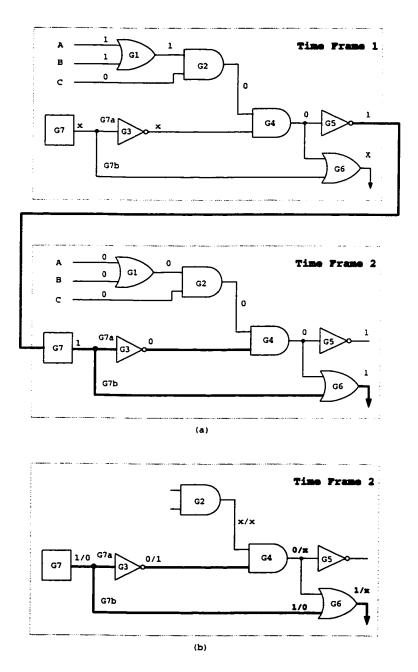

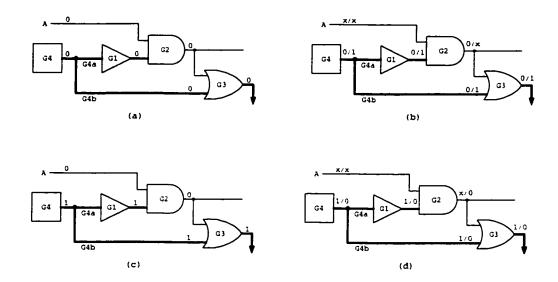

| 3.2  | An example of the single-value relaxation                              |    |

| 3.3  | Limitations of the single-value relaxation                             |    |

| 3.4  | An example of the two-value relaxation                                 |    |

| 3.5  | Circuit of Example 3.13                                                | 81 |

| 3.6  | Circuit of Example 3.14.                                               | 82 |

| 3.7  | Illustration of the effect of reconverging fanouts on the regular cost | 84 |

| 3.8  | Circuit of Example 3.16                                                | 85 |

| 4.1 | Effect of PO's selection on test vector relaxation. |  |  |  |  |  |  |  |  |  |  |  | g | )3 |

|-----|-----------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|---|----|

|-----|-----------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|---|----|

# List of Algorithms

| 3.1 | Main Algorithm                                                                                                                              | 35 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | $MarkReachableLines(f,t) \dots \dots$ | 37 |

|     | $\operatorname{JustifyFault}(f,t)$                                                                                                          |    |

|     | Main Algorithm                                                                                                                              |    |

|     | ComputeFaultyValues $(f,t)$                                                                                                                 |    |

|     | $\operatorname{JustifyFault}(f,po,t)$                                                                                                       |    |

|     | $\operatorname{JustifyGate}(g,f,t)$                                                                                                         |    |

|     | (Cont.) JustifyGate $(g,f,t)$                                                                                                               |    |

|     | GetCorrespondingValue $(g,h,v_1,v_2)$                                                                                                       |    |

#### THESIS ABSTRACT

Name: KHALED ABDUL-AZIZ AL-UTAIBI

Title: AN EFFICIENT TEST-PATTERN RELAXATION

TECHNIQUE FOR SYNCHRONOUS SEQUENTIAL

**CIRCUITS**

Major Field: COMPUTER ENGINEERING

Date of Degree: NOVEMBER 2002

Testing systems-on-a-chip (SOC) involves applying huge amounts of test data, which is stored in the tester memory and then transferred to the circuit under test (CUT) during test application. Therefore, practical techniques, such as compression and compaction, are required to reduce the amount of test data in order to reduce both the total testing time and the memory requirements for the tester. Some of the existing compression/compaction techniques require the test data to be partially specified, while others can benefit from partially specified test sets either directly or by specifying the don't care values in these test sets in a way that improves their efficiency. One obvious way to extract the don't care values in the test sets is to test for the possibility of changing every bit in the test set to an X based on fault simulation. This is called bitwise relaxation. In this thesis, we propose a novel and efficient test relaxation technique for synchronous sequential circuits. The proposed technique is faster than the bitwise relaxation method by several orders of magnitude.

#### MASTER OF SCIENCE DEGREE

King Fhad University of Petroleum and Minerals, Dhahran.

NOVEMBER 2002

### ملخص الرسالة

الاسمة خالد بن عبد العزيز العتيبي

عنوان الرسالة: استخلاص القيم غير المحددة في بيانات الاختبار للدوائر المتسلسلة

التخصيص: هندسة الحاسب الآلي

تاريخ التخسرج: رمضان ١٤٢٣ هـ

إن اختبار الأنظمة المدمجة على رقاقة واحدة يتطلب تطبيق أعداد ضخمة من بيانات الاختبار التي يتم تخزينها في ذاكرة أجهزة الاختبار قبل تطبيقها على الدوائر المراد فحصها، ولذلك فان التعامل مع هذه الكميات الضخمة من بيانات الاختبار يتطلب استخدام تقنيات فعالة، كضغط البيانات وتقليصها، وذلك لتقليص وقت الاختبار وكمية الذاكرة المطلوبة لفحص الدوائر، والملاحظ أن بعض تقنيات ضغط/تقليص البيانات تتطلب أن تكون بيانات الاختبار محددة جزئيا، بينما يمكن للبعض الآخر من هذه التقنيات الاستفادة من بيانات الاختبار المحددة جزئيا من خلال تحديد هذه البيانات بما يزيد من فاعلية عملية الضغط أو التقليص.

تقتضي الطرق التقليدية لاستخلاص بيانات الاختبار المحددة جزئيا؛ تحويل قيمة كل وحدة من بيانات الاختبار إلى قيمة غير محددة، ومن ثم اختبار الدائرة لمعرفة تأثير الوحدة المعدلة على عدد الأخطاء المكتشفة، وبناء على نتيجة الاختبار تحتفظ الوحدات التي لم تؤثر على عدد الأخطاء المكتشفة بالقيم غير المحددة، بينما تستعيد الوحدات التي أثرت على عدد الأخطاء المكتشفة قيمها الأصلية.

في هذه الأطروحة نقدم تقنية جديدة لاستخلاص بيانات الاختبار المحددة جزئيا للدوائر المتسلسلة التقنية المقترحة تتقوق على الطرق التقايدية في عامل الوقت الذي تتطلبه عملية استخلاص البيانات المحددة جزئيا المحددة على الطرق التقايدية في عامل الوقت الذي المحددة المقترحة المقايدية في عامل الوقت الذي المحددة المحددة المحددة المقايدية المحددة المحددة المقايدية المحددة المح

درجة الماجستير في العلوم جامعة الملك فهد للبترول والمعادن الظهران، المملكة العربية السعودية رمضان ١٤٢٣ هـ

# Chapter 1

### Introduction

### 1.1 Testing Systems-on-a-Chip (SOC)

Rapid advancement in VLSI technology has lead to a new paradigm in designing integrated circuits where a *system-on-a-chip* (SOC) is constructed based on predesigned and pre-verified cores such as CPUs, digital signal processors, and RAMs.

Testing SOC is a major challenge due to limited access to the input and output lines of each core during test application. The test vectors for each core must be applied to the core inputs and the test responses must be observed at the core's outputs. A straightforward solution is to have full access to the input and output lines of all cores by multiplexing these lines to the chip pins. However, the complexity of this solution could be enormous. A more efficient way for providing test access to the cores is to use scan chains. The number and organization of these scan chains

determine the test data bandwidth (i.e., the rate of scanning in and scanning out test vectors and test responses respectively).

Another challenging problem in testing SOC is to deal with a large amount of test data that must be loaded from the tester memory, transferred to the SOC, and applied to the individual cores. The amount of time required to test a chip depends on the size of the test data that needs to be transferred and the speed of this transfer operation (i.e., test data bandwidth). The cost of automatic test equipments (ATE's) increases significantly with the increase in their speed, channel capacity, and memory size. Thus reducing the amount of test data and test time is a major concern in testing SOC [1].

One solution to this problem is to use built-in self-test (BIST) where on-chip hardware is added to enable the chip to test itself. The scheme has many advantages, especially the ability of self-testing at normal clocking rates (i.e., test at-speed), the ability for testing systems on-line, and reducing or eliminating the need for the expensive external ATE's. However, BIST has several drawbacks such as the complexity of designing test tools and degradation of the system performance that may occur due to the added hardware. In addition to that, BIST tools, which depend only on pseudo random generators, can't achieve high fault coverage because some faults are hard-to-detect using random test vectors.

Another alternative is to reduce the amount of test data using compression and compaction techniques. The objective of test set compression is to reduce the num-

ber of bits needed to represent the test set. Several test compression techniques have been proposed [2, 3, 4, 5, 6, 7, 8, 9]. In test compaction, the number of test vectors is reduced into a smaller number that achieves the same fault coverage. Test compaction techniques can be classified into two categories: dynamic compaction and static compaction. Dynamic compaction schemes such as [10, 11, 12, 13] try to reduce the number of test vectors during test vector generation. Static compaction schemes, on the other hand, perform compaction on test sequences after they are generated. Several static test compaction techniques have been proposed for synchronous sequential circuits. The techniques proposed in [14] use overlapping of self-initializing test sequences. Four compaction techniques based on insertion. omission, selection and restoration have been proposed by Pomeranz and Reddy [15, 16]. The technique in [17] compacts test sequences by removing inert subsequences under certain conditions.

### 1.2 Motivation

Compression techniques can achieve better results if the test set is composed of test cubes (i.e., if the test set is partially specified). In fact, some compression techniques such as, Line-Feed-Shift-Register-Reseeding (LFSR-Reseeding) [2, 3], require the test vectors to be partially specified. Even those techniques which require fully specified test data can benefit from the unspecified bits in the test set. For example,

variable-to-fixed-length coding [4] and variable-to-variable-length coding [5, 6] are known to perform better for long runs of 0's. Hence, assigning 0's to the don't care values in the test set will improves the efficiency of these techniques. Similarly, run-length coding techniques [7] can specify the don't care values in a way that will reduce test vector activity (i.e., the number of transitions from 0 to 1 and vice versa), which in tern improves the compression efficiency. On the other hand, the amount of compression that can be achieved with statistical coding techniques depends on degree of variation in the occurrences of unique test patterns (i.e., code words). If all test patterns occur with equal frequency, then no compression is achieved at all [18]. Thus, using partially specified test vectors adds more flexibility to statistical coding techniques in a sense that test patterns containing don't care values can be encoded with various possibilities.

Compaction techniques can also benefit from partially specified test sets. For example, when merging two test sequences using the overlapping compaction techniques described in [14], a don't care value, 'X', can be merged with any one of the values: '0', '1', and 'X'. Therefore, increasing the number of X's in a test set will reduce the number of conflicts that may occur when merging two test sequences, and hence, improves the efficiency of compaction.

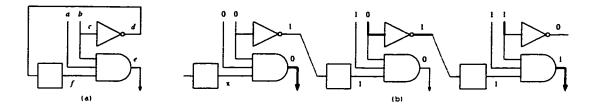

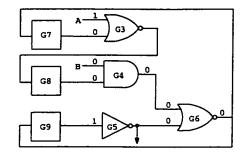

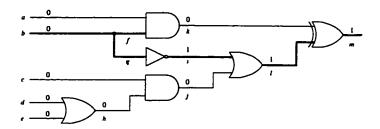

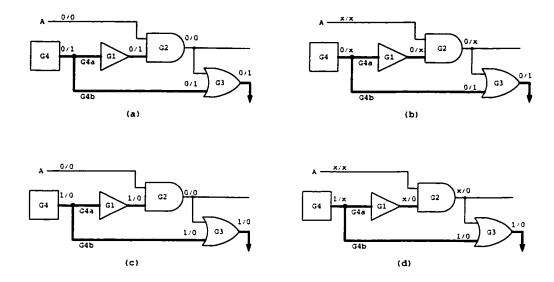

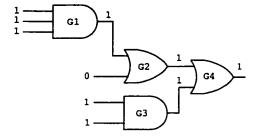

Figure 1.1: An example of test-sequence relaxation in sequential circuits.

### 1.3 Problem Definition

The problem of test set relaxation, i.e., extracting a partially specified test set from a fully-specified one, has not been solved effectively in the literature. This problem, which is targeted in this thesis, can be defined as follows. Given a synchronous sequential circuit and a fully specified test set, generate a partially specified test set that maintains the same fault coverage as the fully specified one while maximizing the number of unspecified bits. As an example, consider the circuit shown in Figure 1.1 (a) and the test set  $ab=\{00, 10, 11\}$ . Under this test set 5 faults are detected: e/1, e/0, d/0, b/1 and b/0. These faults are shown as bold lines in Figure 1.1 (b). Notice that it is enough to set either a=0 or b=0 in the first test vector in order to detect the fault e/1. Hence, either one of these two bits can be set to 'X' and the fault is still detected. Also, the assignment a=1 in the second test vector does not affect the detection of any one of the 5 faults. Therefore, this bit can be set to 'X' as well. As a result, the five faults can be detected under the relaxed test set  $ab=\{X0, X0, 11\}$ .

One obvious way to solve the problem of test set relaxation is to use the bitwise-

relaxation method, where we test for every bit of the test set whether changing it to 'X' reduces the fault coverage or not. Obviously, this technique is O(nm) fault simulation runs, where n is the width of one test vector, m is the number of test vectors. Obviously, this technique is impractical for large circuits.

In this thesis, we propose an efficient test relaxation technique for synchronous sequential circuits that maximizes the number of unspecified bits while maintaining the same fault coverage as the original test set. Our technique uses fault simulation to collect information about faults detected in every time frame (i.e., test vector) and faults propagating from one time frame to another. This information is used during a back-tracing phase starting from the last time frame all the way to the first time frame. The purpose of this phase is to mark all lines whose values are necessary to detect all the faults detected during the fault simulation phase. Obviously, any primary input that is not marked during the back-tracing phase is not required for fault detection, and hence can be relaxed. As compared to the bitwise-relaxation method, out technique is faster by several orders of magnitude.

### 1.4 Thesis Organization

The rest of the thesis is organized as follows. In Chapter 2, literature survey is presented. This chapter reviews several compression and compaction techniques proposed for synchronous sequential circuits. In addition to that, this chapter dis-

cusses some of the techniques proposed in the literature for solving the problem of test pattern relaxation for combinational circuits.

Chapter 3 covers implementation details of the proposed test-pattern relaxation algorithm for synchronous sequential circuits. This chapter starts with illustrative examples that explain the general behavior of the proposed algorithm. Then, it discusses the implementation details on different phases of the relaxation algorithm.

In Chapter 4 experimental results for the proposed technique are compared to the bitwise-relaxation method. The thesis ends with conclusion and future work.

# Chapter 2

## Literature Review

One of the challenges in testing SOC is to deal with a large amount of test data that must be loaded from the tester memory and transferred to the CUT during test application time. Reducing this amount of test data will significantly reduce the total test time, which in turn reduces the time-to-market. Test compression and compaction are known to be practical solutions for this problem. The efficiency of the test compression and compaction schemes depends on the test data itself. For most of the schemes that will be shown in this chapter, it is more efficient to work with a partially specified test set rather than a fully-specified one. Therefore, an efficient relaxation scheme is required to improve the efficiency of test compression and compaction techniques.

In this chapter, we review several test compression and compaction techniques proposed for synchronous sequential circuits, as well as some of the existing testpattern relaxation techniques for combinational circuits.

### 2.1 Compression/Decompression Techniques

The objective of test data compression is to compress (encode) a given test set  $T_D$  to a much smaller test set  $T_E$  that is stored in the tester memory. During test application,  $T_E$  is loaded from the tester memory and decompressed (decoded) using some decompression mechanism to obtain the original test set  $T_D$  before applying it to the required core. In order to guarantee the correctness of all applied test vectors and achieve a reduction in the overall testing time, a test compression/decompression scheme should meet two characteristics: lossless and simple decompression. The first characteristic must be met to guarantee the correctness of all applied test vectors. The second characteristic is important to guarantee a reduction in the overall testing time. Moreover, the decompression circuitry, residing at the core side, must be small so that it doesn't add significant area overhead. In addition to that, test compression/decompression schemes, designed for sequential circuits, must preserve the order of test vectors in every individual test set.

Compression/decompression schemes for deterministic test vectors can be classified, based on the type of test data they require, into three categories.

1. Schemes that require test data to be in the form of test cubes. Examples include LFSR reseeding [2, 3].

- Schemes that require fully specified test vectors such as variable-to-fixed-length codes [4], variable-to-variable-length codes, and Extended frequency-directed run-length codes (EFDR) [5, 6, 19].

- 3. Schemes that have no specific requirements about the type of the test data.

They compress test data regardless of their type. Run-length coding [7] and

Huffman coding [8] are among the examples of this category.

Next, we will review some of the compression/decompression schemes targeting deterministic test vectors generated by ATPGs (schemes based on pseudo-random test vectors are out of the scope of this work).

### 2.1.1 Line-Feed-Shift-Register-Reseeding (LFSR-Reseeding)

Pseudo-random techniques (i.e., LFSRs) used in BIST designs for test generation don't need storage memories, and can be implemented with a small amount of hardware. However, they require long test sets to achieve high fault coverage because some faults are hard-to-detect using random vectors. Thus, LFSRs may generate several millions of test patterns before detecting these faults [20].

Several techniques have been proposed to address this problem. One approach involves the insertion of test-points in the CUT to enhance its random testability [14]. The disadvantage of this technique is that it requires modification of the CUT with possible performance degradation. Mixed-mode test pattern generation

is an alternative solution to this problem. The key idea in this approach is to use some mechanism to generate deterministic vectors that are known to cover hard-to-detect faults, while covering the remaining faults using pseudo-random test vectors. The additional cost of this approach depends on the logic required to include the deterministic test vectors, and more importantly, the storage capacity of these test vectors.

Below we review two approaches to reduce the storage requirements for the mixed-mode designs by encoding test cubes of the hard-to-detect faults using fixed-length seeds.

### Single-Polynomial-LFSR Reseeding (SP-LFSR)

Koenemann [2] has proposed a compression/decompression technique for mixed-mode designs based on an intelligent reseeding of a single-polynomial LFSR. The technique uses short-length seeds to encode the test cubes. The resulting seeds are, then, stored in a ROM or a finite-state-machine (FSM). During test application time, the same LFSR is used to generate pseudo-random test vectors as well as deterministic test vectors.

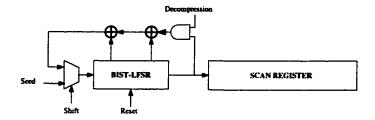

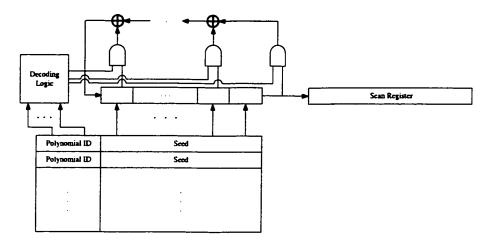

The general structure of this technique is shown in Figure 2.1, where a deterministic test vector is generated by, first, resetting the LFSR. Then, the corresponding seed is loaded into the LFSR (reseeding). Finally, enough clocks are applied to shift the seed into the scan register, which will hold the desired pattern.

Figure 2.1: General structure of the single-polynomial LFSR.

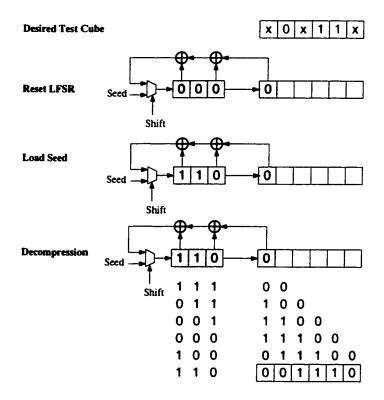

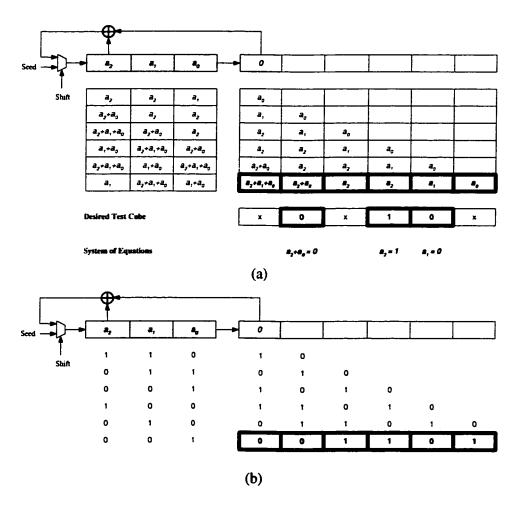

Figure 2.2 illustrates an example of generating a test pattern "X0X11X" from the seed "110". The decompression hardware, for this example, consists of a 4-bit LFSR formed using an existing 3-bit LFSR and one flip-flop from the scan register.

The seeds are computed based on the specified bits of the corresponding test cubes. As an example consider the LFSR represented by the polynomial  $h(x) = x^3 + 1$ . If the LFSR is to generate a test cube "X0X10X", then a corresponding seed can be determined, as shown in Figure 2.3 (a), by solving the following system of equations:

$$a_0 + a_2 = 0$$

$$a_2 = 1$$

$$a_1 = 0$$

The resulting seed is  $(a_2, a_1, a_0) = (101)$ , which will subsequently produce the test pattern "001101" as shown in Figure 2.3 (b).

Figure 2.2: Decompression using a single-polynomial LFSR.

Figure 2.3: An example of seed-computation in a single-polynomial LFSR.

Figure 2.4: General structure of the multiple-polynomial LFSR.

#### Multiple-Polynomial-LFSR Reseeding

The reseeding approach described in [3] uses multiple primitive polynomials instead of a single polynomial to encode the test cubes as shown in Figure 2.4. The LFSR can operate according to one out of many primitive polynomials. Each test cube is encoded as a polynomial identifier and an initial seed. This process involves solving systems of equations similar to the one shown in Figure 2.2 (a). For each test cube, the process tries to find a suitable seed by checking all the available polynomials one after the other, and stops when finding the first encoding.

It is clear that the SP-LFSR approach requires less computational effort than the MP-LFSR. However, it requires an LFSR with (s + 20) bits in order to reduce the probability of not finding a seed for a test cube with s specified bits to less than  $10^{-6}$ , while a MP-LFSR with 16 polynomials can achieve the same probability using only (s + 4) bits.

### 2.1.2 Run-length Coding

Many compression techniques are based on a well-known compression technique referred to as *run-length* coding. The basic idea of this technique is to encode a sequence of equal symbols (*run*) with a certain *codeword* depending on the length of that run. In this section, we will discuss three compression techniques which are based on run-length coding.

### Run-length Coding with Burrows-Wheeler Transformation (BWT)

The original run-length coding technique compresses data by representing each run into two elements, the repeating-symbol and the run-length. For example, the string "aaabbbbd" is encoded as: (a, 3), (b, 4), and (d, 1). This technique is simple in compression and decompression. However, its efficiency depends on a feature of the encoded string called "activity". The activity of a string is the number of transitions in the string from one symbol to another. For example, the string "aaabbbbd" has an activity of two. Thus, run-length encoding is more efficient for strings with low activity.

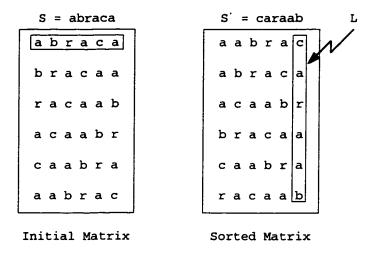

In [7], Burrows-Wheeler transformation (BWT) was used to improve the efficiency of run-length coding. BWT transforms a string S into another string S' by rearranging its symbols in a way that may reduce the string activity. The first step in the BWT is to form an  $n \times n$  matrix, where the  $n^{th}$  row is obtained by rotating the original string (n-1) times to the left. Then, the rows of the matrix are sorted

Figure 2.5: An example of a Burrows-Wheeler transformation.

lexicographically. Finally, the symbols in the last column L are grouped together to form the transformed string. Figure 2.5 shows an example of the BWT.

The BWT, as shown above, is simple and usually results in a better compression using run-length coding. Also, retrieving the original string from the resulting transformation is a simple operation that does not require sorting.

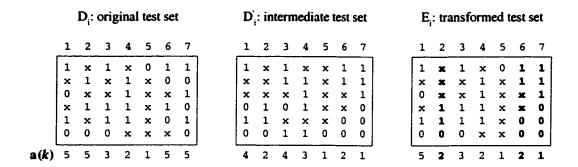

The procedure proposed by Yamaguchi, Tilgner and Ishida [7] works as follows. Given a test set D represented as a matrix  $P \times Q$ , where P is the number of test patterns and Q is the number of PI's, partition D into several equal size submatrices  $D_i$  each of size  $M \times Q$ . This is to reduce the processing time. The BWT is, then, applied on individual columns of every test set  $D_i$  to get an intermediate test set  $D_i'$ . Next, the activity,  $\alpha'(k)$  of every column k in intermediate test set  $D_i'$ , is compared with some threshold activity  $\alpha_t$  and with the activity,  $\alpha(k)$ , of the

Figure 2.6: Preparation of the matrix to be encoded.

corresponding column in the original test set. If the activity of that column is less than both  $\alpha_t$  and  $\alpha(k)$ , the column is copied in the final test set  $E_i$ . Otherwise, the corresponding column from original test set is copied into  $E_i$ . This will save the reverse transformation time for those columns whose BWT will not improve the run-length compression much. Finally, run-length encoding is applied to  $E_i$ .

Figure 2.6 shows an example for constructing an  $E_i$  for some test set  $D_i$ . The last row of each table in the figure indicates the activity of the columns. After applying BWT on  $D_i$ , the activity of the columns: 1, 2, 6, and 7, has decreased. However the activity of column 1, which is 4, is still above the threshold value ( $\alpha = 3$ ). Hence, column 1 is copied from the original test set. Note that copying column 3 from  $D_i$  is trivial since its activity has increased after the BWT.

The transformed test set can be encoded using a straightforward run-length coding that encodes a run using two tuples, (s, L), where s is the repeating symbol and L is the length of the run. However, a more efficient run-length coding scheme was used in [7]. The main idea of this scheme is to combine the run lengths of two

Table 2.1: Transition table for run-length coding.

|                        |   |          | Symbol | t   |

|------------------------|---|----------|--------|-----|

| Transition $(s \to t)$ |   | 0        | 1      | х   |

|                        | 0 | <u> </u> | L      | L+M |

| Symbol s               | 1 | L+M      | -      | L   |

|                        | х | L        | L+M    | _   |

consecutive runs into a single integer using some predefined transition table. As an example, consider the string "0000XX". This string has two runs: s= "0000" and t= "XX". One possible transition table for combining the lengths of two consecutive runs with three logic values ('0', '1', 'X') is shown in Table 2.1, where M is the length of the whole string (which is 6 in this example) and L is the length of the first run (4 in this case). Thus, the lengths of the two runs can be combined into a single integer (L+M=4+6=10).

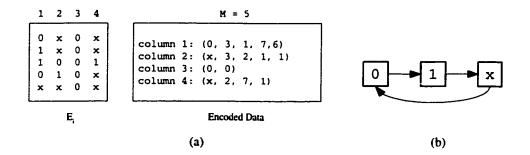

In the above scheme, a string is encoded by giving the first symbol, the activity of the string, and the integers corresponding to the combined run lengths using the transition table. Figure 2.7 (a) shows a complete example for encoding a test set  $E_i$ .

The decompression procedure is done as follows. Start with the symbol given in the encoded data. The integer i, corresponding to the current run, is decoded by computing (i%M) to obtain the length of the current run. The symbol of the next run is the  $j^{th}$  character  $(j = \lceil i/M \rceil)$  following the current symbol in the circular fashion shown in Figure 2.7 (b).

Figure 2.7: An example of the modified run-length coding.

Table 2.2: Variable to fixed length coding.

| Data Block | Codeword |

|------------|----------|

| 1          | 000      |

| 01         | 001      |

| 001        | 010      |

| 0001       | 011      |

| 00001      | 100      |

| 000001     | 101      |

| 0000001    | 110      |

| 0000000    | 111      |

#### Variable-to-Fixed-Length Codes

In this scheme, fully specified test data is compressed using variable-to-fixed-length codes, where a fixed-length codeword is used to encode a block of data based on the number of 0's in that block. Table 2.2 shows a variable-to-fixed-length coding with 3-bits codewords. Using this encoding scheme, the vector "0000010000001100001" can be encoded as follows. The block "000001" is encoded as 101, "0000001" is encoded as 110, "1" is encoded as 000, and "00001" is encoded as 100. Hence, the resulting vector is "101110000100".

The decompression for this scheme can be implemented simply using a counter

that counts down to 0 and outputs a "0" each time it decrements, and outputs a "1" (except for 7 0's) at the end of the count.

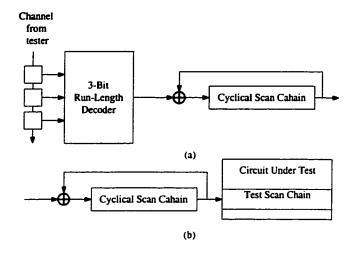

This scheme was used in [4] to compress the difference vector,  $T_{diff}$ , which is given by  $(t_1, t_1 \oplus t_2, t_2 \oplus t_3, t_{n-1} \oplus t_n)$ , instead of compressing the test sequence  $T_D$  itself. This is motivated by the fact that successive test vectors in a test sequence often differ in a small number of bits. Hence, compressing the difference vector is more efficient since it contains more 0's than the original test vectors. In [4], the compressed difference vectors are used as an input to a 3-bit run-length decoder followed by a cyclical scan chain with a feedback to an XOR gate as shown in Figure 2.8 (a). The run-length decoder decompresses the encoded difference vectors, while the cyclical scan chain retrieves the original test vectors. These vectors are passed to a second cyclical scan chain that applies them to the CUT as illustrated in Figure 2.8 (b).

#### Golomb Codes

A drawback of the compression scheme described in [4] is that it uses variable-to-fixed-length codes, which are less efficient than the more general variable-to-variable-length codes. In [5] Golomb codes are used to map variable-length runs of 0's in a difference vector to variable-length codewords. This scheme works for both full-scan and non-scan (sequential) circuits. For full-scan circuits, the test vectors in a given test set can be reordered to maximize the number of 0's. On the other hand, the

Figure 2.8: Structure of the cyclical scan chain.

order of test vector is preserved for non-scan circuits.

This scheme divides the codewords into g groups each of size m. Each one of these groups, as shown in Table 2.3, has a unique prefix, and m members each having  $\log_2 m$  bit sequence (tail) that distinguishes it from other members of the group. The prefix of the  $k^{th}$  group consists of (k-1) 1's followed by a 0.

The first step in encoding a test set  $T_D$  is to generate its difference-vector test set  $T_{diff}$ . The next step is to determine the number of groups, g, and the group size m. The number of groups is determined by the length of the longest run, and the size m is dependent on the distribution of the test data. However, an optimal group size can be determined through actual experiments. Once g and m are determined, the runs of 0's in  $T_{diff}$  are mapped to the g groups, according to their lengths, as follows. The set of run-lengths  $\{0, 1, 2, \ldots, m-1\}$  belongs to group 1; the set  $\{m, m-1\}$

| Group |    | Group Prefix | Tail | Codeword |

|-------|----|--------------|------|----------|

|       | 0  |              | 00   | 000      |

| 1     | 1  | 0            | 01   | 001      |

|       | 2  |              | 10   | 010      |

|       | 3  |              | 11   | 011      |

|       | 4  |              | 00   | 10000    |

| 2     | 5  | 10           | 01   | 10001    |

|       | 6  |              | 10   | 10010    |

|       | 7  |              | 11   | 10011    |

|       | 8  |              | 00   | 110000   |

| 3     | 9  | 110          | 01   | 110001   |

|       | 10 |              | 10   | 110010   |

|       | 11 |              | 11   | 110011   |

Table 2.3: Golomb codes (m = 4)

| T <sub>an</sub>                                                | _ |                                                  | _                                                    |                                                                       |                                            |

|----------------------------------------------------------------|---|--------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------|

| 0001000<br>0011000<br>0100001<br>0000001<br>0010000<br>0001001 | = | 0001<br>00001<br>1<br>00001<br>000001<br>0000001 | L=3<br>L=4<br>L=0<br>L=4<br>L=4<br>L=6<br>L=2<br>L=7 | Codeword= Codeword= Codeword= Codeword= Codeword= Codeword= Codeword= | 1001<br>000<br>1000<br>1000<br>1010<br>010 |

|                                                                |   | 001                                              | L=2                                                  | Codeword=                                                             |                                            |

T<sub>E</sub> = 011 1001 000 1000 1000 1010 010 1011 010

Figure 2.9: An example of a Golomb coding.

$m+1, \ldots, 2m-1$ } belongs to group 2, and so on. The final codeword for a run of length L that belongs to group k consists of the prefix of group k followed by the tail corresponding to the  $j^{th}$  (j=L-(k-1)m+1) member of group k. Figure 2.9 illustrates the encoding of a difference vector test set consisting of 6 vectors using the Golomb codes of Table 2.3. Notice that only the first two groups of this table are required since the length of longest run is 7.

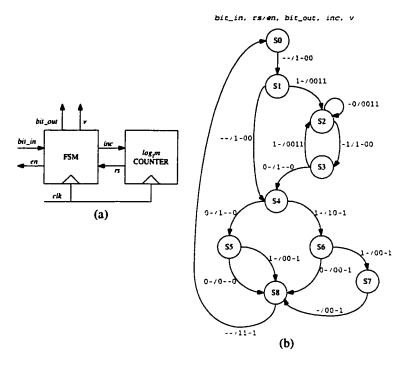

The decompression operation can be implemented using a  $\log_2 m$  bit counter that

counts up to m and a finite-state-machine as shown in Figure 2.10. The en signal synchronizes the input of the decoder. When en is high the next bit of the current codeword is shifted into the FSM through  $bit\_in$ . The inc signal is used to increment the counter, and the rs signal indicates that the counter has finished counting. The v signal synchronizes the decoder output. When v is high one decoded bit is shifted out through  $bit\_out$ .

The decoder starts by decoding the prefix of the codeword. For every 1 in the prefix, the counter counts up to m (the en signal is low while the counter is busy counting). During this operation, the decoder outputs m 0's. When the last 1 in the prefix gets decoded (i.e., a 0 is shifted in), the FSM starts decoding the tail sequence of the codeword. The number of 0's generated during this operation is equivalent to value of the tail sequence. Finally, the decoder outputs a 1 at the end of the decoding operation.

#### Frequency-Directed Run-Length Code

Frequency-directed run-length (FDR) code [5] is another variable-to-variable coding technique based on encoding runs of 0's. In FDR code, the prefix and tail of any codeword are of equal size. In any group  $A_i$ , the prefix is of size i bits. The prefix of a group is the binary representation of the first member of that group. When moving from group  $A_i$  to group  $A_{i+1}$ , the length of the code words increases by two bits, one for the prefix and the other for the tail. Runs of length i are mapped to

Figure 2.10: Structure of the decoder used in the Golomb coding technique.

group  $A_j$ , where  $j = \lceil \log_2(i+3) \rceil - 1$ . The size of the  $i^{th}$  group is equal to  $2^i$ . The FDR code for the first three groups is shown in Table 2.4.

The FDR technique was extended in [19] to encode both runs of 0's and 1's by adding an extra bit to the begging of a codeword to indicate the type of run. If the bit is 0, this indicates that the codeword is encoding a run of 0's, otherwise it

| Group | Run-Length | e 2.4: FDR code.<br>Group Prefix | Tail | Codeword |

|-------|------------|----------------------------------|------|----------|

| $A_1$ | 0          | 0                                | 0    | 00       |

|       | 1          |                                  | 1    | 01       |

|       | 2          |                                  | 00   | 1000     |

| $A_2$ | 3          | 10                               | 01   | 1001     |

|       | 4          |                                  | 10   | 1010     |

|       | 5          |                                  | 11   | 1011     |

|       | 6          |                                  | 000  | 110000   |

|       | 7          |                                  | 001  | 110001   |

|       | 8          |                                  | 010  | 110010   |

| $A_3$ | 9          | 110                              | 011  | 110011   |

|       | 10         |                                  | 100  | 110100   |

|       | 11         |                                  | 101  | 110101   |

|       | 12         |                                  | 110  | 110110   |

|       | 13         |                                  | 111  | 110111   |

encodes a run of 1's. This code, called Extended FDR (FDR), is shown in Table 2.5. As with the FDR code, in this code when moving from group  $A_i$  to group  $A_{i+1}$ , the length of codewords increases by two bits, one for the prefix and the other for the tail. Runs of length i are mapped to group  $A_j$ , where  $j = \lceil \log_2(i+2) \rceil - 1$ .

If we apply the EFDR on the test  $T = \{01100011111111000000001\}$ , we find that it contains 5 runs of 0's and 5 runs of 1's. This can be encode as  $T_{EFDR} = \{000\ 100\ 001\ 11011\ 0110000\}$ , which contains 21 bits. Obviously, for this example EFDR is performing better than the FDR code.

#### 2.1.3 Statistical Coding

Statistical coding methods minimize the average length of a codeword by assigning short codewords to frequently occurring patterns, while assigning longer codewords

|         | Table 2.5: Extended FDR code. |        |      |             |             |  |  |

|---------|-------------------------------|--------|------|-------------|-------------|--|--|

| Group   | Run                           | Group  | Tail | Codeword    | Codeword    |  |  |

| <u></u> | Length                        | Prefix |      | Runs of 0's | Runs of 1's |  |  |

| $A_1$   | 1                             | 0      | 0    | 000         | 100         |  |  |

|         | 2                             |        | 1    | 001         | 101         |  |  |

|         | 3                             |        | 00   | 01000       | 11000       |  |  |

| $A_2$   | 4                             | 10     | 01   | 01001       | 11001       |  |  |

|         | 5                             |        | 10   | 01010       | 11010       |  |  |

|         | 6                             |        | 11   | 01011       | 11011       |  |  |

|         | 7                             |        | 000  | 0110000     | 1110000     |  |  |

|         | 8                             |        | 001  | 0110001     | 1110001     |  |  |

|         | 9                             |        | 010  | 0110010     | 1110010     |  |  |

| $A_3$   | 10                            | 110    | 011  | 0110011     | 1110011     |  |  |

|         | 11                            |        | 100  | 0110100     | 1110100     |  |  |

|         | 12                            |        | 101  | 0110101     | 1110101     |  |  |

|         | 13                            |        | 110  | 0110110     | 1110110     |  |  |

|         | 14                            |        | 111  | 0110111     | 1110111     |  |  |

to less frequently occurring patterns. Examples of statistical encoding methods include Huffman coding, Shannon-Fano coding, and Lempel-Ziv coding [21, 22, 23].

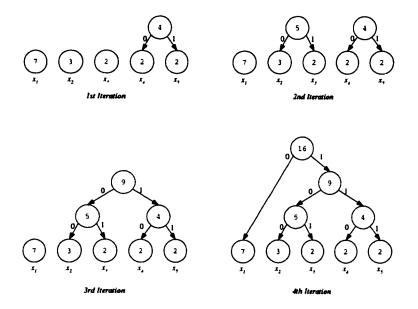

The scheme proposed in [8] uses Huffman coding to compress the test patterns in a test set  $T_D$ . It starts by computing the frequency (number of occurrences) of every unique test pattern in  $T_D$ . Then, it builds a Huffman tree out of these test patterns. The edges of the Huffman tree are labeled either with 0 or 1, while every leaf in the tree represents one unique pattern. The codeword of every unique pattern is obtained by traversing the path from the root to the corresponding leaf noting the sequence of 0's and 1's along the edges of this path.

Figure 2.11 illustrates the procedure for constructing the Huffman tree for a test set with five unique patterns  $x_1$ ,  $x_2$ ,  $x_3$ ,  $x_4$ , and  $x_5$  having frequencies of occurrence

Figure 2.11: Construction of a Huffman tree.

$f(x_1) = 7$ ,  $f(x_2) = 3$ ,  $f(x_3) = 2$ ,  $f(x_4) = 2$ , and  $f(x_5) = 2$ . The procedure iteratively selects two nods  $v_1$  and  $v_2$  with the lowest frequencies, and generates a parent node v for  $v_1$  and  $v_2$ . The edges  $(v, v_1)$  and  $(v, v_2)$  are labelled 0 and 1 respectively, and the node v is assigned the frequency  $f(v) = f(v_1) + f(v_2)$ . The codewords are obtained, as explained previously, by traversing the tree from the root to every leaf. Thus, the codewords for  $x_1, x_2, x_3, x_4$ , and  $x_5$  are 0, 100, 101, 110, and 111 respectively.

The encoded test set  $T_E$  is stored in the tester's memory, and is read out one bit at a time during test application.  $T_E$  can be decoded using a simple finite-state-machine (FSM) with n-1 states, where n is the number of leaves in the corresponding Huffman tree.

## 2.2 Compaction Techniques

Test set compaction is the process of reducing the length of a test set while achieving the desired fault coverage. Test compaction procedures can be classified into two categories: dynamic compaction and static compaction. Dynamic compaction procedures try to reduce the length of the test set during the generation of test vectors. Static compaction, on the other hand, performs compaction after the generation process. Hence, it does not require any modification to the test generation procedures. In addition to that, static compaction can be used after dynamic compaction, to further reduce the length of the test sequence [24].

In testing sequential circuits the order in which a test sequence is applied to the CUT is critical and can't be altered. This complicates the issue of compacting test data for sequential circuits than that for combinational circuits because any technique based on reordering of test vectors can't be applied here.

In this section we will review some of the static compaction procedures proposed for sequential circuits (dynamic compaction is out of the scope of our work).

# 2.2.1 Compaction by Overlapping Self-Initializing Test Sequences

In a combinational circuit, two test vectors are compatible if they do not specify opposite values for any primary input (PI). Two compatible test vectors  $t_i$  and  $t_j$

can be combined into one test  $t_{ij} = t_i \cap t_j$  using the intersection operation defined below.

Since the order of applying test vectors in combinational circuits is not important, test vectors can be compacted in any order. However, this is not the case with sequential circuits where the memory elements must be set to a specific state in order to excite, propagate or detect certain fault(s). A test sequence (with a strict order) is used to set the memory elements in the required state. Hence, two patterns can't be compacted arbitrary.

Self-initializing test sequence: In a test set containing self-initializing sequences, any test sequence does not depend on the state at which the sequential circuit arrives due to the application of previous sequences. Thus, the set of test sequences may be applied in any order without affecting the fault coverage. Such test sequences can be overlapped as long as they are compatible with each other, and the order of test vectors in each test sequence is preserved.

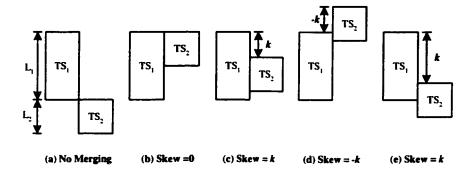

Compatibility of a test sequences: Consider two test sequences  $T_1$  and  $T_2$  of lengths  $l_1$  and  $l_2$  respectively, and  $l_1 \geq l_2$ . Originally the total test length due to  $T_1$  and  $T_2$  is  $l_1 + l_2$  as shown in Figure 2.12 (a). There are four ways in which  $T_2$  can be skewed from the start of  $T_1$  as shown in Figure 2.12 (b)-(e). In the first

Figure 2.12: Merging of two test sequences.

group, the two test sequences are aligned with each other such that they start at the same time (skew = 0). These two sequences will be compatible if the  $i^{th}$  vector in  $T_1$  is compatible with the  $i^{th}$  vector in  $T_2$  for  $(i = 1, 2, ..., l_2)$ . In the second group, the two sequences will be compatible if every vector in  $T_2$  is compatible with its corresponding vector in  $T_1$  (note that the  $1^{st}$  vector in  $T_2$  corresponds to the  $k^{th}$  vector  $T_1$ ). The reduction in total test length in this case is  $l_2$ . The compatibility of the test sequences in the third and fourth groups can be handled in a similar manner, where the reductions in the total test length due to compaction are  $(l_2 - k)$  and  $(l_1 - k)$  respectively.

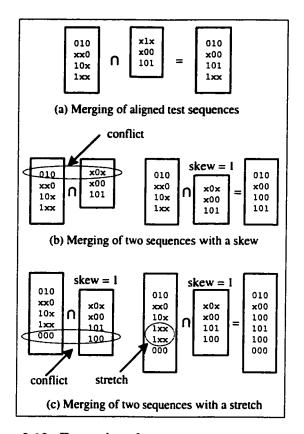

In [14], three algorithms were given to merge self-initializing test sequences. The first algorithm merges aligned test sequences as shown in Figure 2.13 (a). If aligning two sequences will result in a conflict between one or more vectors, a second algorithm is used to merge two sequences with a skew as shown in Figure 2.13 (b). The third algorithm improves the compatibility of test sequences using stretching. A sequence is stretched if some of its vectors are repeated several times without

Figure 2.13: Examples of merging two test sequences.

changing their order. For example the sequence (101x, 1x01, 111x) can be replaced by (101x, 1x01, 1x01, 111x). This will add one more degree of freedom to the process of compaction as shown in Figure 2.13 (c). Merging two test sequences using the last two algorithms may affect the fault coverage. Therefore, a fault simulation step is performed after the merging process.

# 2.2.2 Compaction Based on Insertion, Omission, and Selection

Three compaction algorithms were proposed in [15]. These algorithms are insertion, omission and selection. The following definitions and notations will be used to describe these algorithms.

- T[i] is the  $i^{th}$  test vector in the test sequence T.

- $T[u_i, u_k]$  is a subsequence of T between the two time units  $u_i$  and  $u_k$ .

- $S_i$  is the state of the fault-free circuit at time  $u_i$ .

- $S_i^f$  is the state of the faulty circuit at time unit  $u_i$  for some fault f.

- The effective test length of T,  $L_{eff}$ , is the minimum length of a subsequence of T that starts at time 0 and include the detection time of every detected fault.

#### Compaction Based on Insertion

Consider a fault f detected at time unit  $u_d$  by the test vector T[d]. If there exist two time units  $u_j$  and  $u_k$  such that  $u_j < u_k \le u_d$  and  $S_j/S_j^f = S_k/S_k^f$ , then f can be detected earlier by duplicating and inserting the subsequence  $T[u_k, u_d]$  at  $u_j$ . The insertion operation increases the total length of the test sequence, however, it reduces the effective length  $L_{eff}$  by reducing the highest detection time. The insertion

Table 2.6: The test sequence of Example 2.1.

|   | i    | 0    | 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8    | 9    |

|---|------|------|------|------|------|------|------|------|------|------|------|

| Ī | T[i] | 0011 | 1101 | 0001 | 0011 | 1110 | 1011 | 0001 | 0010 | 0000 | 0110 |

Table 2.7: The fault detection of the test sequence in Example 2.1.

| i                      | 0 | 1          | 2 | 3     | 4               | 5     | 6 | 7                  | 8 | 9        |

|------------------------|---|------------|---|-------|-----------------|-------|---|--------------------|---|----------|

| <b>Detected Faults</b> | φ | $f_1, f_2$ | φ | $f_3$ | $f_4, f_5, f_6$ | $f_7$ | φ | $f_8, f_9, f_{10}$ | φ | $f_{11}$ |

operation is applied iteratively, until no additional improvements in effective test length or in the fault coverage can be obtained. The following example demonstrates the insertion operation.

Example 2.1: Consider the test sequence shown in Table 2.6. The corresponding fault detection of this test sequence is shown in Table 2.7. Assume that the combined fault-free/faulty states are identical at times  $u_7$  and  $u_8$ . Then,  $f_{11}$  can be detected at earlier time by duplicating and inserting T[8,9]=(0000, 0110) at  $u_7$  as shown in Table 2.8. After inserting the subsequence, fault simulation is performed to see the effect of the insertion operation on the faults detected in time units following  $u_7$ . Table 2.9 shows a possible fault detection due to the insertion operation, where the detection time of  $f_{11}$  has been shifted from  $u_9$  to  $u_8$ .

Table 2.8: The test sequence of Example 2.1 after insertion.

| i    | 0    | 1    | 2    | 3    | 4    | 5    |

|------|------|------|------|------|------|------|

| T[i] | 0011 | 1101 | 0001 | 0011 | 1110 | 1011 |

|      |      |      |      |      |      |      |

| i    | 6    | 7    | 8    | 9    | 10   | 11   |

Table 2.9: The fault detection of Example 2.1 after insertion.

| i                      | 0 | 1          | 2 | 3     | 4                          | 5     | 6 | 7          | 8                | 9 |

|------------------------|---|------------|---|-------|----------------------------|-------|---|------------|------------------|---|

| <b>Detected Faults</b> | φ | $f_1, f_2$ | φ | $f_3$ | $f_4, f_5, \overline{f_6}$ | $f_7$ | φ | $f_8, f_9$ | $f_{10}, f_{11}$ | φ |

#### **Compaction Based on Omission**

This algorithm is based on the omission of redundant test vectors from the test sequence. The omission of a test vector  $t_i$  at time unit  $u_i$  may affect faults detected in the time units following  $u_i$ . Also, it may result in detecting new faults. Hence, a fault simulation is performed after every omission operation to check the fault coverage. Test vectors are considered for omission in the order in which they appear in the test sequence. After omitting a test vector  $t_i$ , a fault simulation is performed for all faults detected in time units following  $u_i$  and for all undetected faults. If the fault coverage after omission is not lower than the fault coverage before omission, the change is accepted, otherwise,  $t_i$  is restored.

#### **Compaction Based on Selection**

This technique works as follows. For every detected fault f, it first collects all subsequences that detect the fault f, such that each subsequence starts from unspecified states (i.e., all memory elements set to X's). Next, it uses a covering procedure to select a minimal subset of the collected subsequences that detect all the faults detected by the original test set. During this selection phase, a newly selected subsequence is combined with the previously selected subsequences in the order by which they

appear in the original test set. Then the new sequence is simulated to identify the faults that still need to be detected. This can expressed by means of the following example.

Example 2.2: Assume that we are given a circuit with 8 test vectors ( $t_1$  to  $t_8$ ) which detect 10 faults ( $f_1$  to  $f_{10}$ ). First, the circuit is fault simulated starting from every test vector with all states set to X's. Thus, the circuit is simulated starting from  $t_1$  up to  $t_8$ , then from  $t_2$  up to  $t_8$ , and so on. Suppose that the fault detections shown in Table 2.10 represent the result of the above fault simulations. From this table we can obtain the subsequences that detect a given fault. For example, the fault  $f_1$  is detected in  $t_3$  of the first fault simulation. Thus, it can be detected by any one of the subsequences (1,3), (1,4), (1,5), (1,6), (1,7) and (1,8). Table 2.11 shows all the subsequences that detect every one of the 10 faults.

Next, a minimal subset of these subsequences is selected to detect all the faults detected by the original test set as follows. Starting from  $f_1$ , we find that this fault can be detected by any one of the subsequences (1,3), (1,4), (1,5), (1,6), (1,7) and (1,8). However, the subsequence (1,3) is selected because it is the shortest among the 6 subsequences. Notice that this sequence detects the faults  $f_2$ ,  $f_3$ , and  $f_5$  as well. Therefore, no need to consider these faults in the next selection. The next fault to be consider is  $f_4$  which is detected by 7 subsequences. The shortest sequence among these subsequences is (7,8). This subsequence is combined with the subsequence (1,3) to form the sequence  $T' = \{t_1, t_2, t_3, t_7, t_8\}$ . Notice the new

sequence may detect additional faults other than those detected by the individual subsequences. Therefore, we should fault simulate the circuit under the new test sequence before selecting a new subsequence.

Suppose that after simulating the circuit under the test sequence T' we found that the faults  $f_1$ ,  $f_2$ ,  $f_3$ ,  $f_5$ ,  $f_9$  and  $f_{10}$  are detected (i.e.,  $f_4$  is missing). In this case,  $f_4$  is considered again and the next choice is the subsequence (6,8). This subsequence is combined with T' to form the test sequence  $T'' = \{t_1, t_2, t_3, t_6, t_7, t_8\}$ . Then, the circuit is fault simulated under the new test sequence. Suppose that T'' detects all the 10 faults (i.e., the fault  $f_6$  is accidently detected). In this case, the selection process stops and the compacted test set will be in T''.

#### 2.2.3 Compaction Based on Vector Restoration

For many test sequences considered in [15], the test length after compaction is less than half of the original test length. This suggests that it may be faster to decide which test vectors must be restored in the test sequence in order to maintain the fault coverage, instead of deciding on the test vectors that may be omitted. The technique in [16] restores test vectors for each fault starting from the hardest-to-detect to the easiest. In this way, some faults can be detected by sequences of other faults. The technique is illustrated by the following example.

Example 2.3: Consider the fault detection shown in Table 2.12. The technique starts by omitting (almost) all test vectors in the test sequence (test vectors that

| Table 2.10:                                  | Fault detection         | n of Example 2.2.                 |

|----------------------------------------------|-------------------------|-----------------------------------|

| Starting From                                | TV(s)                   | Detected Faults                   |

| $t_1$                                        | $t_1, t_2$              | φ                                 |

| ĺ                                            | $t_3$                   | $f_1, f_2, f_3, f_5$              |

|                                              | $t_4, t_5, t_6$         | $\phi$                            |

|                                              | $t_7$                   | $f_6$                             |

|                                              | $t_8$                   | $f_4, f_7, f_8, f_9, f_{10}$      |

| $t_2$                                        | $t_2, t_3, \ldots, t_7$ | $\phi$                            |

|                                              | $t_8$                   | $f_4, f_6, f_7, f_8, f_9, f_{10}$ |

| $t_3$                                        | $t_3, t_4, \ldots, t_7$ | $\phi$                            |

|                                              | $t_8$                   | $f_4, f_6, f_7, f_8, f_9, f_{10}$ |

| $t_4$                                        | $t_4, t_5, \ldots, t_7$ | $\phi$                            |

|                                              | $t_8$                   | $f_4, f_6, f_7, f_8, f_9, f_{10}$ |

| $t_5$                                        | $t_5, t_6, t_7$         | $ \phi $                          |

| <u>.                                    </u> | $t_8$                   | $f_4, f_6, f_7, f_8, f_9, f_{10}$ |

| $t_6$                                        | $t_6, t_7$              | $\phi$                            |

|                                              | $t_8$                   | $f_4, f_7, f_8, f_9, f_{10}$      |

| $t_7$                                        | $t_7$                   | $\phi$                            |

|                                              | $t_8$                   | $f_4, f_9, f_{10}$                |

| $t_8$                                        | $t_8$                   | $\phi$                            |

Table 2.11: Test subsequences of Example 2.2.

| Fault    | Subsequences                                          |

|----------|-------------------------------------------------------|

| $f_1$    | (1,3) $(1,4)$ $(1,5)$ $(1,6)$ $(1,7)$ $(1,8)$         |

| $f_2$    | (1,3) (1,4) (1,5) (1,6) (1,7) (1,8)                   |

| $f_3$    | (1,3) (1,4) (1,5) (1,6) (1,7) (1,8)                   |

| $f_4$    | (1,8) (2,8) (3,8) (4,8) (5,8) (6,8) (7,8)             |

| $f_5$    | (1,3) $(1,4)$ $(1,5)$ $(1,6)$ $(1,7)$ $(1,8)$         |

| $f_6$    | (1,7) (1,8) (2,8) (3,8) (4,8) (5,8)                   |

| $f_7$    | (1,8) (2,8) (3,8) (4,8) (5,8) (6,8)                   |

| $f_8$    | (1,8) $(2,8)$ $(3,8)$ $(4,8)$ $(5,8)$ $(6,8)$ $(7,8)$ |

| $f_9$    | (1,8) (2,8) (3,8) (4,8) (5,8) (6,8) (7,8)             |

| $f_{10}$ | (1,8) (2,8) (3,8) (4,8) (5,8) (6,8) (7,8)             |

Table 2.12: Fault detection of Example 2.3.

| Fault | Subsequence to detect the fault                 |

|-------|-------------------------------------------------|

| $f_1$ | $(t_1,t_3)$                                     |

| $f_2$ | $(t_2,t_5)$                                     |

| $f_3$ | $(t_3,t_{12})$                                  |

| $f_4$ | $(t_{11}, t_{16}) \text{ or } (t_{18}, t_{20})$ |

| $f_5$ | $(t_{17}, t_{20})$                              |

synchronize the circuit by taking it from an unspecified state to a fully specified one are not omitted). Starting from the last detected fault (i.e.,  $f_5$ ), the algorithm restores test vectors one at a time until the required fault is detected. For instance,  $t_{20}$  is simulated first and since it does not detect  $f_5$ ,  $t_{19}$  is added to the sequence. Now, the sequence  $(t_{19}, t_{20})$  is simulated, and so on, until the sequence  $(t_{17}, t_{20})$  is restored. Notice that any fault that is detected by this sequence is dropped from the current fault list. For example,  $f_4$  is removed from the list since it is detected by  $(t_{18}, t_{20})$ . After restoring  $f_5$ , the algorithm starts from the last yet-undetected fault and repeats the process until all detected faults are covered.

We can speed-up the process of vector restoration in the above technique by considering several faults in parallel during the restoration process. In [25], faults are grouped together according to their detection times by the original test sequence. Specifically, all the faults detected by the original test sequence at time unit  $u_i$  are considered together during the restoration process.

The restoration techniques we have seen so far restore the test vectors in the same order in which they appear in the original test sequence. For example, if the compacted test sequence is  $T_c = \{t_1, t_2, t_9\}$ , then the compacted test sequence after restoring  $t_8$  becomes  $T_c = \{t_1, t_2, t_8, t_9\}$ . Notice that in this example, the faults detected after restoring  $t_9$  may not be detected after restoring  $t_8$ . Thus, all faults detected at a certain test vector need to be resimulated when a new vector is restored into the compacted test sequence. The technique proposed in [26] avoids this problem by reversing the order of the vectors during restoration. In this technique, every time a subsequence of the original test sequence is restored to detect a subset of faults, the subsequence is placed at the end of the compacted test sequence  $(T_c)$ . In this way, a fault detected by  $T_c$  is guaranteed to remain detected by at the end of the compaction process.

#### 2.2.4 Compaction Based on Inert Subsequence Removal

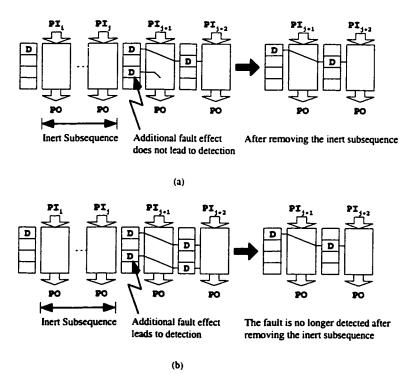

The technique proposed in [17] is based on the observation that test sequences traverse through a small set of states and some states are frequently revisited throughout the application of a test set. Subsequences that start and end on the same states may be removed if sufficient conditions are met. Before going over these conditions, the following two definitions are given to help in explaining the inert subsequence removal technique.

**Definition 2.1** A state-recurrence subsequence  $T_{rec}$  is a subsequence of test vectors such that the fault-free states reached at the beginning of  $T_{rec}$  and those reached at

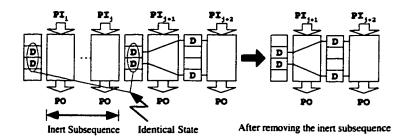

Figure 2.14: Subsequence removal (Criterion 1).

the end of it are identical.

**Definition 2.2** An inert recurrence subsequence  $T_{inert}$  is a state-recurrence subsequence such that no additional faults are detected within this subsequence.

Inert subsequences can be removed, in order to compact a test sequence, given that certain criteria are satisfied. These criteria are discussed below.

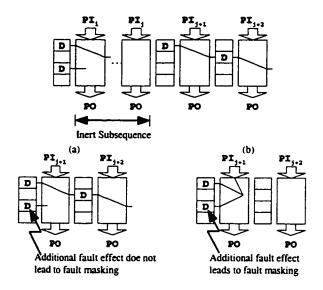

Criterion 1: Consider the situation in Figure 2.14. If the faulty state before and after the inert subsequence  $T_{inert}$  are identical for every undetected fault f that is activated by this subsequence, then  $T_{inert}$  can be removed without affecting the fault coverage.

Criterion 2: For an inert subsequence  $T_{inert}$ , if the faulty state after the subsequence covers the faulty state before the subsequence for every activated fault, and any additional fault effects propagated at the end of the subsequence do not lead to detection, then  $T_{inert}$  can be removed. This criterion is illustrated in Figure 2.15. Criterion 3: For an inert subsequence  $T_{inert}$ , if the faulty state before the subse-

quence covers the faulty state after the subsequence and the additional fault effects

Figure 2.15: Subsequence removal (Criterion 2).

Figure 2.16: Subsequence removal (Criterion 3).

propagated before the subsequence do not cause fault-masking in time frames following the subsequence, then  $T_{inert}$  can be removed. This situation is shown in Figure 2.16.

Criterion 4: For an inert subsequence  $T_{inert}$ , if neither of the faulty states before and after the subsequence cover the other, then conditions imposed on activated faults in both Criterion 2 and Criterion 3 must be satisfied in order to remove  $T_{inert}$ .

The above criteria can identify subsequences that may be removed in order to compact a given test sequence. However, this technique will not be able to compact test sequences that do not contain state-recurrence subsequences. In such cases, state relaxation can be used to identify state-recurrence subsequences that may be removed. For example, assume that the test set T transfer the circuit through the states  $S_1 = 10110$ ,  $S_2 = 00100$ ,  $S_3 = 01110$ ,  $S_4 = 00110$  and  $S_5 = 11001$  without

repeating any state. It is possible that not all specified bits in  $S_4$  are necessary to reach  $S_5$ . Therefore, if  $S_4$  can be relaxed to "X0110", then there exists a state-recurrence subsequence between  $S_1$  and  $S_4$ . The technique proposed in [27] extends the subsequence removal technique using state relaxation to identify more cycles in a test set. In state relaxation, logic simulation is performed for all test vectors in the test set. For every test vector, the state of the circuit (i.e., values of the memory-elements) is analyzed to identify those bits that have no effect on the next state or primary outputs, and relax them. This process is illustrated in the following example.

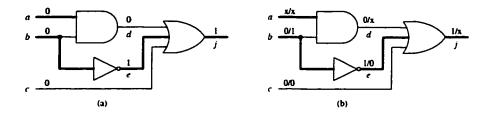

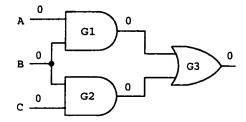

Example 2.4: Consider the circuit shown in Figure 2.17. This circuit has two primary inputs (A, B), one primary output (G5), and three memory-elements (G7, G8, G9). If the initial state of the circuit is (G7, G8, G9) = (0, 0, 1) and the input is (A, B) = (1, 0), then the output circuit becomes 0 and the circuit is transferred to the state (G7, G8, G9) = (0, 1, 1). Notice that a fault effect on G7 can't be propagated to the primary output or the memory-elements because of the controlling value A = 1. Therefore, the value on G7 can be relaxed to 'X'. Similarly, G8 can be relaxed without affecting the primary output or the memory-elements because of the the controlling value B = 0. Thus the initial state can be relaxed to (G7, G8, G9) = (X, X, 1).

Figure 2.17: Circuit of Example 2.4.

## 2.3 Test-Pattern Relaxation Techniques for Com-

### binational Circuits

In this section, we discuss two test-pattern relaxation techniques proposed for combinational circuits [28, 29]. The main idea of both techniques is to determine logic values in the fully-specified test set that are necessary to cover (i.e., detect) all faults which are detectable by this test set. Unnecessary logic values are set to X's. Before we go into details of the two techniques, we define some of the terminologies used in each technique. Given a test set T, if any fault detected by test vector t in T is detected by at least one test vector in  $T - \{t\}$ , t is called redundant test vector. If a fault, f, is detected by t in t, but not detected by any test vector in t is called an essential fault of t. To indicate that a line t is stuck-at value t, the notation t is used. The notation t indicates that the fault-free value of line t is t, and the faulty value of line t is t.

#### Relaxation Using Implication/Justification Procedures

The technique proposed in [28] uses fault simulation and implication/justification procedures similar to those used by ATPG algorithms. The technique consists of three phases. The first phase starts by fault-simulating the circuit under the original test set to determine essential faults of every test vector. Then, implication/justification procedures are used to specify logic values necessary to detect these essential faults. The resulting relaxed test set is still an intermediate test set. In the second phase, the circuit is fault-simulated under the intermediate test set. Then, implication/justification are used again to specify logic values necessary to detect any fault that is detected by the original test set but not detected by the intermediate test set. After all, if the second phase fails to detect any of the detectable faults, a more restricted implication/justification (call extended implication/justification) is used in third phase to specify logic values necessary to detect all faults missed by the previous phases. The general behavior of this technique is illustrated by the following example.

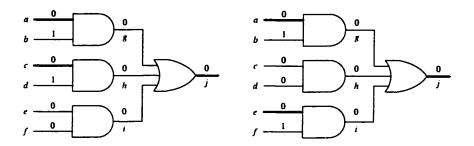

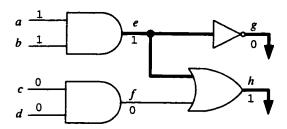

Example 2.5: Consider the combinational circuit shown in Figure 2.18 under the test set  $abcdef = \{010100, 010001\}$ . The first test vector,  $t_1$ , can detect three faults: a/1, c/1 and j/1. The second test vector,  $t_2$ , can detect the fault e/1 in addition to the faults a/1 and j/1. Therefore, c/1 is considered as an essential fault for  $t_1$ , while e/1 is an essential fault for  $t_2$ .