### The Translinear Current Controlled Conveyor and its Applications

by

Noman Ali Tassaduq

A Thesis Presented to the

# FACULTY OF THE COLLEGE OF GRADUATE STUDIES KING FAHD UNIVERSITY OF PETROLEUM & MINERALS DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

### **MASTER OF SCIENCE**

In

### **ELECTRICAL ENGINEERING**

May, 1998

#### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality  $6^{\circ} \times 9^{\circ}$  black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor MI 48106-1346 USA 313/761-4700 800/521-0600

# NOTE TO USERS

The original manuscript received by UMI contains indistinct, slanted and or light print. All efforts were made to acquire the highest quality manuscript from the author or school. Microfilmed as received.

This reproduction is the best copy available

# UMI

### THE TRANSLINEAR CURRENT CONTROLLED CONVEYOR AND ITS APPLICATIONS

BY

### NOMAN ALI TASADDUQ

A Thesis Presented to the

FACULTY OF THE COLLEGE OF GRADUATE STUDIES

KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

# MASTER OF SCIENCE

**ELECTRICAL ENGINEERING**

**MAY 1998**

**UMI Number: 1390786**

UMI Microform 1390786 Copyright 1998, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

### UMI

300 North Zeeb Road Ann Arbor, MI 48103

### THE TRANSLINEAR CURRENT CONTROLLED CONVEYOR AND ITS APPLICATIONS

NOMAN ALI TASADDUQ

**ELECTRICAL ENGINEERING**

MAY 1998

# KING FAHD UNIVERSITY OF PETROLEUM AND MINERALS DHAHRAN, SAUDI ARABIA

This thesis, written by

### Noman Ali Tasadduq

under the direction of his thesis advisor, and approved by his thesis committee, has been presented to and accepted by the Dean, College of Graduate Studies, in partial fulfillment of the requirements for the degree of

### MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

Thesis Committee:

Chairman (Prof. M. T. Abuelma'atti)

Member (Dr. M. A. Al-Sunaidi)

Member (Dr. Chedly B. Yahya)

Member (Dr. Z. J. Al-Saati)

Dr. Samir A. Al-Baiyat Department Chairman

Dr. Abdallah M. Al-Shehri Dean, College of Graduate Studies

Date: 2016/98

#### Acknowledgments

Praise be to the Lord of the World, the Almighty for having guided me at every stage of my life.

I am grateful to my thesis advisor Prof. M. T. Abuelma'atti for his continuous support and guidance throughout the work. I would also like to place on record my appreciation for the cooperation and guidance extended by my committee members. Dr. Z. J. Al-Saati, Dr. Chedly B. Yahya and Dr. M. A. Al-Sunaidi.

My thanks to the department chairman Dr. Samir A. Al-Baiyat for providing me every help and facility to carry out this research. I am grateful to all my friends, both from within and outside the department, who made my stay at KFUPM a pleasant and memorable one.

I recall with deep gratitude and respect the debt I owe to my mother, uncle Mr. Sirajuddin and brothers Imran and Rizwan for their unfathomable love, prays, support and encouragement throughout my studies. May Allah bless them and may they live long for me.

# Contents

|   | Ack                | nowle  | dgements                                           | i  |

|---|--------------------|--------|----------------------------------------------------|----|

|   | List of Figures    |        |                                                    | v  |

|   | Abstract (English) |        |                                                    | ix |

|   | Abs                | tract  | (Arabic)                                           | x  |

| 1 | INT                | ROD    | UCTION                                             | 1  |

|   | 1.1                | Curre  | nt Conveyor                                        | 2  |

|   | 1.2                | Mono   | lithic Implementation of Current Conveyors         | 4  |

|   |                    | 1.2.1  | Power Supply Current Sensing Technique             | 5  |

|   |                    | 1.2.2  | Translinear Cell                                   | 8  |

|   | 1.3                | Effect | of Internal Resistance in Current Conveyors (CCII) | 11 |

|   |                    | 1.3.1  | Multiple input single output (MISO) based circuit  | 11 |

|   | 1.4                | Curre  | nt Controlled Conveyor                             | 20 |

|   | 1.5                |        |                                                    | 27 |

|   |                    | 1.5.1  | Active-C Universal Filters                         | 28 |

|   |                    | 1.5.2  | Sinusoidal Oscillators                             | 28 |

|   |     | 1.5.3  | Impedance Simulation                    | 29  |

|---|-----|--------|-----------------------------------------|-----|

|   |     | 1.5.4  | Higher Order Filter Synthesis           | 29  |

|   | 1.6 | Proble | em Definition                           | 30  |

| 2 | FIL | TERS,  | OSCILLATOR AND IMPEDANCE SIMULATION     | 31  |

|   | 2.1 | Univer | rsal Second Order Filters               | 32  |

|   | 2.2 | Design | 1 Requirements                          | 33  |

|   | 2.3 | Propos | sed Circuits                            | 34  |

|   |     | 2.3.1  | Universal Filter 1                      | 34  |

|   |     | 2.3.2  | Universal Filter 2                      | 46  |

|   |     | 2.3.3  | Universal Filter 3                      | 49  |

|   |     | 2.3.4  | Universal Filter 4                      | 65  |

|   | 2.4 | SINUS  | SOIDAL OSCILLATORS                      | 68  |

|   |     | 2.4.1  | Design Requirements                     | 72  |

|   |     | 2.4.2  | Proposed Circuit                        | 73  |

|   |     | 2.4.3  | Simulation Results and Discussion       | 75  |

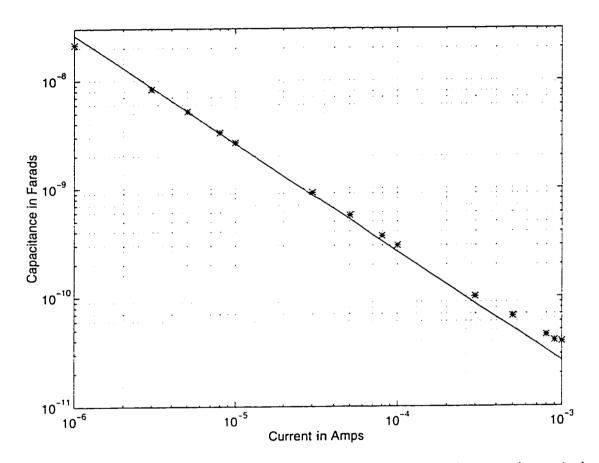

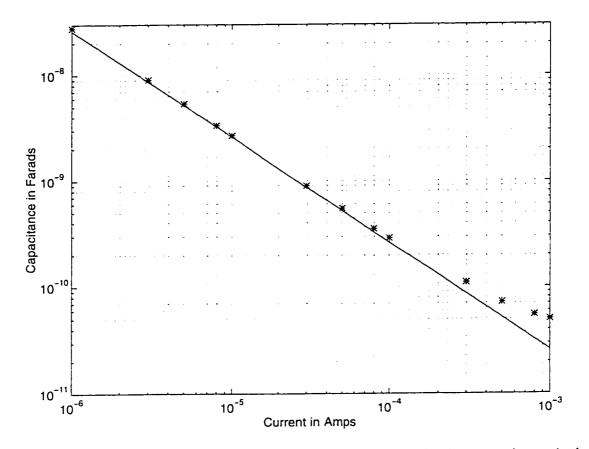

|   | 2.5 | Imped  | ance Simulation                         | 78  |

|   |     | 2.5.1  | Capacitance Multiplier and FDNR Element | 79  |

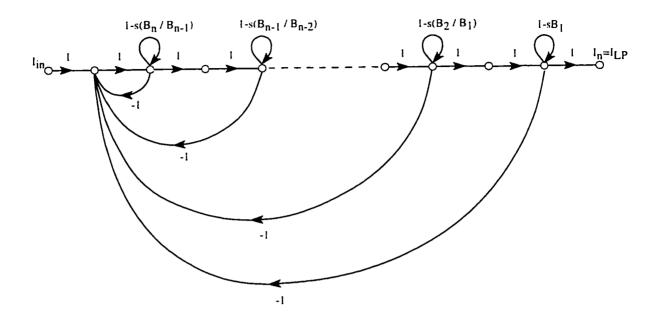

| 3 | Hig | her Or | der Filter Synthesis                    | 87  |

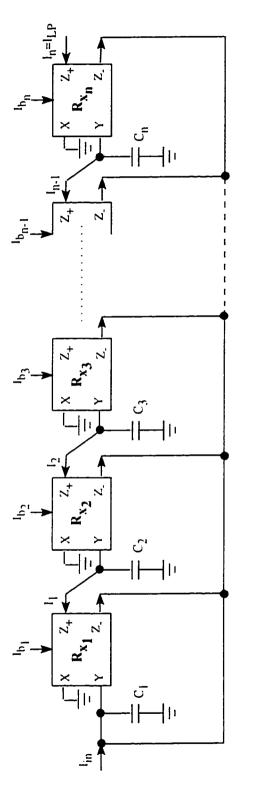

|   | 3.1 | Low P  | ass $n^{th}$ order Transfer Function    | 88  |

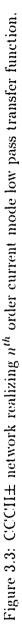

|   | 3.2 | Genera | al $n^{th}$ order Transfer Function     | 92  |

|   | 3.3 | Simula | ation Results and Discussion            | 97  |

| 4 | CO  | NCLU   | SION AND FUTURE WORK                    | 108 |

|   | 4.1 | Conclu | 1sion                                   | 108 |

| 4.2   | Future Work | 110 |

|-------|-------------|-----|

| Appen | ndix A      | 111 |

| Appen | ıdix B      | 115 |

| Bib   | liography   | 123 |

# List of Figures

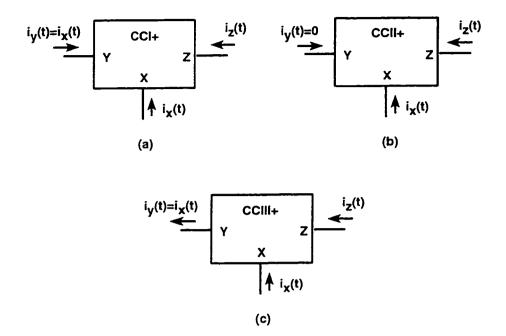

| 1.1  | Symbols of current conveyor                                              | 3  |

|------|--------------------------------------------------------------------------|----|

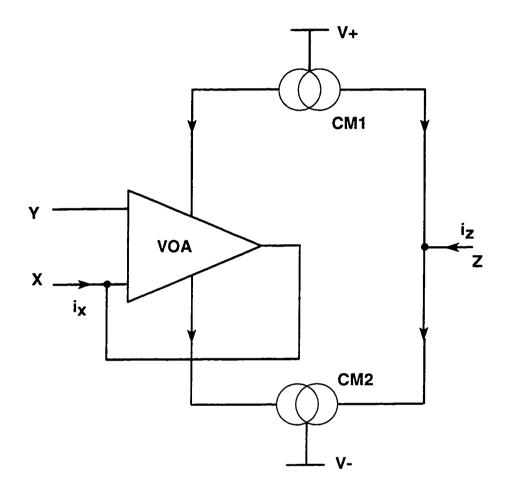

| 1.2  | Schematic of VOA based CCII+                                             | 6  |

| 1.3  | Schematic of VOA based CCII                                              | ī  |

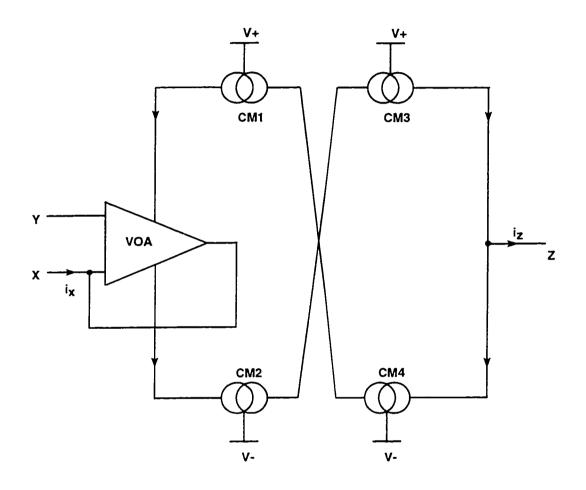

| 1.4  | Circuit diagram of translinear cell.                                     | 10 |

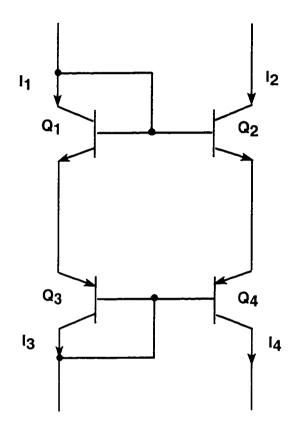

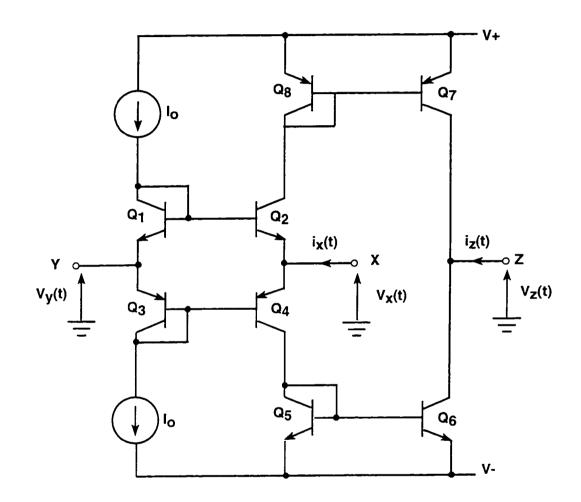

| 1.5  | Translinear Cell based CCII+                                             | 12 |

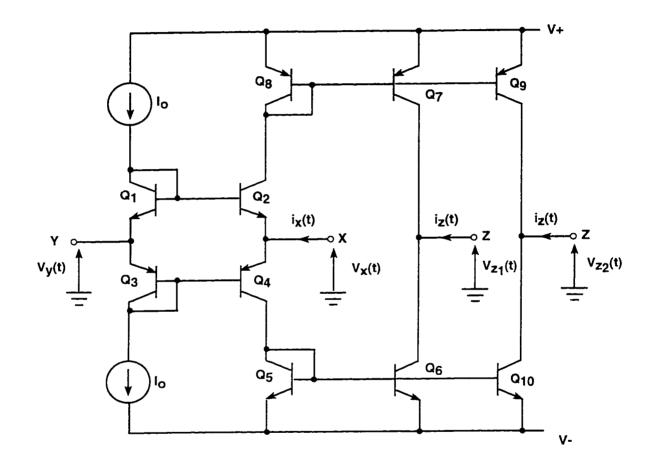

| 1.6  | Multiple Output Translinear Cell based CCII+                             | 13 |

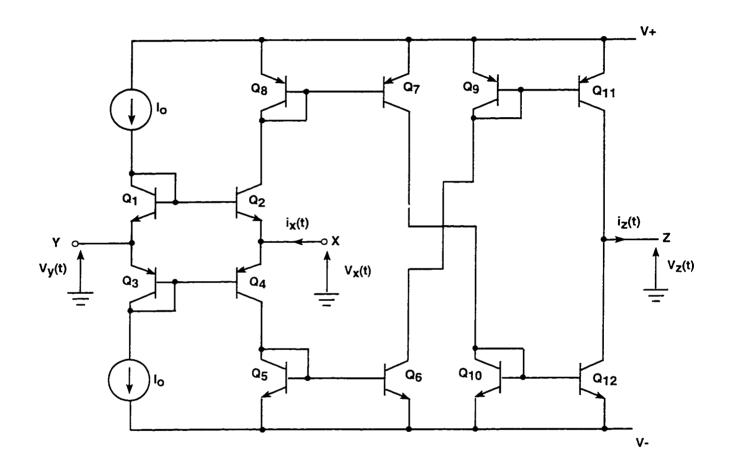

| 1.7  | Translinear Cell based CCII                                              | 14 |

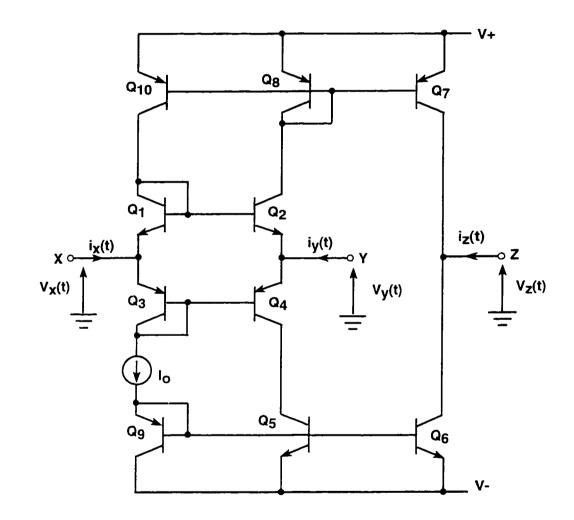

| 1.8  | Circuit diagram of CCI+                                                  | 15 |

| 1.9  | Multiple input single output CCII+ based filter                          | 16 |

| 1.10 | Experimental result of Figure 1.9 for lowpass filter.                    | 18 |

| 1.11 | Experimental result of Figure 1.9 for bandpass filter                    | 19 |

| 1.12 | Experimental result of Figure 1.9 for highpass filter without consid-    |    |

|      | ering internal resistance                                                | 21 |

| 1.13 | Experimental result of Figure 1.9 for highpass filter with the effect of |    |

|      | internal resistance                                                      | 22 |

| 1.14 | Circuit diagram of mixed translinear cell                                | 23 |

| 1.15 | Circuit diagram and symbol of current controlled conveyor                | 25 |

| 2.1  | CCCII based Universal second order filter-1.                                    | 35  |

|------|---------------------------------------------------------------------------------|-----|

| 2.2  | Simulation results of Figure 2.2 for lowpass filter                             | 39  |

| 2.3  | Simulation results of Figure 2.2 for highpass filter                            | 40  |

| 2.4  | Simulation results of Figure 2.2 for bandpass filter                            | -11 |

| 2.5  | Simulation results of Figure 2.2 for notch filter                               | 42  |

| 2.6  | Simulation results of Figure 2.2 for the gain of allpass filter                 | 43  |

| 2.7  | Simulation results of Figure 2.2 for the phase of all<br>pass filter $\ldots$ . | 44  |

| 2.8  | Simulation results of Figure 2.2 for the variable gain of bandpass filter       | 45  |

| 2.9  | CCCII based Universal second order filter-2                                     | 46  |

| 2.10 | ) Simulation results of Figure 2.9 for lowpass filter                           | 50  |

| 2.11 | Simulation results of Figure 2.9 for highpass filter                            | 51  |

| 2.12 | 2 Simulation results of Figure 2.9 for bandpass filter                          | 52  |

| 2.13 | Simulation results of Figure 2.9 for notch filter                               | 53  |

| 2.14 | Simulation results of Figure 2.9 for the gain of allpass filter                 | 54  |

| 2.15 | 5 Simulation results of Figure 2.9 for the phase of all pass filter $\ldots$ .  | 55  |

| 2.10 | Improved CCCII based Universal second order filter-3                            | 56  |

| 2.17 | Simulation results of Figure 2.16 for lowpass filter                            | 59  |

| 2.18 | Simulation results of Figure 2.16 for highpass filter                           | 60  |

| 2.19 | Simulation results of Figure 2.16 for bandpass filter                           | 61  |

| 2.20 | Simulation results of Figure 2.16 for notch filter                              | 62  |

| 2.21 | Simulation results of Figure 2.16 for the gain of all<br>pass filter $\ldots$ . | 63  |

| 2.22 | Simulation results of Figure 2.16 for the phase of allpass filter               | 64  |

| 2.23 | Multiple filter functions, CCCII based Universal second order filter-4.         | 67  |

| 2.24 | Simulation results of Figure 2.23 for bandpass, lowpass and highpass        |     |

|------|-----------------------------------------------------------------------------|-----|

|      | filter                                                                      | 69  |

| 2.25 | Simulation results of Figure 2.23 for lowpass notch and highpass notch      |     |

|      | filter                                                                      | 70  |

| 2.26 | Simulation results of Figure2.23 for the gain of allpass and notch filter   | 71  |

| 2.27 | Circuit diagram for proposed sinusoidal oscillator                          | 74  |

| 2.28 | Simulation results of the sinusoidal oscillation                            | 76  |

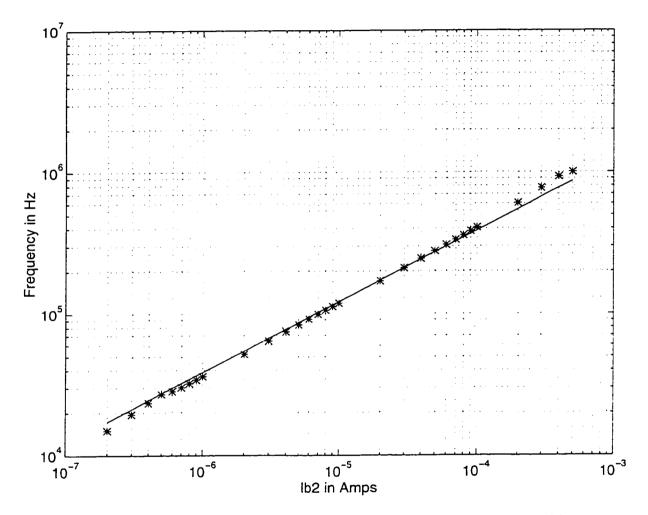

| 2.29 | Oscillation frequencies against bias current                                | 77  |

| 2.30 | CCCII+ based impedance simulator.                                           | 8() |

| 2.31 | Simulation result of grounded capacitance multiplier                        | 82  |

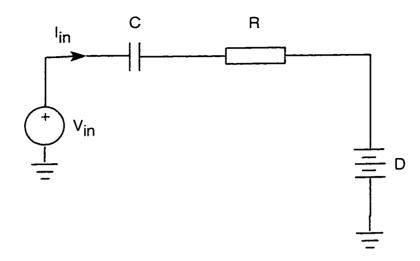

| 2.32 | Highpass filter using FDNR                                                  | 83  |

| 2.33 | Simulation result of highpass filter using FDNR                             | 84  |

| 2.34 | CCCII based floating capacitance simulator.                                 | 85  |

| 2.35 | Simulation result of floating capacitance multiplier                        | 86  |

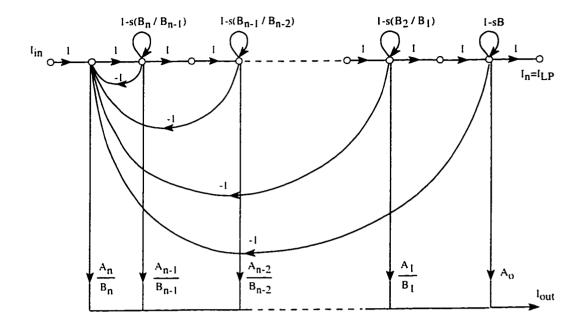

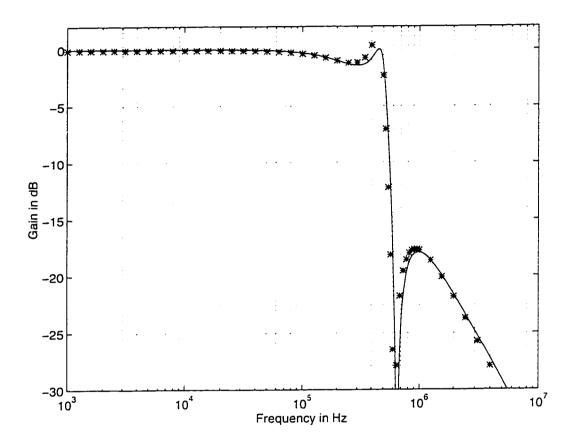

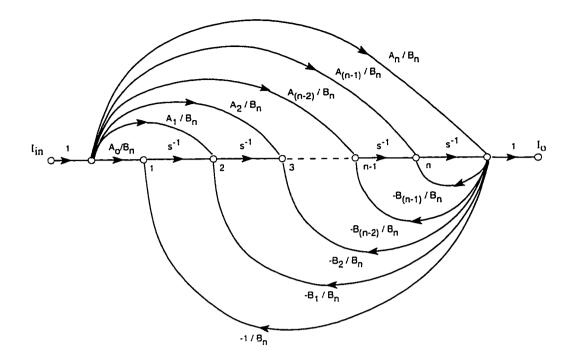

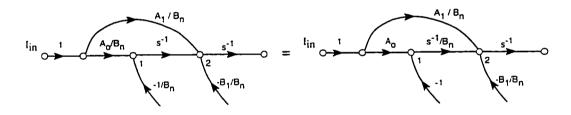

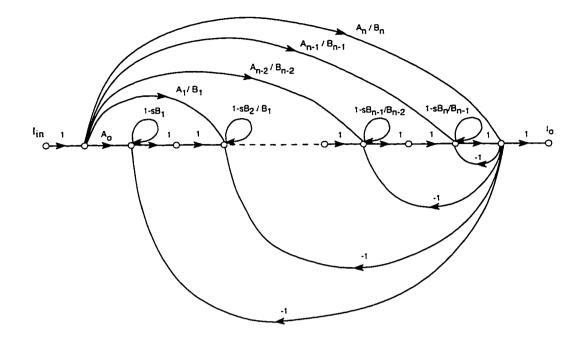

| 3.1  | $n^{th}$ order low pass signal flow graph                                   | 90  |

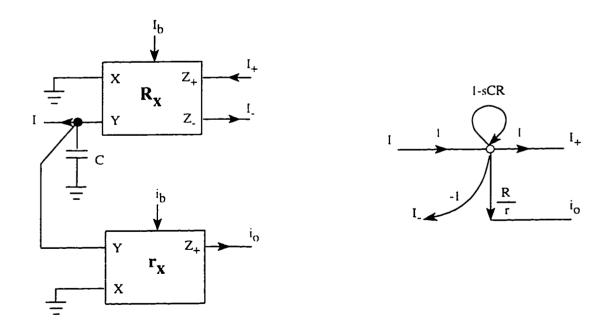

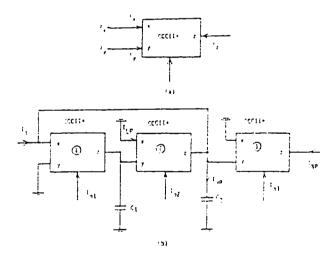

| 3.2  | Correspondence between subgraph and subcircuit for low pass function.       | 90  |

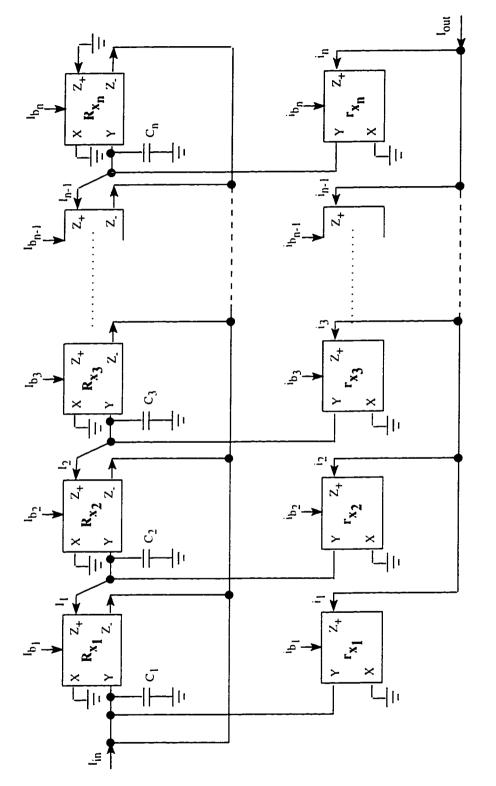

| 3.3  | CCCII $\pm$ network realizing $n^{th}$ order current mode low pass transfer |     |

|      | function.                                                                   | 91  |

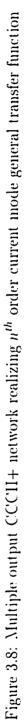

| 3.4  | Multiple output CCCII+ network realizing $n^{th}$ order current mode        |     |

|      | low pass transfer function                                                  | 93  |

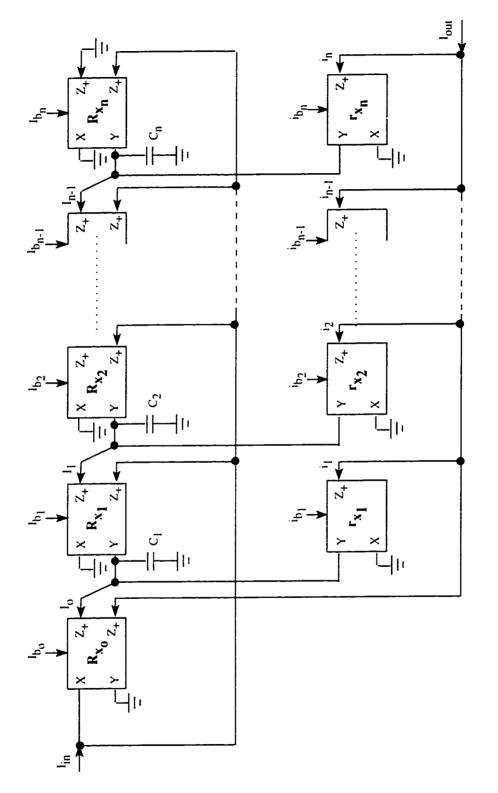

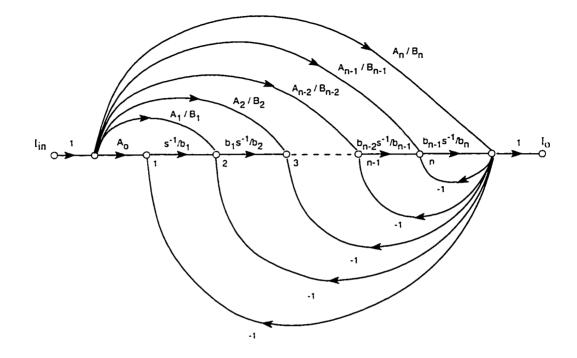

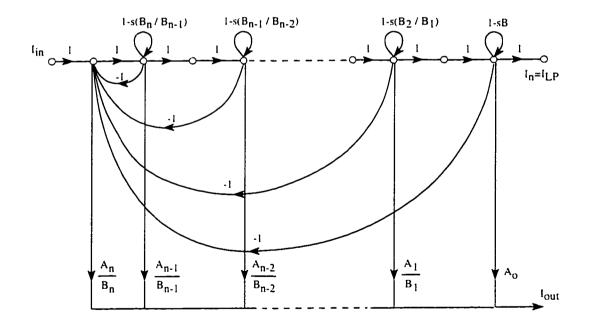

| 3.5  | $n^{th}$ order signal flow graph of general transfer function               | 95  |

| 3.6  | Correspondence between subgraph and subcircuit for general transfer         |     |

|      | function.                                                                   | 95  |

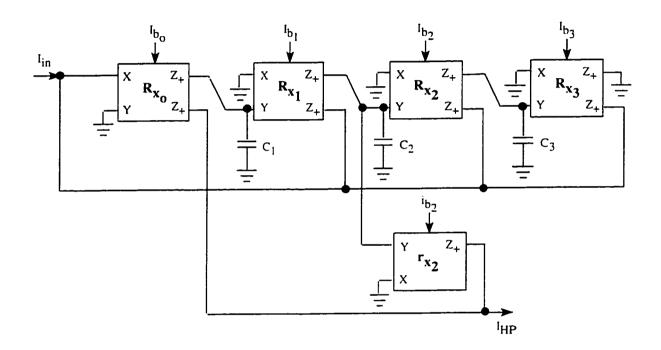

| 3.7  | CCCII $\pm$ network realizing $n^{th}$ order current mode general transfer         |

|------|------------------------------------------------------------------------------------|

|      | function                                                                           |

| 3.8  | Multiple output CCCII+ network realizing $n^{th}$ order current mode               |

|      | general transfer function                                                          |

| 3.9  | Circuit diagram of $3^{rd}$ order lowpass elliptic filter                          |

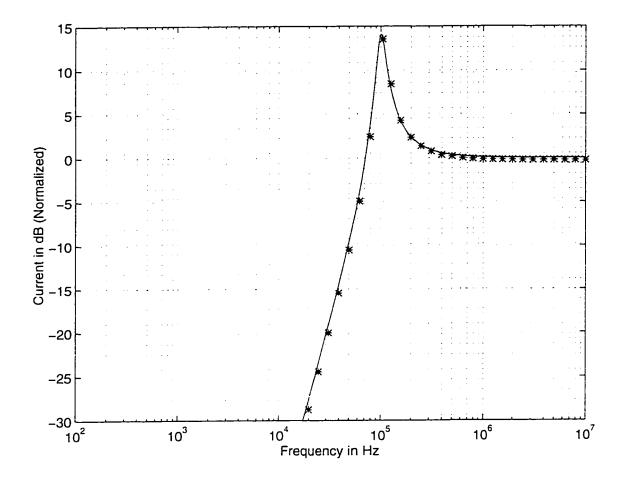

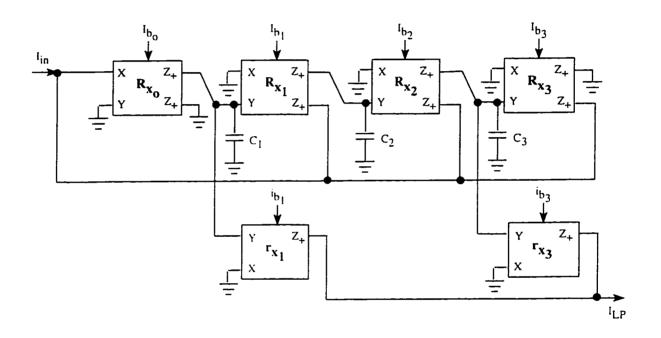

| 3.10 | Simulation result of third order lowpass elliptic filter                           |

| 3.11 | Circuit diagram of $3^{rd}$ order highpass elliptic filter                         |

| 3.12 | Simulation result of third order highpass elliptic filter                          |

| 3.13 | Simulation result of fifth order lowpass butterworth filter 104                    |

| 3.14 | Simulation result of fourth order highpass butterworth filter 105                  |

| 3.15 | Simulation result of gain response of fourth order allpass filter 106              |

| 3.16 | Simulation result of phase response of fourth order all<br>pass filter $\dots$ 107 |

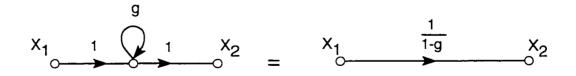

| A.1  | $n^{th}$ order signal flow graph                                                   |

| A.2  | Unity gain feedback loop subgraph                                                  |

| A.3  | $n^{th}$ order unity gain signal flow graph                                        |

| A.4  | Self loop transformation property                                                  |

| A.5  | $n^{th}$ order signal flow graph with self loops                                   |

| A.6  | $n^{th}$ order signal flow graph obtained by transposition                         |

#### Abstract

| Name:           | Noman Ali Tasadduq                               |

|-----------------|--------------------------------------------------|

| Title:          | Current Controlled Conveyor and its Applications |

| Major Field:    | Electrical Engineering                           |

| Date of Degree: | May 1998                                         |

The thesis discusses the use of current controlled conveyor in applications like filters, oscillator and impedance simulation. Parasitic resistance  $R_r$  of current conveyor is used to advantage for realizing programmable and resistorless circuits. Universal filters, sinusoidal oscillator, higher order filters and impedance simulation circuits are designed with minimum number of active and passive components and grounded capacitors. These circuits enjoy independent control of circuit parameters and low active and passive sensitivities. The proposed circuits are compared with the previously published work. Simulation results confirming the theoretical designs are included.

Master of Science Degree King Fahd University of Petroleum and Minerals Dhahran, Saudi Arabia May, 1998

### خلاصة الرسالة

الإسم : نعسمان عسسلي تسصدق عنوان الرسالة : ناقسل التيار المبرمسج وتسطبيقاتمه التخصص : الهسندسسة كسهربانسية تاريخ الشهادة : صفر ١٤١٩هـ

تناقش هذه الرسالة تطبيقات ناقل التيار المبرمج في دوائر المرشحات ومولـــدات الذبذبـات وكذلك الدوائر التمثيلية للمعانقة. وفي هذا الإطار تستخدم المقاومة الداخلية لناقل التيار (Rx) في تحقيق دوائر مبرمجة بدون استخدام مقاومات خارجية. وقد تم استنباط دوائر مرشــحات ، ومولد ذبذبات، مرشحات ذات درجة عالية وكذلك دوائر تمثيل الممانعة باســـتخدام الحــد الأدن من المكونات وكذلك باستخدام مكثفات متصلة بالأرض. وكل هذه الدوائر تتمتــع بخاصية هامة وهي إمكانية التحكم المستقل في خصائصها وكذلك الحساسية القليلة للتغـيرات في مكونات الدوائر. وفي كل الحالات عقدت المقارنة بين الدوائر المقترحة والمستنبطة والدوائر المائلة التي سبق نشرها. وكذلك استخدمت برامج الحاسب الآلي لتمثيـــل هــذه الدوائر. واختبارها.

### Chapter 1

# INTRODUCTION

Current mode signal processing circuit techniques are receiving considerable attention, because of their advantages in terms of speed, bandwidth and accuracy over the voltage mode circuits. Circuits are classified as current mode if the signals being processed are represented by time varying currents. Certain applications bencfit from operating in the current mode domain rather than in the voltage mode [1]: for example in a predominantly capacitive environment, speed is maximized by driving currents rather than voltages. Basic operations like for example addition, subtraction or multiplication are easier to perform using currents instead of voltages. In addition current-mode functions exhibit simpler architectures and lower supply voltage capabilities than their voltage-mode counterparts. As a result numerous papers have been published reporting new and novel current mode circuits, common examples are amplifiers, filters, oscillators and rectifiers [2].

The theoretical basis of many of the current mode circuits dates back many years but it is only with developments in truly complementary bipolar technology that these devices can be realized. At present, a number of current mode circuit techniques, such as current conveyors (CCs) [3][4], operational transconductance amplifiers (OTAs) [5]-[7] and switched current (SI) [8] have been developed. In these techniques the current conveyors have proved to be functionally flexible and versatile, rapidly gaining acceptance as a practical device with a wide range of high performance circuit and system applications. A host of circuits have been suggested on synthesis of various circuit elements using current conveyors [9].

### 1.1 Current Conveyor

Due to the growing role of current mode analog signal processing the current conveyors have become important building blocks in many applications. Current conveyors are a combination of voltage and current-mode devices offering low component count and high bandwidth. Unlike operational amplifiers, current conveyors do not have their bandwidth restricted by feedback. They can work over 100MHz bandwidth and remain stable with both inductive and capacitive loads.

Current conveyor was first introduced by Smith and Sedra in 1968 [10], as first generation current conveyor (CCI). In 1970 they introduced another type as second generation current conveyor (CCII) [11]. A third generation current conveyor (CCIII) was later introduced by Fabre in 1995 [12].

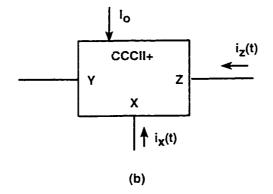

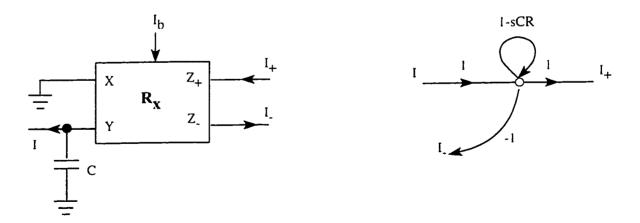

Current conveyor is normally a three terminal device with terminals marked as X, Y and Z. The input/output characteristics of the three types of conveyors can

Figure 1.1: (a) Symbol of first generation current conveyor. (b) Symbol of second generation current conveyor. (c) Symbol of third generation current conveyor.

be represented in the form of a matrix as follows:

$$\begin{bmatrix} i_y \\ v_x \\ i_z \end{bmatrix} = \begin{bmatrix} 0 & a & 0 \\ 1 & 0 & 0 \\ 0 & b & 0 \end{bmatrix} \begin{bmatrix} v_y \\ i_x \\ v_z \end{bmatrix}$$

(1.1)

A first generation current conveyor (CCI) results if a=1, while a second generation current conveyor (CCII) results if a = 0. For a = -1, the third generation current conveyor (CCIII) is obtained. Usually,  $b = \pm 1$ . The sign of b parameter determines the conveyor current transfer polarity  $(i_x \rightarrow i_z)$ . By convention, positive is taken to mean  $i_x$  and  $i_z$  both flowing simultaneously towards or away from the conveyor. Block representation of the three types of conveyors is shown in Figure 1.1. The operation of the first generation current conveyor is such that if a voltage is applied to terminal Y, an equal amount of voltage will appear on the terminal X. In the same way, an input current  $i_x$  being forced into terminal X will result in an equal amount of current into terminal Y. The current supplied to X is also conveyed to output terminal Z with either positive or negative polarity. Terminal Z has the characteristics of a current source, with high output impedance.

To increase the versatility of the current conveyor a high impedance node is introduced in second generation current conveyor. No current flows in terminal Yand it exhibits an infinite impedance. The voltage at X follows that applied to Y. The current supplied to X is conveyed to the high impedance output terminal Zwhere it is supplied with either positive or negative polarity.

The operation of a third generation current conveyor is similar to the first generation except that the current through terminal Y is in opposite direction to terminal X.

The second generation current conveyor, because of its versatility has proven to be more useful than CCI. They have led to a great number of applications in the various designs of analog electronics, like amplifiers, filters or more generally signal processing circuits [1]-[3][9].

# 1.2 Monolithic Implementation of Current Conveyors

Since the introduction of current conveyors, several configurations have been introduced to implement these conveyors [1][9]. Two types are suitable for monolithic implementation. One is based on the operational amplifier (OA) power supply current sensing technique and the other is based on the translinear cell. These are discussed below.

### 1.2.1 Power Supply Current Sensing Technique

In the earlier design of current conveyors voltage mode operational amplifiers were used for realizing a current conveyor. They suffered from the disadvantage of large number of operational amplifiers, use of matched resistances and low bandwidth [13]. Operational transconductance amplifiers have also been used but again were limited by poor bandwidth and poor output capability [14]. In an effort to minimize the disadvantages of using operational amplifiers as building blocks for current conveyors, a series of circuits and applications [15]-[20] were proposed. These circuits sensed the output stage current in an operational amplifier and produced a current conveyor function with appropriately connected current mirrors. The technique makes use of the fact that the current flowing from the output of the operational amplifier must be drawn through the supply leads. Current mirrors are thus used to sense the phase split output current via the operational amplifiers' supply leads. The current mirror outputs are then recombined to provide the required single high impedance bipolar output.

A CCII+ implementation using supply current sensing technique proposed by Wilson [16] is shown in Figure 1.2. Input Y draws only the bias current and acts as a high impedance input, whereas input X reflects the voltage at Y. As shown in Figure 1.3 a CCII- can be realized by simply adding a second pair of mirrors that are crosscoupled to produce a phase inversion between input and output current.

Although there had been attempts to improve the performance of supply current sensing techniques [16][20], however there are disadvantages which result from the

Figure 1.2: Schematic of VOA based CCII+

Figure 1.3: Schematic of VOA based CCII-.

presence of operational amplifier. These are listed below:

- low bandwidth (a few MHz to tens of MHz).

- large number of active and passive components necessary for the design of operational amplifier.

- increase of the power dissipation due to the operational amplifier.

- indirect monitoring of the output current introduces errors due to the bias component of the supply current.

#### 1.2.2 Translinear Cell

As discussed in section 1.2.1, the use of operational amplifier limits the performance of the circuits in terms of frequency and power dissipation. There had been attempts to design circuits that did not require operational amplifier. One of the major achievement in this regard is the implementation of the input cell with a mixed translinear loop composed of complementary bipolar transistors instead of an operational amplifier. Translinear implementation allows the design of high performance circuits that exhibit extended bandwidth [21]-[23].

The translinear principle [24] can be applied to the loops containing n baseemitter junctions of PNP bipolar transistors and n junctions of NPN bipolar transistors. There is an elegant circuit arrangement known as mixed translinear cell (or simply translinear cell) conceived by Gilbert [23]. As shown in Figure 1.4, it uses a set of transistors arranged in a ring. This topology shows a strong resemblance to a pair of back-to-back two transistor mirrors. Because of its high performance it is commonly used as the input stage of many high performance analog functions including transimpedance amplifiers [25], current controlled current sources [26]-[30], current conveyors [31]-[33] and impedance convertors [34][35]. Assuming that the following translinear conditions are satisfied [27].

- the current gain  $\beta \gg 1$ .

- $V_{BE} > 4V_T$  (  $V_T = kT/q$  is the thermal voltage).

- all the junctions are at the same temperature.

- the emitter areas of the NPN transistors are the same and those of PNP transistors are the same.

then the translinear principle produces the current balance.

$$I_1 I_3 = I_2 I_4 \tag{1.2}$$

Many different circuit functions may be achieved by a suitable choice of currents. For example, when  $I_1$ ,  $I_2$  and  $I_3$  are actively driven from input circuits then the output  $I_4$  will be equal to  $I_1I_3/I_2$ , providing the opportunity for multiplication ( $I_2$ held constant), division ( $I_3$  held constant) and squaring ( $I_1 = I_3 = I_i$  and  $I_2$  held constant).

A current conveyor based on Gilbert translinear cell was proposed by both Fabre [32] and Normand [31] independently and is shown in Figure 1.5. In this circuit the translinear current equation and mirror arrangements force the current out of Z to be equal to the current out of X, while the voltage at X will faithfully track Y: exactly the properties of a CCII+ current conveyor. This conveyor is characterized by an improved frequency response for the voltage transfer from port Y to port X

Figure 1.4: Circuit diagram of translinear cell.

[22] and needs a few number of active and passive components. Hence it requires less silicon area for implementation.

To introduce multiple outputs a pair of mirrors can be connected in parallel as shown in Figure 1.6. In order to realize CCII- cross coupled mirrors can be connected as shown in Figure 1.7.

Implementation of CCI+ is shown in Figure 1.8. Multiple outputs or negative output are easily realizable. Although there is no monolithic implementation for CCIII, it can be implemented by using multiple output CCII [12].

# 1.3 Effect of Internal Resistance in Current Conveyors (CCII)

The disadvantage associated with the topologies involving translinear cell as the input stage is that they have non-negligible parasitic resistance on port X (around 140 $\Omega$ , for a bias current equal to 100 $\mu$ A) which leads to errors when a load is connected at port X. Moreover, this may lead to instability if a capacitive load is connected at port X.

In the following section the effect of internal resistance in current conveyor circuits will be highlighted.

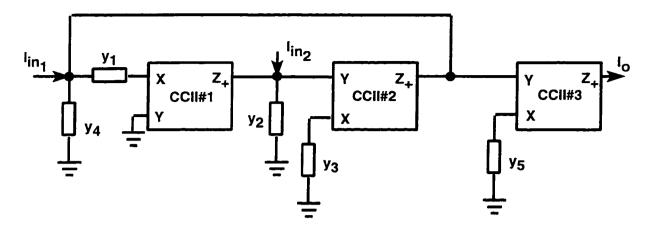

#### 1.3.1 Multiple input single output (MISO) based circuit

Consider the circuit shown in Figure 1.9. It is a multiple input single output current mode circuit. It uses three current conveyors for filter realization. Routine analysis of the circuit assuming ideal current conveyor ( $v_x = v_y$ ,  $i_z = i_x$ ) gives the following

.

Figure 1.5: Translinear Cell based CCII+.

Figure 1.6: Multiple Output Translinear Cell based CCII+.

Figure 1.7: Translinear Cell based CCII-.

Figure 1.8: Circuit diagram of CCI+.

Figure 1.9: Multiple input single output CCII+ based filter

current transfer function.

$$I_o = -\frac{y_2 y_5 I i n_1 + y_3 y_5 I i n_2}{y_1 y_2 + y_1 y_3 + y_2 y_4}$$

(1.3)

For  $I_{in_2} = 0$  and  $y_2 = sC_2$ ,  $y_4 = sC_4$ ,  $y_1 = G_1$ ,  $y_3 = G_3$ ,  $y_5 = G_5$ , a bandpass filter is realized, with the transfer function.

$$\frac{I_o}{I_{in_1}} = -\frac{G_5 C_{2} s}{C_1 C_2 s^2 + G_1 C_2 s + G_1 G_3}$$

(1.4)

Similarly, for  $I_{in_1}=0$  and other components remaining the same we obtain a lowpass filter with transfer function.

$$\frac{I_o}{I_{in_2}} = -\frac{G_3G_5}{C_1C_2s^2 + G_1C_2s + G_1G_3}$$

(1.5)

Similarly, by having  $I_{in_2} = 0$ ,  $y_5 = sC_5$  and other components remaining the same, we obtain a highpass function,

$$\frac{I_o}{I_{in_1}} = -\frac{C_2 C_5 s^2}{C_1 C_2 s^2 + G_1 C_2 s + G_1 G_3}$$

(1.6)

The center frequency  $w_o$ , bandwidth  $w_o/Q_o$  and quality factor  $Q_o$  are given by,

$$w_o = \sqrt{\frac{G_1 G_3}{C_2 C_4}} \tag{1.7}$$

$$\frac{w_o}{Q_o} = \frac{G_1}{C_4} \tag{1.8}$$

$$Q_o = \frac{1}{G_5} \sqrt{\frac{G_3 C_4}{G_1 C_2}}$$

(1.9)

Gain of highpass, lowpass and bandpass is approximately given by,

$$G_{LP} = \frac{G_5}{G_1} , \ G_{IIP} = \frac{C_5}{C_1} , \ G_{BP} = \frac{G_5}{G_1}$$

(1.10)

It can be seen from equations (1.7) and (1.8) that the center frequency can be adjusted without disturbing the bandwidth by adjusting external grounded resistance  $R_3$ . Lowpass and bandpass gain can be adjusted by  $G_5$  whereas, highpass gain can be adjusted by  $C_5$ , without disturbing the center frequency or bandwidth.

#### Experimental Results and Discussion

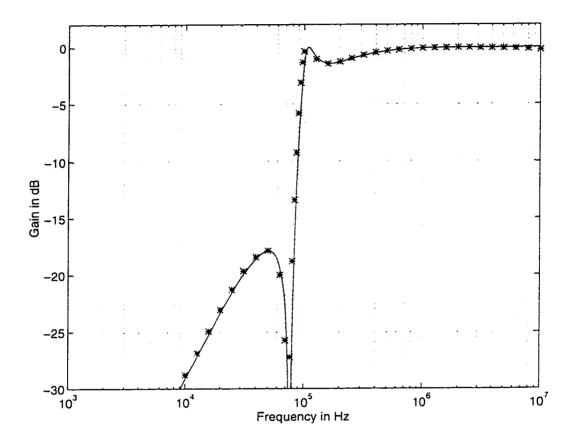

In order to validate the theoretical results, the filter is experimentally tested by using a breadboard realization. The AD844 current conveyor is used for experimental setup.

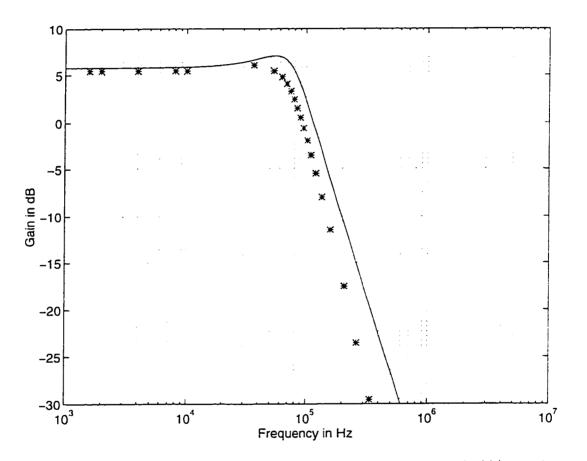

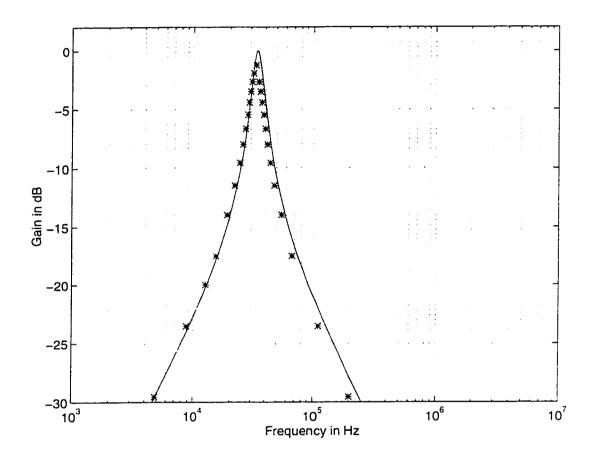

The lowpass filter experimental result, for 80kHz frequency, is shown in Figure 1.10, which confirms the theoretical analysis. The bandpass filter experimental result, for 35kHz center frequency, is shown in Figure 1.11, which also confirms the theoretical analysis. The internal resistances of the current conveyors can be added to the external resistances for predistortion design.

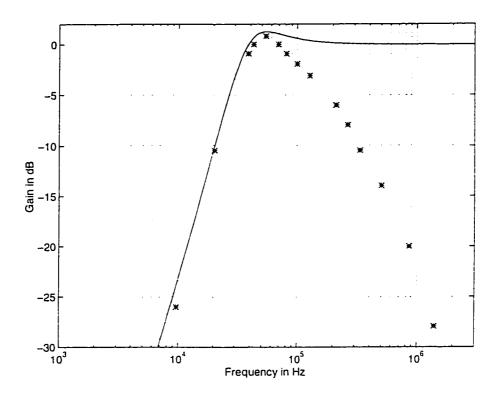

The highpass filter result, for 80kHz frequency, is shown in Figure 1.12. It can be seen that it does not confirm the theoretical result. In order to investigate the filter performance as a highpass filter, theoretical analysis is again performed by taking into account the parasitic resistance of current conveyor CCII#3. Only  $R_{r_3}$ is included in the analysis because it is in series with the capacitor  $C_5$ . Other internal

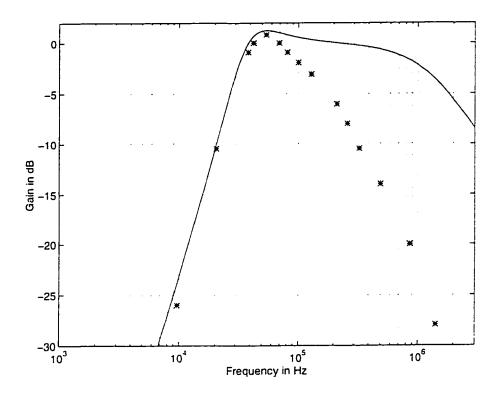

Figure 1.10: Experimental result for lowpass filter. theoretical, \*\*\*experimental,  $R_1 = R_3 = 2k\Omega$ ,  $R_5 = 1k\Omega$ ,  $C_2 = C_4 = 1nF$

Figure 1.11: Experimental result for bandpass filter. theoretical, \*\*\*experimental,  $R_1 = R_5 = 10k\Omega$ ,  $R_3 = 1k\Omega$ ,  $C_2 = 1nF$ ,  $C_4 = 2nF$

resistances  $(R_{x_1} and R_{x_2})$  can be easily added to the external resistances  $R_1$  and  $R_3$ . The modified transfer function is.

$$\frac{I_o}{I_{in_1}} = -\frac{R_1 R_3 C_2 C_5 s^2}{R_1 R_3 R_{x_3} C_2 C_4 C_5 s^3 + R_3 C_2 (R_{x_3} C_5 + R_1 C_4) s^2 + (R_{x_3} C_5 + R_3 C_2) s + 1}$$

(1.11)

It can be seen from the modified transfer function that the filter transfer function is now a third order function. The theoretical result of equation (1.11) and the experimental result are again plotted in Figure 1.13. It can be seen that the curve for theoretical result also shows a rolloff after 100kHz, like the experimental result. This is due to the presence of internal resistance  $R_{x_3}$  in series with a capacitor. The effect of  $R_{x_3}$  is not advantageous in this circuit as a capacitor is present in series to it. So an extra condition is imposed on the proposed highpass filter i.e.  $w \ll (R_{x_3}C_5)^{-1}$ , otherwise erronous results will appear.

## 1.4 Current Controlled Conveyor

Recently, Fabre [36] exploited to advantage the parasitic resistance, as its value is dependent on the bias current. The CCII+ proposed has the parasitic resistance at port X which is current controlled, thus it introduces the concept of Current Controlled Current Conveyor (CCCII).

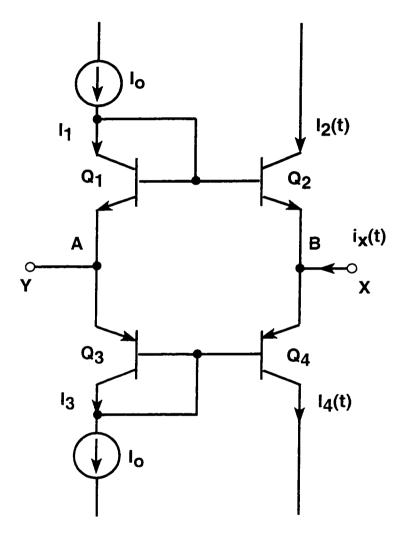

The basic circuit of the CCCII is the mixed translinear loop [27] shown in Figure 1.14. Applying translinear principle to the four transistors,

$$I_1 I_3 = I_2 I_4 \tag{1.12}$$

Assuming  $\beta \gg 1$ , the bias current  $I_o = I_1 = I_3$ , therefore

$$I_o^2 = I_2 I_4 \tag{1.13}$$

Figure 1.12: Experimental result for highpass filter. theoretical, \*\*\*experimental,  $R_1 = R_3 = 2k\Omega$ ,  $C_2 = C_4 = C_5 = 2nF$

Figure 1.13: Experimental result for highpass filter with internal resistance. theoretical, \*\*\*experimental,  $R_1 = R_3 = 2k\Omega$ ,  $C_2 = C_4 = C_5 = 2nF$

Figure 1.14: Circuit diagram of mixed translinear cell.

The expressions for  $I_2$  and  $I_4$  can be written in terms of  $i_x(t)$  as,

$$I_2 = \frac{1}{2} [(i_x^2(t) + 4I_o^2)^{1/2} - i_x(t)]$$

(1.14)

$$I_4 = \frac{1}{2} \left[ \left( i_x^2(t) + 4I_o^2 \right)^{1/2} + i_x(t) \right]$$

(1.15)

The voltage difference between points A and B depends on the value of the current  $i_x(t)$  and its expression is given by,

$$V_{BA} = -V_T \log \frac{I_2}{I_o} \tag{1.16}$$

$$V_{BA} = -V_T \log\left[-i_x(t)/2I_o + \sqrt{1 + (i_x(t)/2I_o)^2}\right]$$

(1.17)

$$V_{BA} = V_T sinh^{-1}(\frac{i_x(t)}{2I_o})$$

(1.18)

Assuming the magnitude of current  $i_x(t)$  much smaller than  $2I_o$ ,  $V_{BA}$  is given by

$$V_{BA} = \frac{V_T}{2I_o} i_x \tag{1.19}$$

Thus  $R_x$  is calculated as follows

$$R_{r} = \frac{V_{BA}}{i_{r}} = \frac{V_{T}}{2I_{o}}$$

(1.20)

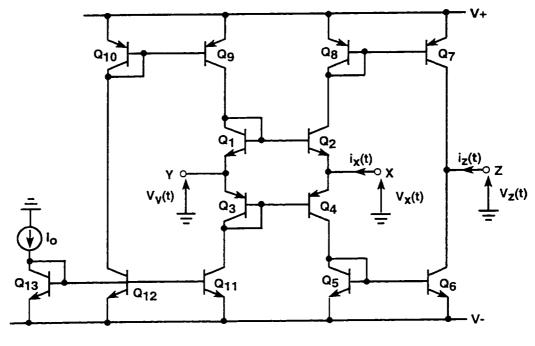

where  $V_T$  is the thermal voltage. Equation (1.20) shows that the small signal resistance  $R_x$  is dependent on the bias current. The mixed translinear implementation of a second generation current controlled conveyor (CCCII+) and its symbol are shown in Figure 1.15. The matrix relationship, by taking intrinsic resistance  $R_x$ into account becomes,

$$\begin{bmatrix} i_y \\ v_x \\ i_z \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ 1 & R_x & 0 \\ 0 & 1 & 0 \end{bmatrix} \begin{bmatrix} v_y \\ i_x \\ v_z \end{bmatrix}$$

(1.21)

(a)

Figure 1.15: (a)Circuit diagram of CCCII+. (b) Symbol of CCCII+.

A negative current transfer ratio can be easily obtained by adding two cross coupled current mirrors.

This topology results in the following advantages.

- The parasitic resistance  $R_r$  is current controlled. Therefore circuits can be implemented using CCCII without external resistance. Such circuits could be programmed.

- Due to the use of monolithic implementation it has excellent frequency response.

- The number of active and passive components are very few and therefore require less silicon area in implementation.

- Because of low component count and no resistances, power dissipation is very low.

- Circuits using this CCCII will also take very less silicon area as no external resistances will be used.

Fabre et al. [36] performed a comparison between controlled conveyor (CCCII) and operational transconductance amplifier (OTA). This comparison shows that CCCII is a better option than OTA. For a conventional bipolar OTA the value of transconductance  $(g_m)$  is  $I_o/2V_T$  [1], while  $1/R_x$  for the CCCII is  $2I_o/V_T$ . Thus, for the same value of  $I_o$  the transconductance of OTA will be 4 times less than that of the controlled conveyor. This means that if a filter is designed by using only OTAs or only CCCIIs then for the same center frequency  $f_o$ , which is linearly proportional to the bias current  $I_o$ , the OTA implementation will result in higher power consumption. Fabre showed that the implementation of voltage to current convertor using OTA results in 3 times greater power consumption than with the controlled conveyor. Also because of the use of high values of currents, the maximum frequency usable will be reached sooner. Therefore the frequency response and power dissipation of the CCCII based circuits is expected to be better than OTA based circuits.

Like the transconductance of operational transconductance amplifier (OTA), internal resistance of controlled conveyor is temperature dependent  $(R_x = V_T/(2I_o))$ . Its temperature dependence can be reduced by using a PTAT current source [37].

The most important deviation in the value of internal resistance  $R_x$  occurs for very low or very high values of bias current. These deviations occur because of the difference between the collector and bias current of the transistors  $Q_1$  and  $Q_3$  (see Figure 1.10). These current deviations result from the low value of the current gain  $\beta$  of transistors  $Q_1$  to  $Q_4$  operating for very low or very high values of collector currents [36]. To reduce these deviations, transistors with higher values of  $\beta$  should be used in realizing CCCII.

## 1.5 Applications of Current Controlled Conveyor

Although current conveyors are used in many applications [1], in this thesis stress is upon universal filters, higher order filters, oscillator and impedance simulation circuits. These are discussed briefly.

## 1.5.1 Active-C Universal Filters

After the work of Nawrocki and Klein [38] the emphasis is on designing universal filters, as all the major filter functions can be implemented from the same structure and the higher orders can be implemented by cascading the second order function. Although the original design using operational transconductance amplifiers (OTAs) [39]-[42] is suitable for integration due to the absence of resistors in the circuit, performance limitations of OTAs such as poor bandwidth and poor output drive capabilities restrict the overall operating performance [43][44]. High performance current conveyors (CCs) become an attractive alternative to OTAs in this application because of their higher bandwidth and improved current drive capabilitics [43]-[49]. But the disadvantage associated with current conveyors is lack of programmability. This limitation could be overcome by using current controlled conveyor, by taking advantage of its internal programmable resistance. At present only few circuits using the current controlled conveyor are available. However these suffer from certain disadvantages. The bandpass filter proposed by Fabre [36] does not possess independent control of frequency and bandwidth and the universal filter proposed by Kiranon et al. [50] uses floating capacitors and cannot realize allpass and notch functions.

## 1.5.2 Sinusoidal Oscillators

Over the past few years a number of schemes have been developed to realize sinusoidal oscillators [51]-[56]. Schemes using OTAs give the advantage of programmability over the simple current conveyors. Current controlled conveyor has the programmability feature and gives better performance in terms of frequency and power dissipation. So far there are only two circuits in the literature that use current controlled conveyor for sinusoidal oscillator and are proposed by Kiranon et al. [57][50]. The disadvantage in the first circuit is that the condition of oscillation and the frequency of oscillation are not independently controllable. Whereas, the second circuit requires another current controlled conveyor for sensing the output current.

#### **1.5.3** Impedance Simulation

Impedance realization finds wide application in the design of active filters and oscillators. There are lots of circuits realizing impedance with general impedance converter (GIC) and negative impedance converter (NIC) using operational amplifier [58][59], but they suffer from poor bandwidth. Schemes using OTA provide the programmability option but they also suffer from poor bandwidth [60]. Until now, there is only one circuit realizing floating inductor using current controlled conveyor [61].

## 1.5.4 Higher Order Filter Synthesis

Although there are many higher order structures in the literature but most of them are voltage mode and use large number of active and passive components. Some of the techniques in the literature are presented by Acar. Gunes and Jie Wu. The filters proposed by Acar [62][63] use floating and large number of passive and active components and are voltage mode and the one proposed by Gunes and Anday [64] and Jie Wu [65] can realize only low pass filter. The number of active and passive components is an important parameter for higher order filters. The number of active components is rapidly growing, for the above mentioned filter structures, as the filter order increases. This results in greater power consumption and larger chip area. Also the use of floating capacitors increases the area. Thus reducing the number of elements and utilizing grounded capacitors becomes a major consideration in high frequency continuous time filter design.

Until now, there are no higher order filter structures in the literature using current controlled conveyor.

## 1.6 **Problem Definition**

According to the literature review, it is believed that current controlled conveyor is more versatile and flexible active device as compared to other available devices. It results in circuits without external resistances, with less power consumption and takes less area for implementation. However, only a little work has been done in designing application circuits like universal filters and sinusoidal oscillators using current controlled conveyor. The main objective of this thesis is to propose new universal filters, higher order filters, sinusoidal oscillator and impedance simulation circuits using current controlled conveyor.

## Chapter 2

# FILTERS,OSCILLATOR AND IMPEDANCE SIMULATION

An electric filter can be defined as an interconnected network of electrical components that shapes the spectrum of the input signal in order to obtain an output signal with the desired frequency content. Thus a filter has passbands where the frequency components are transmitted to the output and stopbands where they are rejected. The major types of such filters are lowpass(LP), highpass(HP), bandpass(BP), bandreject(BR) or notch, and allpass(AP).

The earliest filter designs use only resistors, inductors and capacitors and therefore are called passive RLC filters. With the growing pressure towards microminiturisation, inductors were found to be too bulky so that designers started to replace passive RLC filters by active RC circuits. Aside from their obvious size and weight advantages over equivalent passive RLC implementations, active filters provide the following additional advantages:

• Increased circuit reliability because all processing steps can be automated.

- In large quantities the cost of integrated circuit active filters are much lower than equivalent passive filters.

- Improvement in performance because high quality components can be readily manufactured.

- A reduction in parasitics because of smaller size.

- Active filters and digital circuitry can be integrated onto the same silicon chip.

- The design and tuning processes are simpler than those for passive filters.

Because of these advantages active filters are used for a wide variety of applications such as voice and video signal processing for the communication industry. Much of the motivation for considering active filters stems from the progress that has occured in integrated circuit technology.

## 2.1 Universal Second Order Filters

Second order active filters are of great interest because several cells of that kind can be connected in cascade to implement higher order filters. Cascade filter design is the approach most widely used to design active filters, because the individual filter sections are noninteracting.

For a voltage-mode second order filter it is advantageous to have infinite input impedance because several cells can be directly connected in cascade with no need to interpose active separating stages. Similarly for a current mode active filter it is desirable to have low input impedance and high output impedance. A universal voltage or current-mode filter is capable of realizing the five different basic functions (LP, HP, BP, BR and AP filters). Advantage is that all the filter functions can be implemented from the same structure. There are two categories of universal filters: multiple input single output and single input multiple output. The former can realize each function separately by controlling the inputs while the latter can provide all the five functions simultaneously.

## 2.2 Design Requirements

An active filter should be designed by taking into consideration the following requirements.

- Independent control of center frequency  $w_o$  and the bandwidth  $w_o/Q_o$ , where  $Q_o$  is the quality factor.

- Use of grounded capacitors to overcome the effect of stray capacitance.

- It is advantageous if the center frequency and the bandwidth are programmable.

- Minimum number of active and passive components. This will result in filters with less power consumption, less silicon area and lower sensitivity.

- No matching/cancellation requirements for realizing different filtering functions.

- The sensitivity of filter parameters  $(w_o, w_o/Q_o)$  to active and passive components should be low (less than unity).

- Filters should be directly cascadable.

Current controlled conveyor is an excellent candidate for the above mentioned requirements. Its internal resistance can be controlled by bias current, therefore programmable filters are easy to design. Moreover, filters will have no external resistances which will result in less silicon area for implementation and low power consumption.

## 2.3 Proposed Circuits

Only a few universal filters are available that use the current controlled conveyor. All of them suffer from certain disadvantages. The bandpass filter proposed by Fabre [36] does not possess independent control of frequency and bandwidth and the universal filter proposed by Kiranon et al. [50] uses floating capacitors and cannot realize allpass and notch functions. In the following section unviversal filters are proposed that remove the disadvantages associated with the above mentioned work.

## 2.3.1 Universal Filter 1

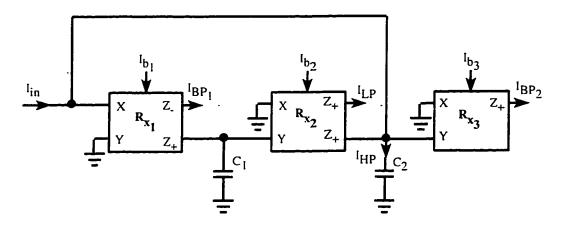

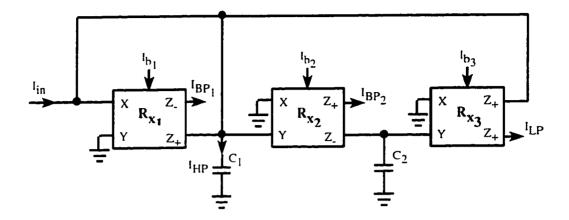

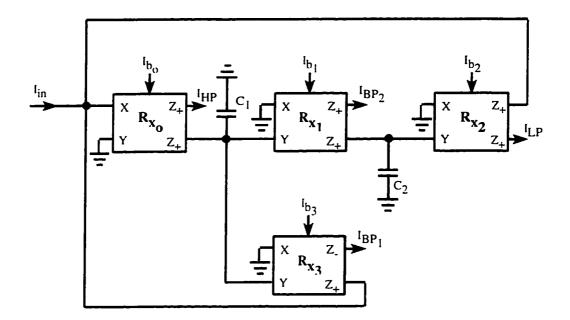

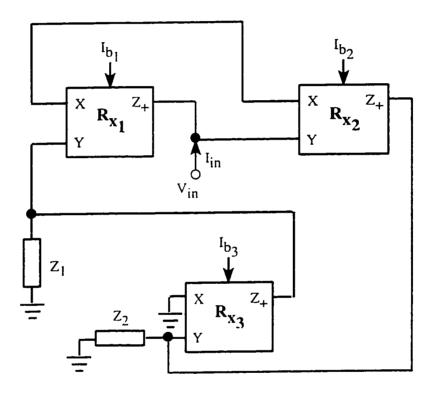

The proposed circuit is shown in Figure 2.1 [66] (Appendix B). It is a current-mode circuit using current controlled conveyor (CCCII) with internal resistance  $R_x$ . This filter uses three multiple output CCCII, two capacitors and no external resistances. Routine analysis of the circuit assuming ideal CCCII ( $v_x = v_y + i_x R_x$ ,  $i_x = i_z$ ) gives the following current transfer functions.

$$\frac{I_{LP}}{I_{in}} = \frac{R_{x_1}}{R_{x_1}R_{x_2}R_{x_1}C_1C_2s^2 + R_{x_2}R_{x_3}C_1s + R_{x_3}}$$

(2.1)

$$\frac{I_{IIP}}{I_{in}} = \frac{R_{x_1}R_{x_2}R_{x_3}C_1C_2s^2}{R_{x_1}R_{x_2}R_{x_3}C_1C_2s^2 + R_{x_2}R_{x_3}C_1s + R_{x_3}}$$

(2.2)

Figure 2.1: CCCII based Universal second order filter-1.

$$\frac{I_{BP_1}}{I_{in}} = \frac{R_{x_2}R_{x_3}C_1s}{R_{x_1}R_{x_2}R_{x_3}C_1C_2s^2 + R_{x_2}R_{x_3}C_1s + R_{x_3}}$$

(2.3)

$$\frac{I_{BP_2}}{I_{in}} = \frac{R_{x_1}R_{x_2}C_1s}{R_{x_1}R_{x_2}R_{x_3}C_1C_2s^2 + R_{x_2}R_{x_3}C_1s + R_{x_3}}$$

(2.4)

The high pass current is flowing through capacitor  $C_2$ . It can be sensed by connecting another CCCII as a current follower. A current mode notch signal is easily obtained by connecting the  $I_{HP}$  and  $I_{LP}$  output terminals. Let  $I_{NH} = I_{HP} + I_{LP}$ , we obtain the current-mode notch transfer function as,

$$\frac{I_{NH}}{I_{in}} = \frac{R_{x_1}R_{x_2}R_{x_3}C_1C_2s^2 + R_{x_3}}{R_{x_1}R_{x_2}R_{x_3}C_1C_2s^2 + R_{x_2}R_{x_3}C_1s + R_{x_3}}$$

(2.5)

Similarly by connecting the  $I_{HP}$ ,  $I_{BP_1}$  and  $I_{LP}$  output terminals, a current mode allpass response is obtained

$$\frac{I_{AP}}{I_{in}} = \frac{R_{x_1}R_{x_2}R_{x_3}C_1C_2s^2 - R_{x_2}R_{x_3}C_1s + R_{x_3}}{R_{x_1}R_{x_2}R_{x_3}C_1C_2s^2 + R_{x_2}R_{x_3}C_1s + R_{x_3}}$$

(2.6)

The center frequency  $w_o$ , bandwidth  $w_o/Q_o$  and quality factor  $Q_o$  are given by,

$$w_o = \sqrt{\frac{1}{R_{r_1}R_{r_2}C_1C_2}} \tag{2.7}$$

$$\frac{w_o}{Q_o} = \frac{1}{R_{x_1}C_2}$$

(2.8)

$$Q_o = \sqrt{\frac{R_{x_1}C_2}{R_{x_2}C_1}}$$

(2.9)

Gain of high pass, lowpass and bandpass are approximately given by,

$$G_{LP} = G_{HP} = G_{BP_1} = 1 , \ G_{BP_2} = \frac{R_{x_1}}{R_{x_1}}$$

(2.10)

It can be seen from equations (2.7) and (2.8) that the center frequency can be adjusted without disturbing the bandwidth. The center frequency  $w_o$  can be electronically tuned by adjusting  $I_{b_2}$ . The gain of bandpass function  $I_{BP_2}$  can be independently adjusted without disturbing  $w_o$  and  $w_o/Q_o$  by adjusting  $I_{b_3}$ . Another important advantage is that no matching condition is required for the realization of allpass and notch functions.

In summary the proposed circuit at most needs four multiple output CCCII for the realization of five basic filter functions, one grounded and one floating capacitor (for the realization of highpass filter) and uses no external resistance.

#### Sensitivity Analysis

Nonideal analysis is required to find the active sensitivities of the filter. Assuming that the nonideal port relations of the CCCII can be expressed as  $v_x = \beta v_y + i_x R_x$ ,  $i_z = \alpha i_x$ , where  $\alpha = 1 - \delta$  ( $|\delta| \ll 1$ ) denotes the current tracking error,  $\beta = 1 - \epsilon$  ( $|\epsilon| \ll 1$ ) represents the voltage tracking error, the output currents can now be expressed as,

$$\frac{I_{LP}}{I_{in}} = \frac{\alpha_1 R_{x_3}}{R_{x_1} R_{x_2} R_{x_3} C_1 C_2 s^2 + R_{x_2} R_{x_3} C_1 s + \alpha_1 \alpha_2 \beta_2 R_{x_3}}$$

(2.11)

$$\frac{I_{IIP}}{I_{in}} = \frac{R_{x_1}R_{x_2}R_{x_3}C_1C_2s^2}{R_{x_1}R_{x_2}R_{x_3}C_1C_2s^2 + R_{x_2}R_{x_3}C_1s + \alpha_1\alpha_2\beta_2R_{x_3}}$$

(2.12)

$$\frac{R_{r_2}R_{r_3}C_1s}{R_{r_1}R_{r_2}R_{r_3}C_1C_2s^2 + R_{r_2}R_{r_3}C_1s + \alpha_1\alpha_2\beta_2R_{r_3}}$$

(2.13)

$$\frac{I_{BP_2}}{I_{in}} = \frac{\alpha_3 \beta_3 R_{x_1} R_{x_2} C_1 s}{R_{x_1} R_{x_2} R_{x_3} C_1 C_2 s^2 + R_{x_2} R_{x_3} C_1 s + \alpha_1 \alpha_2 \beta_2 R_{x_3}}$$

(2.14)

The center frequency  $w_o$ , bandwidth  $w_o/Q_o$  and quality factor  $Q_o$  are given by,

$$w_{o} = \sqrt{\frac{\alpha_{1}\alpha_{2}\beta_{2}}{R_{r_{1}}R_{r_{2}}C_{1}C_{2}}}$$

(2.15)

$$\frac{w_o}{Q_o} = \frac{1}{R_{x_1}C_2}$$

(2.16)

$$Q_o = \sqrt{\frac{\alpha_1 \alpha_2 \beta_2 R_{x_1} C_2}{R_{x_2} C_1}}$$

(2.17)

By defining the sensitivity [58] of  $w_o$  and  $Q_o$  to the parameter F by.

$$S_F^{w_o} = \frac{dw_o}{dF} \frac{F}{w_o} \text{ and } S_F^{Q_o} = \frac{dQ_o}{dF} \frac{F}{Q_o}$$

(2.18)

From equations (2.15) and (2.17) it is easy to show that the active and passive sensitivities of the parameters  $w_o$  and  $Q_o$  (i.e. per-unit change in  $w_o$  and  $Q_o$  due to a given per-unit change in F) are,

$$S_{\alpha_{1}}^{w_{o}} = S_{\alpha_{2}}^{w_{o}} = S_{\beta_{2}}^{w_{o}} = \frac{1}{2} , \ S_{\alpha_{3}}^{w_{o}} = S_{\beta_{1}}^{w_{o}} = S_{\beta_{3}}^{w_{o}} = 0$$

$$S_{R_{x_{1}}}^{w_{o}} = S_{R_{x_{2}}}^{w_{o}} = S_{C_{1}}^{w_{o}} = S_{C_{2}}^{w_{o}} = -\frac{1}{2} , \ S_{R_{x_{3}}}^{w_{o}} = 0$$

$$S_{\alpha_{1}}^{Q_{o}} = S_{\alpha_{2}}^{Q_{o}} = S_{\beta_{2}}^{Q_{o}} = \frac{1}{2} , \ S_{\alpha_{3}}^{Q_{o}} = S_{\beta_{1}}^{Q_{o}} = S_{\beta_{3}}^{Q_{o}} = 0$$

$$S_{R_{x_{1}}}^{Q_{o}} = -S_{R_{x_{2}}}^{Q_{o}} = -S_{C_{1}}^{Q_{o}} = S_{C_{2}}^{Q_{o}} = \frac{1}{2} , \ S_{R_{x_{3}}}^{Q_{o}} = 0$$

All of the active and passive sensitivities are small (no more than unity).

#### Simulation Results and Discussion

To validate the theoretical analysis, the proposed universal filter in Figure 2.1 is simulated using ICAPS circuit simulation program. The CCCII $\pm$  is modelled by the schematic implementation of Figure 1.15, proposed by Fabre et al. [36] with dc

supply voltage of  $\pm 2.5$ V. The simulation results reported here were obtained using the transistors PR100N(PNP) and NR200N(NPN) of the bipolar arrays ALA400 from AT&T [67].

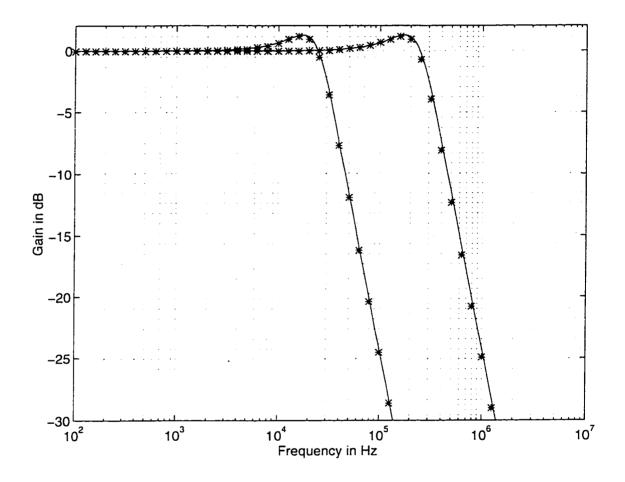

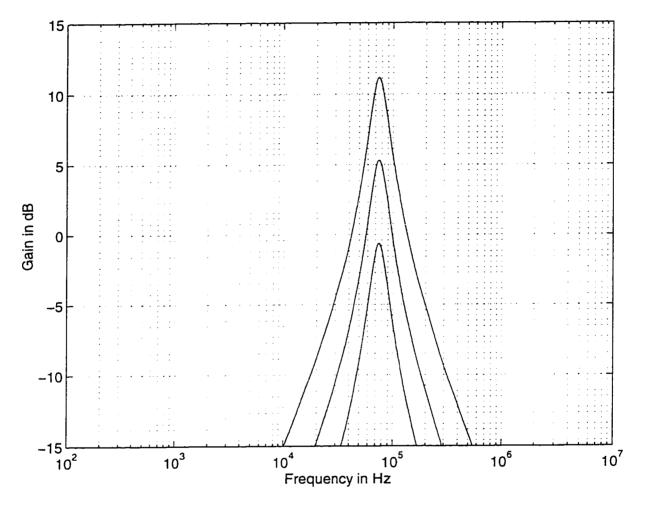

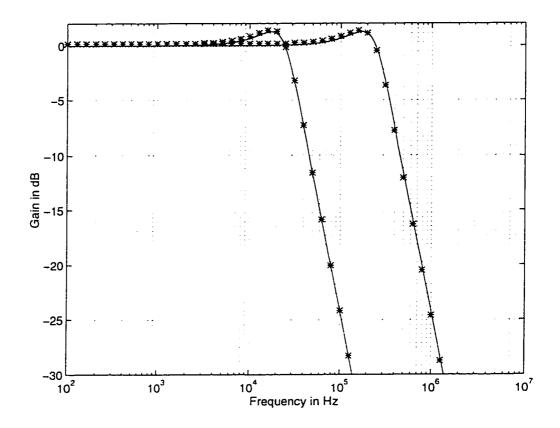

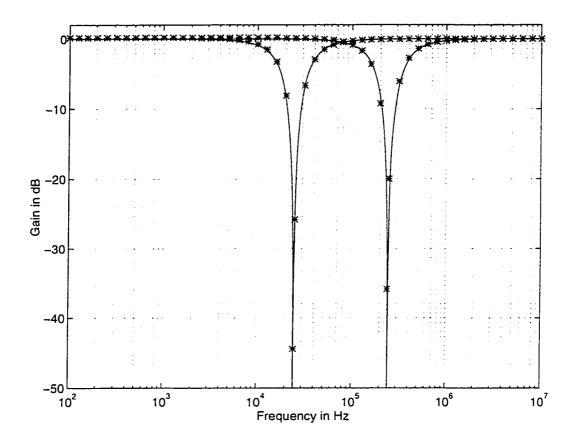

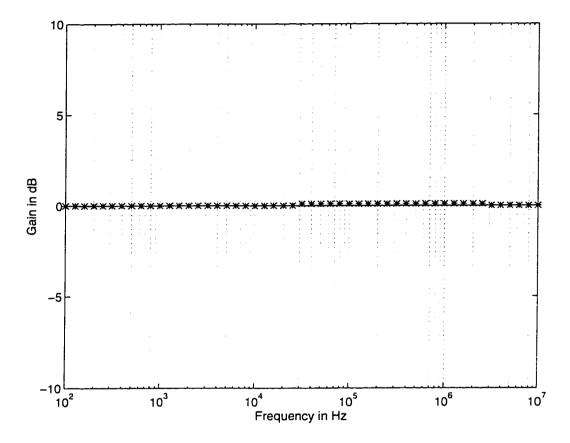

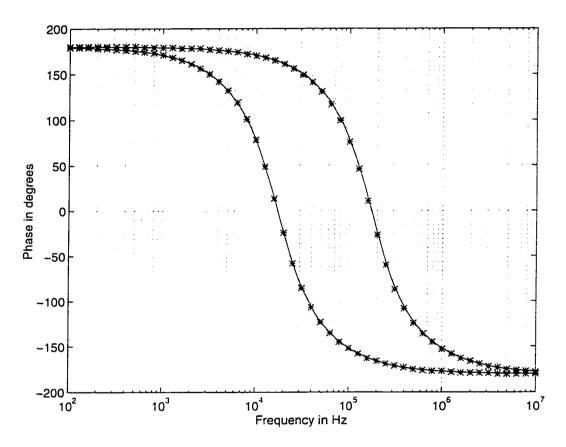

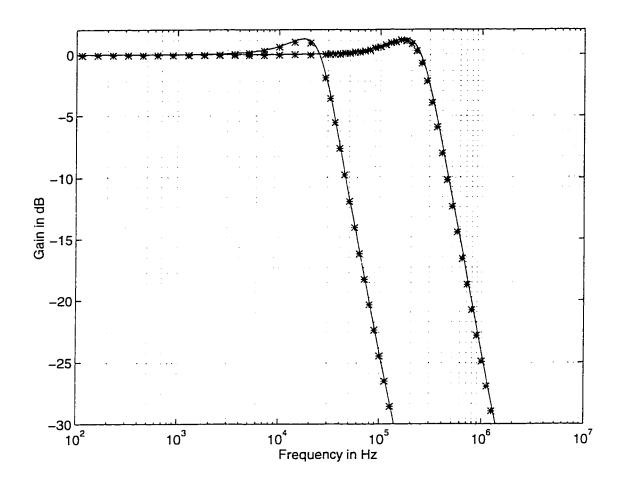

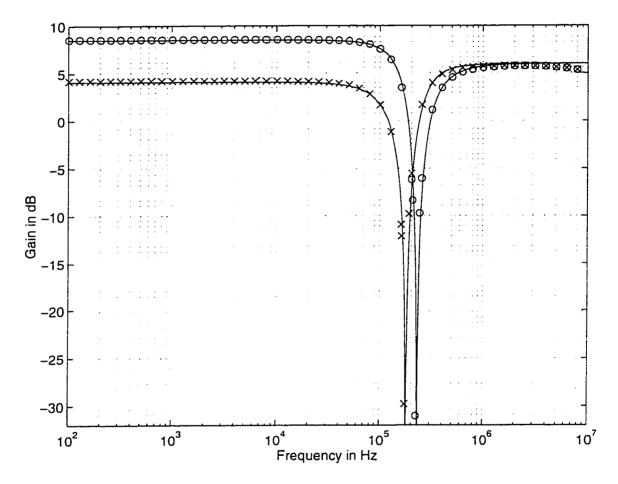

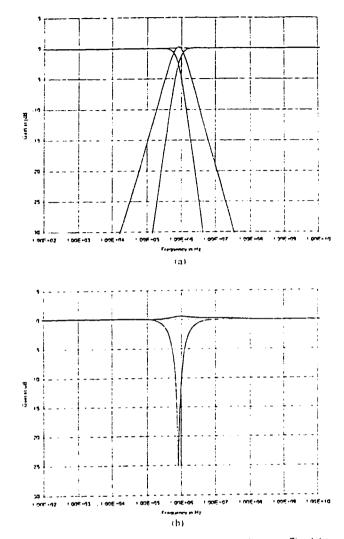

Figures 2.2 to 2.7 show the theoretical and simulation results of lowpass, highpass, bandpass, notch and allpass (gain and phase response) filters respectively. Lowpass, highpass, notch and allpass filters are simulated for (1)24.48kHz and (2)244.8kHz frequencies. Bandpass filter is simulated for (1)54.7kHz and (2)244.7kHz frequencies. It can be seen that the simulation results agree very well with the presented theory. Deviations less than 5% are obtained for these results. Figure 2.8 shows the effect of changing  $I_{b_1}$ . It can be seen that the bandpass gain of  $I_{BP_2}$ can be independently adjusted without disturbing the bandwidth and center frequency. The results are obtained by simulating the bandpass filter for gain=1.2.4 with 77.4kHz center frequency. In short the proposed circuit offers the following advantages.

- Arbitrary biquadratic transfer functions are realized with single input.

- With multiple outputs all the five basic filter functions can be obtained.

- Center frequency  $w_o$  can be independently adjusted.

- No external resistances are used.

- No matching conditions are required for the realization of allpass and notch transfer functions.

- Low active and passive sensitivities.

Figure 2.2: Simulation results of the lowpass filter. theoretical,\*\*\*simulation (1)  $I_1 = I_2 = I_3 = 10 \mu A$ ,  $C_1 = C_2 = 5nF(2)$   $I_1 = I_2 = I_3 = 100 \mu A$ ,  $C_1 = C_2 = 5nF$

Figure 2.3: Simulation results of the highpass filter. theoretical,\*\*\*simulation (1)  $I_1 = I_2 = I_3 = 10\mu A$ ,  $C_1 = C_2 = 5nF$  (2)  $I_1 = I_2 = I_3 = 100\mu A$ ,  $C_1 = C_2 = 5nF$

Figure 2.4: Simulation results of the bandpass filter. theoretical,\*\*\*simulation (1)  $I_1 = I_3 = 5\mu A$ ,  $I_2 = 100\mu A$ ,  $C_1 = C_2 = 5nF$  (2)  $I_1 = I_3 = 20\mu A$ ,  $I_2 = 520\mu A$ ,  $C_1 = C_2 = 5nF$

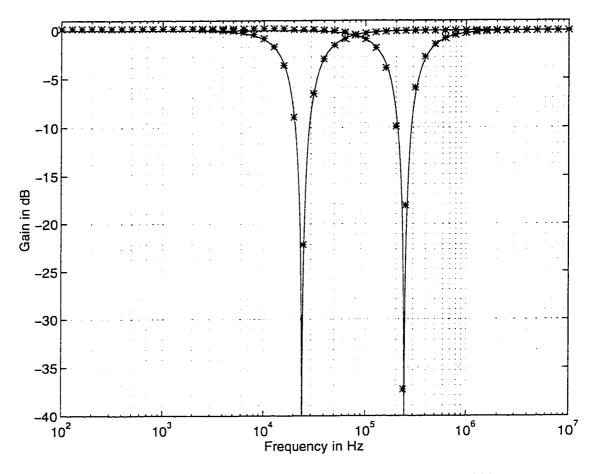

Figure 2.5: Simulation results of the notch filter. theoretical,\*\*\*simulation (1)  $I_1 = I_2 = I_3 = 10\mu A$ ,  $C_1 = C_2 = 5nF$  (2)  $I_1 = I_2 = I_3 = 100\mu A$ ,  $C_1 = C_2 = 5nF$

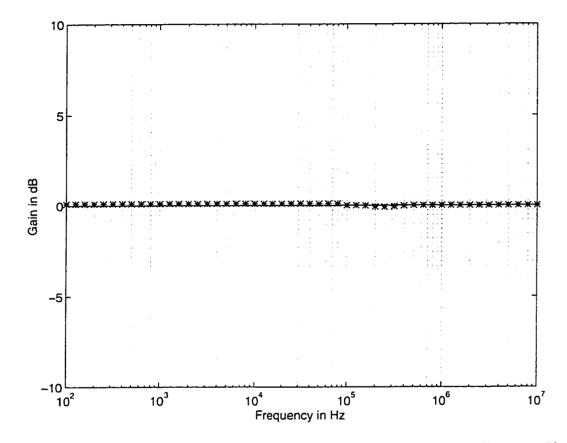

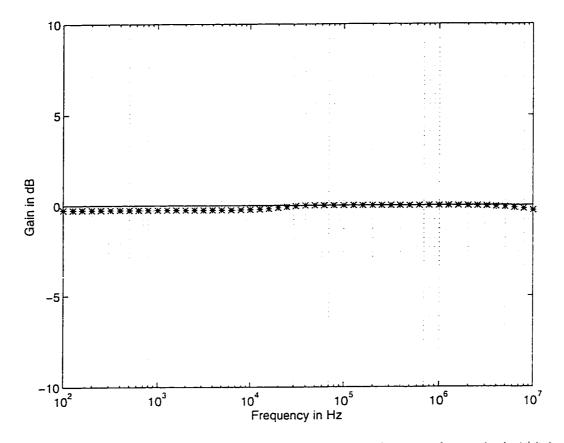

Figure 2.6: Simulation results of the gain of allpass filter. theoretical.\*\*\*simulation  $I_1 = I_2 = I_3 = 100 \mu A$ ,  $C_1 = C_2 = 5nF$

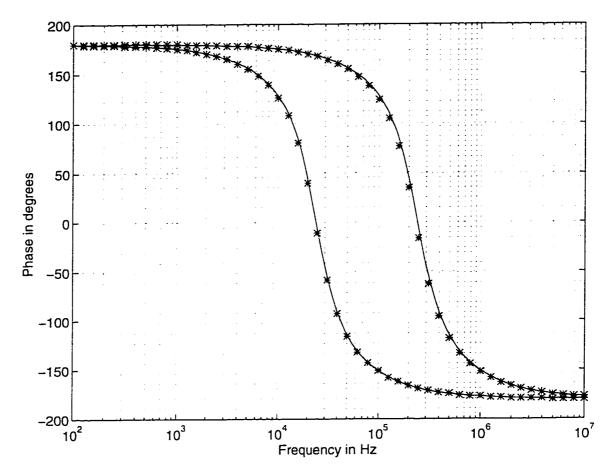

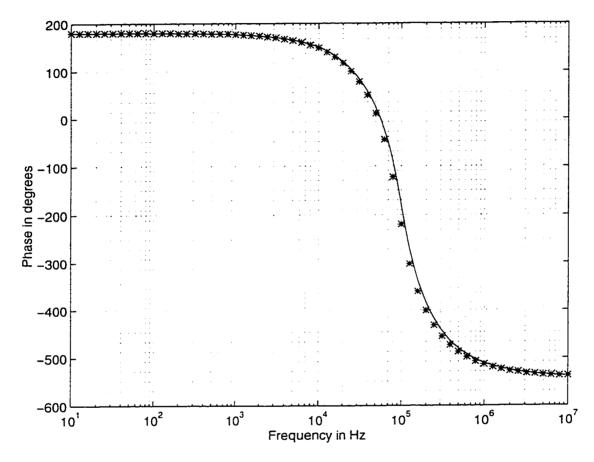

Figure 2.7: Simulation results of the phase of allpass filter. theoretical, \*\*\*simulation (1)  $I_1 = I_2 = I_3 = 10\mu A$ ,  $C_1 = C_2 = 5nF$  (2)  $I_1 = I_2 = I_3 = 100\mu A$ ,  $C_1 = C_2 = 5nF$

Figure 2.8: Simulation results of the variable gain of bandpass filter. (1)  $I_1 = I_3 = 10\mu A$ ,  $I_2 = 100\mu A$ ,  $C_1 = C_2 = 5nF$  (2)  $I_1 = 10\mu A$ ,  $I_2 = 100\mu A$ ,  $I_3 = 20\mu A$ ,  $C_1 = C_2 = 5nF$  (3)  $I_1 = 10\mu A$ ,  $I_2 = 100\mu A$ ,  $I_3 = 40\mu A$ ,  $C_1 = C_2 = 5nF$

Figure 2.9: CCCII based Universal second order filter-2.

The disadvantage associated with this filter is that the high pass current is flowing through a capacitor. As a result the capacitor will be floating if this current needs to be sensed. Also the bandwidth  $w_o/Q_o$  cannot be set independently without disturbing the center frequency. To make the bandwidth and center frequency independent, another filter is proposed with some modifications.

## 2.3.2 Universal Filter 2

The proposed circuit is shown in Figure 2.9. It is a current-mode circuit using current controlled conveyor (CCCII) with internal resistance  $R_x$ . This filter uses three multiple output CCCII, two capacitors and no external resistances. Assuming that the nonideal port relations of the CCCII can be expressed as  $v_x = \beta v_y + i_x R_x$ ,  $i_z = \alpha i_x$ , where  $\alpha = 1 - \delta$  ( $|\delta| \ll 1$ ) denotes the current tracking error,  $\beta = 1 - \epsilon$  ( $|\epsilon| \ll 1$ ) represents the voltage tracking error, gives the following current transfer functions,

$$\frac{I_{LP}}{I_{in}} = \frac{\alpha_2 \beta_2 \beta_3 R_{x_1}}{R_{x_1} R_{x_2} R_{x_3} C_1 C_2 s^2 + (1 + \alpha_1) R_{x_2} R_{x_3} C_2 s + \alpha_2 \alpha_3 \beta_2 \beta_3 R_{x_1}}$$

(2.19)

$$\frac{I_{IIP}}{I_{in}} = \frac{R_{x_1}R_{x_2}R_{x_3}C_1C_2s^2}{R_{x_1}R_{x_2}R_{x_3}C_1C_2s^2 + (1+\alpha_1)R_{x_2}R_{x_3}C_2s + \alpha_2\alpha_3\beta_2\beta_3R_{x_1}}$$

(2.20)

$$\frac{I_{BP_1}}{I_{in}} = \frac{R_{x_2}R_{x_3}C_2s}{R_{x_1}R_{x_2}R_{x_3}C_1C_2s^2 + (1+\alpha_1)R_{x_2}R_{x_3}C_2s + \alpha_2\alpha_3\beta_2\beta_3R_{x_1}} \qquad (2.21)$$

$$I_{BP_2} \qquad \qquad \beta_2R_{x_1}R_{x_3}C_2s \qquad (2.22)$$

$$\frac{\beta P_2}{r_{in}} = -\frac{\beta P_2 r_{11} r_{13} \sigma_2 r_3}{R_{x_1} R_{x_2} R_{x_3} C_1 C_2 s^2 + (1 + \alpha_1) R_{x_2} R_{x_3} C_2 s + \alpha_2 \alpha_3 \beta_2 \beta_3 R_{x_1}}$$

(2.22)

The high pass current is flowing through capacitor  $C_1$ . It can be sensed by connecting another CCCII as a current follower. A current mode notch signal is easily obtained by connecting the  $I_{IIP}$  and  $I_{LP}$  output terminals. Similarly by connecting the  $I_{IIP}$ ,  $I_{BP_1}$ ,  $I_{BP_2}$  and  $I_{LP}$  output terminals, a current mode allpass response is obtained, but with the condition that  $R_{x_1} = R_{x_2}$ .

The center frequency  $w_o$ , bandwidth  $w_o/Q_o$  and quality factor  $Q_o$  are given by,

$$w_{o} = \sqrt{\frac{\alpha_{2}\alpha_{3}\beta_{2}\beta_{3}}{R_{x_{2}}R_{x_{3}}C_{1}C_{2}}}$$

(2.23)

$$\frac{w_o}{Q_o} = \frac{1+\alpha_1}{R_{s_1}C_1}$$

(2.24)

$$Q_o = \frac{R_{x_1}}{1 + \alpha_1} \sqrt{\frac{\alpha_2 \alpha_3 \beta_2 \beta_3 C_1}{R_{x_2} R_{x_3} C_2}}$$

(2.25)

Gain of high pass, lowpass and bandpass are approximately given by,

$$G_{LP} = G_{HP} = 1$$

.  $G_{BP_1} = \frac{1}{2}$ .  $G_{BP_2} = \frac{R_{r_1}}{2R_{r_2}}$  (2.26)

It can be seen from equations (2.23) and (2.24) that the center frequency can be adjusted without disturbing the bandwidth. The center frequency  $w_o$  can be electronically tuned by adjusting  $I_{b_2}$ , whereas the bandwidth  $w_o/Q_o$  can be separately adjusted by  $I_{b_1}$  without disturbing  $w_o$ .

In summary the proposed circuit at most needs four multiple output CCCII for the realization of five basic filter functions, one grounded and one floating capacitor (for the realization of highpass filter) and uses no external resistance.

#### Sensitivity Analysis

From equations (2.23) and (2.24) it is easy to show that the active and passive sensitivities of the parameters  $w_o$  and  $Q_o$  are,

$$S_{\alpha_{2}}^{w_{o}} = S_{\alpha_{3}}^{w_{o}} = S_{\beta_{2}}^{w_{o}} = S_{\beta_{3}}^{w_{o}} = \frac{1}{2} \cdot S_{\alpha_{1}}^{w_{o}} = S_{\beta_{1}}^{w_{o}} = 0$$

$$S_{R_{x_{2}}}^{w_{o}} = S_{R_{x_{1}}}^{w_{o}} = S_{C_{1}}^{w_{o}} = S_{C_{2}}^{w_{o}} = -\frac{1}{2} \cdot S_{R_{x_{1}}}^{w_{o}} = 0$$

$$S_{\alpha_{2}}^{Q_{o}} = S_{\alpha_{3}}^{Q_{o}} = S_{\beta_{2}}^{Q_{o}} = S_{\beta_{3}}^{Q_{o}} = \frac{1}{2} \cdot S_{\beta_{1}}^{Q_{o}} = 0 \cdot S_{\alpha_{1}}^{Q_{o}} l - 1$$

$$-S_{R_{x_{2}}}^{Q_{o}} = -S_{R_{x_{1}}}^{Q_{o}} = -S_{C_{2}}^{Q_{o}} = S_{C_{1}}^{Q_{o}} = \frac{1}{2} \cdot S_{R_{x_{1}}}^{Q_{o}} = 1$$

All of the active and passive sensitivities are small (no more than unity).

#### Simulation Results and Discussion

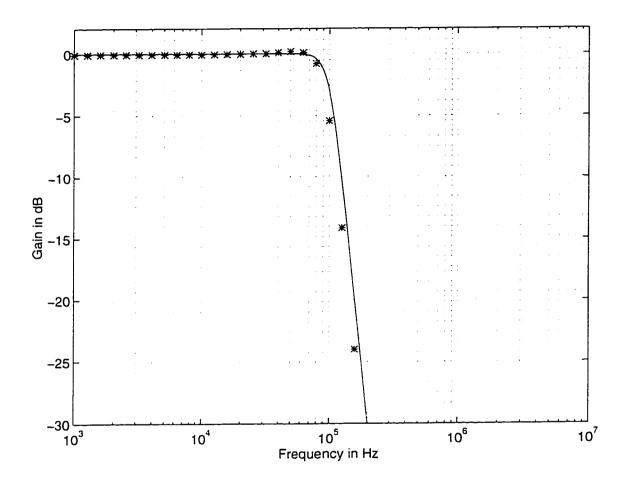

To validate the theoretical analysis, the proposed universal filter in Figure 2.9 is simulated using ICAPS circuit simulation program. The CCCII $\pm$  is modelled by the schematic implementation of Figure 1.15, proposed by Fabre et al. [36] with dc supply voltage of  $\pm 2.5$ V. The simulation results reported here were obtained using the transistors PR100N(PNP) and NR200N(NPN) of the bipolar arrays ALA400 from AT&T [67].

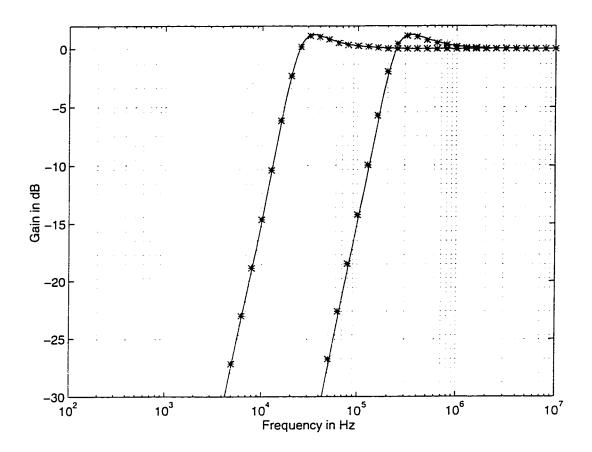

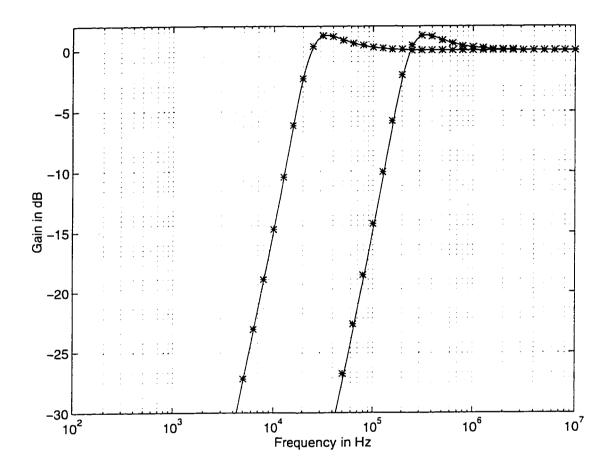

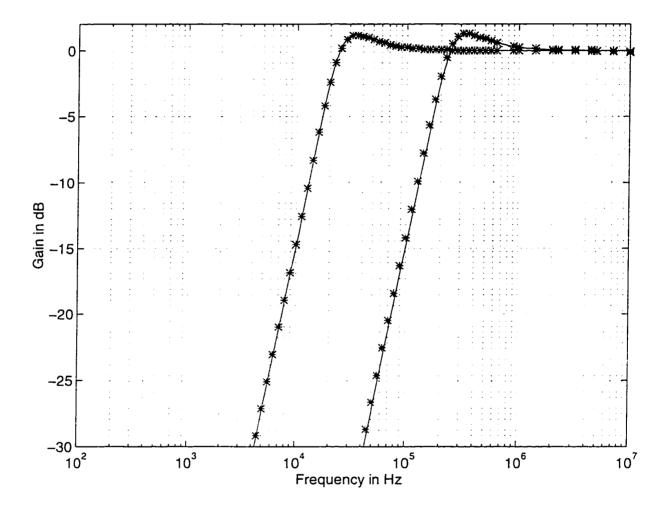

Figures 2.10 to 2.15 show the theoretical and simulation results of lowpass, highpass, bandpass, notch and allpass (gain and phase response) filters respectively. Lowpass, highpass and notch filter results are obtained for (1)24.48kHz and (2)244.8kHz frequencies. Bandpass filter is simulated for (1)50kHz and (2)244.8kHz center frequencies. Allpass filter results are obtained for (1)17.3kHz and (2)173.3kHz frequencies. It can be seen that the simulation results agree very well with the presented theory. Deviation less than 5% are obtained for these results. In short the

proposed circuit offers the following advantages.

- Arbitrary biquadratic transfer functions are realized with single input.

- With multiple outputs all the five basic filter functions can be obtained.

- Center frequency and bandwidth can be independently adjusted.

- No external resistances are used.

- Low active and passive sensitivities.

The disadvantage associated with this filter is that the high pass current is flowing through a capacitor. As a result the capacitor will be floating if this current needs to be sensed. Also the allpass transfer function requires matching condition. To remove these disadvantages another filter is proposed with some modifications.

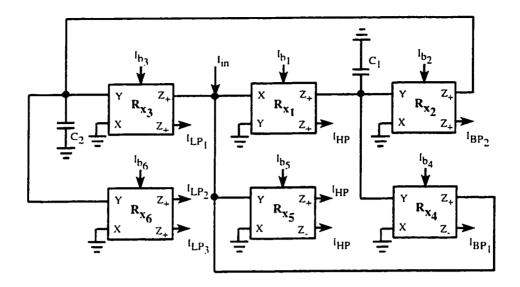

### 2.3.3 Universal Filter 3

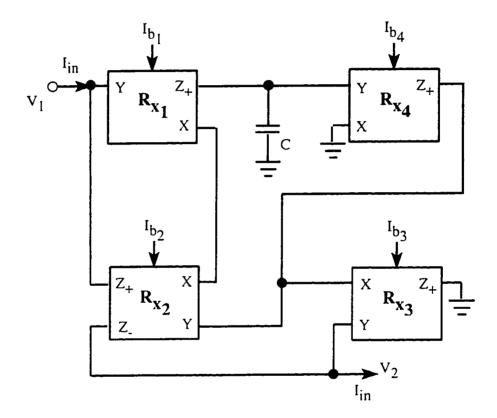

The proposed circuit is shown in Figure 2.16. It is a current-mode circuit using current controlled conveyor (CCCII) with internal resistance  $R_x$ . This filter has four multiple output CCCII, two grounded capacitors and no external resistances. Routine analysis of the circuit assuming ideal CCCII gives the following current transfer functions.

$$\frac{I_{LP}}{I_{in}} = \frac{R_{x_3}}{R_{x_1}R_{x_2}R_{x_3}C_1C_2s^2 + R_{x_1}R_{x_2}C_2s + R_{x_3}}$$

(2.27)

$$\frac{I_{IIP}}{I_{in}} = \frac{R_{x_1}R_{x_2}R_{x_3}C_1C_2s^2}{R_{x_1}R_{x_2}R_{x_3}C_1C_2s^2 + R_{x_1}R_{x_2}C_2s + R_{x_3}}$$

(2.28)

$$\frac{I_{BP_1}}{I_{BP_1}} = \frac{R_{x_1}R_{x_2}C_2s}{R_{x_1}R_{x_2}C_2s}$$

(2.29)

$$\frac{I_{BP_1}}{I_{in}} = \frac{R_{x_1}R_{x_2}C_2s}{R_{x_1}R_{x_2}R_{x_1}C_1C_2s^2 + R_{x_1}R_{x_2}C_2s + R_{x_3}}$$

(2.29)

$$\frac{I_{BP_2}}{I_{in}} = \frac{R_{x_2}R_{x_3}C_2s}{R_{x_1}R_{x_2}R_{x_3}C_1C_2s^2 + R_{x_1}R_{x_2}C_2s + R_{x_3}}$$

(2.30)

Figure 2.10: Simulation results of the lowpass filter. theoretical,\*\*\*simulation (1)  $I_2 = I_3 = 10\mu A$ ,  $I_1 = 5\mu A$ ,  $C_1 = C_2 = 5nF$  (2)  $I_2 = I_3 = 100\mu A$ ,  $I_1 = 50\mu A$ ,  $C_1 = C_2 = 5nF$

Figure 2.11: Simulation results of the high pass filter. theoretical.\*\*\*simulation (1)  $I_2 = I_3 = 10\mu A$ ,  $I_1 = 5\mu A$ ,  $C_1 = C_2 = 5nF$  (2)  $I_2 = I_3 = 100\mu A$ ,  $I_1 = 50\mu A$ ,  $C_1 = C_2 = 5nF$

Figure 2.12: Simulation results of the bandpass filter. -theoretical,\*\*\*simulation (1)  $I_2 = I_3 = 20\mu A$ ,  $I_1 = 2\mu A$ ,  $C_1 = C_2 = 5nF$  (2)  $I_2 = I_3 = 100\mu A$ ,  $I_1 = 10\mu A$ ,  $C_1 = C_2 = 5nF$

Figure 2.13: Simulation results of the notch filter. theoretical,\*\*\*simulation (1)  $I_2 = I_3 = 10\mu A$ ,  $I_1 = 5\mu A$ ,  $C_1 = C_2 = 5nF$  (2)  $I_2 = I_3 = 100\mu A$ ,  $I_1 = 50\mu A$ ,  $C_1 = C_2 = 5nF$

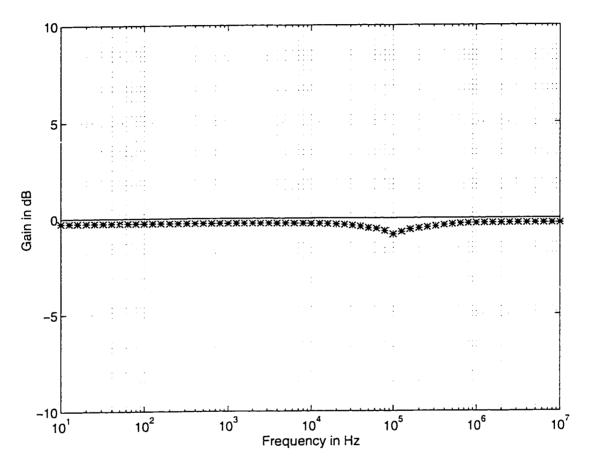

Figure 2.14: Simulation results of the gain of allpass filter. —theoretical, \*\*\*simulation.  $I_2 = I_1 = 5\mu A$ ,  $I_3 = 10\mu A$ ,  $C_1 = C_2 = 5nF$

Figure 2.15: Simulation results of the phase of allpass filter. -theoretical, \*\*\*simulation (1)  $I_2 = I_1 = 5\mu A$ ,  $I_3 = 10\mu A$ ,  $C_1 = C_2 = 5nF$  (2)  $I_2 = I_1 = 50\mu A$ ,  $I_3 = 100\mu A$ ,  $C_1 = C_2 = 5nF$

Figure 2.16: Improved CCCII based Universal second order filter-3.

A current mode notch signal is easily obtained by connecting the  $I_{HP}$  and  $I_{LP}$  output terminals. Let  $I_{NH} = I_{HP} + I_{LP}$ , we obtain the current-mode notch transfer function as,

$$\frac{I_{NII}}{I_{in}} = \frac{R_{x_1}R_{x_2}R_{x_3}C_1C_2s^2 + R_{x_3}}{R_{x_1}R_{x_2}R_{x_3}C_1C_2s^2 + R_{x_1}R_{x_2}C_2s + R_{x_3}}$$

(2.31)

Similarly by connecting the  $I_{IIP}$ ,  $I_{BP_1}$  and  $I_{LP}$  output terminals, a current mode allpass response is obtained

$$\frac{I_{AP}}{I_{in}} = \frac{R_{x_1}R_{x_2}R_{x_3}C_1C_2s^2 - R_{x_1}R_{x_2}C_2s + R_{x_3}}{R_{x_1}R_{x_2}R_{x_3}C_1C_2s^2 + R_{x_1}R_{x_2}C_2s + R_{x_3}}$$

(2.32)

The center frequency  $w_o$ , bandwidth  $w_o/Q_o$  and quality factor  $Q_o$  are given by,

$$w_{\alpha} = \sqrt{\frac{1}{R_{x_1}R_{x_2}C_1C_2}} \tag{2.33}$$

$$\frac{w_o}{Q_o} = \frac{1}{R_{r_3}C_1}$$

(2.34)

$$Q_o = R_{x_1} \sqrt{\frac{C_1}{R_{x_1}R_{x_2}C_2}}$$

(2.35)

Gain of high pass, lowpass and bandpass are approximately given by,

$$G_{LP} = G_{HP} = G_{BP_1} = 1 , \ G_{BP_2} = \frac{R_{x_3}}{R_{x_1}}$$

(2.36)

It can be seen from equations (2.33) and (2.34) that the center frequency can be adjusted without disturbing the bandwidth. The center frequency  $w_o$  can be electronically tuned by adjusting  $I_{b_2}$ , whereas the bandwidth  $w_o/Q_o$  can be separately adjusted by trimming  $I_{b_3}$  without disturbing  $w_o$ . Another important advantage is that no matching condition is required for the realization of allpass and notch functions. Also the proposed filter uses two grounded capacitors which can absorb the stray capacitances. This will result in high frequency operation and less silicon area for implementation. So the disadvantages associated with the previous two circuits are removed.

#### Sensitivity Analysis

Nonideal analysis is required to find the active sensitivities of the filter. Assuming that the nonideal port relations of the CCCII can be expressed as  $v_x = \beta v_y + i_x R_x$ ,  $i_z = \alpha i_x$ , where  $\alpha = 1 - \delta$  ( $|\delta| \ll 1$ ) denotes the current tracking error,  $\beta = 1 - \epsilon$  ( $|\epsilon| \ll 1$ ) represents the voltage traking error. The output current can now be expressed as,

$$\frac{I_{LP}}{I_{in}} = \frac{\alpha_o \alpha_1 \beta_1 \beta_2 R_{x_3}}{R_{x_1} R_{x_2} R_{x_3} C_1 C_2 s^2 + \alpha_o \alpha_3 \beta_3 R_{x_1} R_{x_2} C_2 s + \alpha_o \alpha_1 \alpha_2 \beta_1 \beta_2 R_{x_3}} \quad (2.37)$$

$$\frac{I_{IIP}}{I_{in}} = \frac{R_{r_1}R_{r_2}R_{r_3}C_1C_2s^2}{R_{r_1}R_{r_2}R_{r_3}C_1C_2s^2 + \alpha_o\alpha_3\beta_3R_{r_1}R_{r_2}C_2s + \alpha_o\alpha_1\alpha_2\beta_1\beta_2R_{r_3}}$$

(2.38)

$$\frac{I_{BP_1}}{I_{in}} = \frac{\alpha_o \beta_3 R_{r_1} R_{r_2} C_2 s}{R_{r_1} R_{r_2} R_{r_3} C_1 C_2 s^2 + \alpha_o \alpha_3 \beta_3 R_{r_1} R_{r_2} C_2 s + \alpha_o \alpha_1 \alpha_2 \beta_1 \beta_2 R_{r_3}}$$

(2.39)

$$\frac{I_{BP_2}}{I_{in}} = \frac{\alpha_o \beta_1 R_{x_2} R_{x_3} C_{2S}}{R_{x_1} R_{x_2} R_{x_3} C_1 C_2 s^2 + \alpha_o \alpha_3 \beta_3 R_{x_1} R_{x_2} C_2 s + \alpha_o \alpha_1 \alpha_2 \beta_1 \beta_2 R_{x_3}}$$

(2.40)

The center frequency  $w_o$ , bandwidth  $w_o/Q_o$  and quality factor  $Q_o$  are given by,

$$w_o = \sqrt{\frac{\alpha_o \alpha_1 \alpha_2 \beta_1 \beta_2}{R_{x_1} R_{x_2} C_1 C_2}} \tag{2.41}$$

$$\frac{w_o}{Q_o} = \frac{\alpha_o \alpha_3 \beta_3}{R_{r_3} C_1} \tag{2.42}$$

$$Q_o = \frac{R_{x_3}}{\alpha_3 \beta_3} \sqrt{\frac{\alpha_1 \alpha_2 \beta_1 \beta_2 C_1}{\alpha_o R_{x_1} R_{x_2} C_2}}$$

(2.43)

From equations (2.41) and (2.43) it is easy to show that the active and passive sensitivities of the parameters  $w_o$  and  $Q_o$  are.

$$\begin{split} S_{\alpha_{\sigma}}^{w_{\sigma}} &= S_{\alpha_{1}}^{w_{\sigma}} = S_{\alpha_{2}}^{w_{\sigma}} = S_{\beta_{1}}^{w_{\sigma}} = S_{\beta_{2}}^{w_{\sigma}} = \frac{1}{2} \ . \ S_{\alpha_{3}}^{w_{\sigma}} = S_{\beta_{\sigma}}^{w_{\sigma}} = S_{\beta_{3}}^{w_{\sigma}} = 0 \\ S_{R_{r_{1}}}^{w_{\sigma}} &= S_{R_{r_{2}}}^{w_{\sigma}} = S_{C_{1}}^{w_{\sigma}} = S_{C_{2}}^{w_{\sigma}} = -\frac{1}{2} \ . \ S_{R_{r_{3}}}^{w_{\sigma}} = 0 \\ S_{\alpha_{\sigma}}^{Q_{\sigma}} &= S_{\alpha_{1}}^{Q_{\sigma}} = S_{\alpha_{2}}^{Q_{\sigma}} = S_{\beta_{1}}^{Q_{\sigma}} = S_{\beta_{2}}^{Q_{\sigma}} = \frac{1}{2} \ . \ S_{\alpha_{3}}^{Q_{\sigma}} = S_{\beta_{3}}^{Q_{\sigma}} = -1 \ . \ S_{\beta_{\sigma}}^{Q_{\sigma}} = 0 \\ -S_{R_{r_{1}}}^{Q_{\sigma}} &= -S_{R_{r_{2}}}^{Q_{\sigma}} = S_{C_{1}}^{Q_{\sigma}} = -S_{C_{2}}^{Q_{\sigma}} = \frac{1}{2} \ . \ S_{R_{r_{3}}}^{Q_{\sigma}} = 1 \ . \ S_{C_{1}}^{Q_{\sigma}} = \frac{1}{2} \end{split}$$

All of the active and passive sensitivities are small (no more than unity).

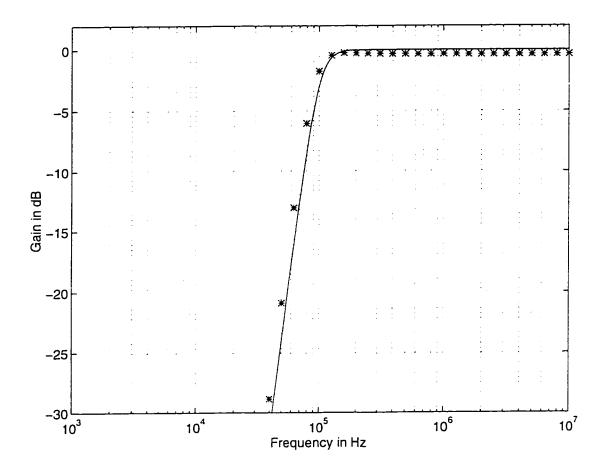

#### Simulation Results and Discussion

To validate the theoretical analysis, the proposed universal filter in Figure 2.16 is simulated using ICAPS circuit simulation program. The CCCII $\pm$  is modelled by the schematic implementation of Figure 1.15, proposed by Fabre et al. [36] with dc supply voltage of  $\pm 2.5$ V. The filter characteristics here were obtained using the transistors PR100N(PNP) and NR200N(NPN) of the bipolar arrays ALA400 from AT&T [67].

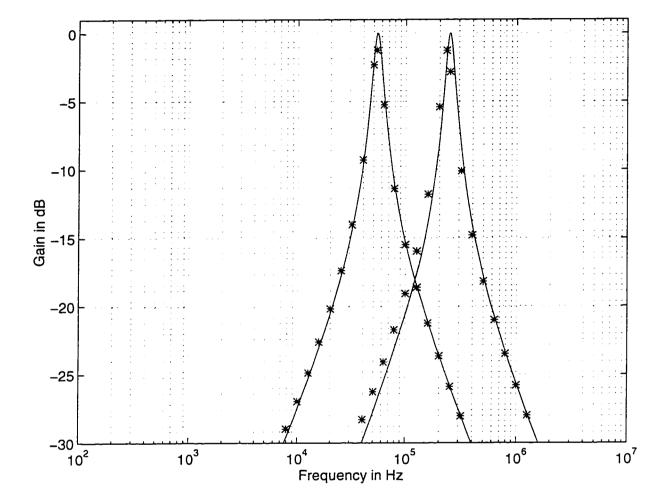

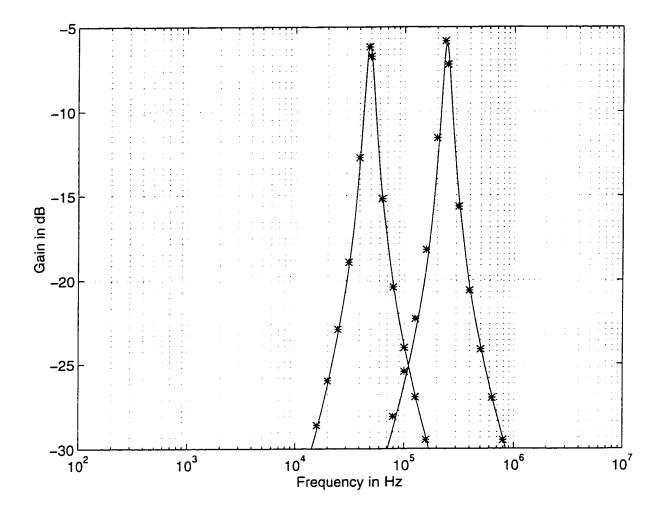

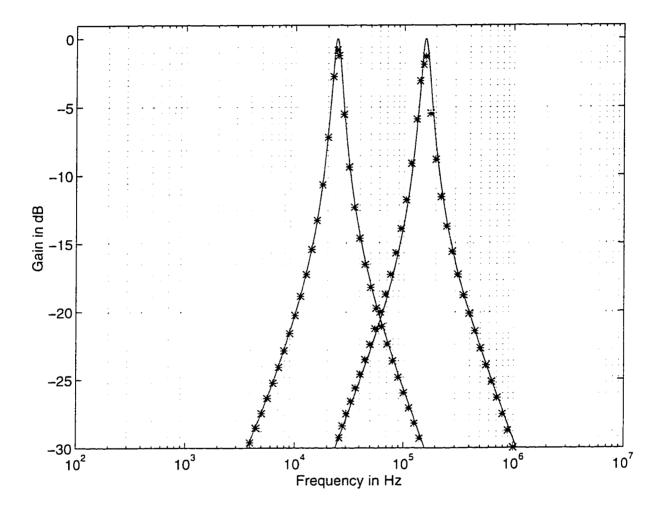

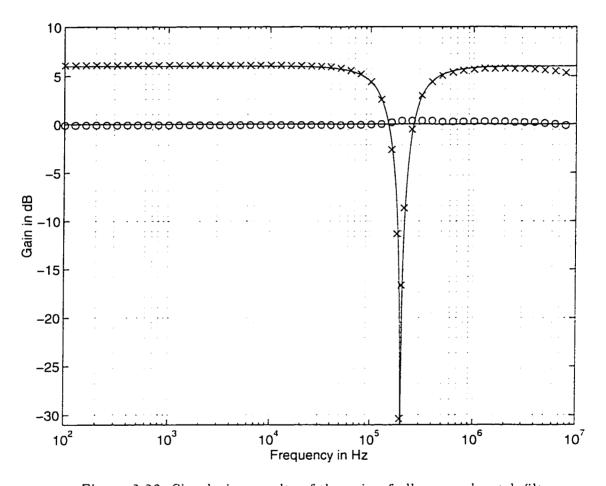

Figures 2.17 to 2.22 show the theoretical and simulation results of lowpass, highpass, bandpass, notch and allpass (gain and phase response) filters respectively. Lowpass, highpass, notch and allpass filters are simulated for (1)24.48kHz

Figure 2.17: Simulation results of the lowpass filter. theoretical,\*\*\*simulation (1)  $I_o = 100\mu A$ ,  $I_1 = I_2 = I_3 = 10\mu A$ ,  $C_1 = C_2 = 5nF$  (2)  $I_o = 100\mu A$ ,  $I_1 = I_2 = I_3 = 100\mu A$ ,  $C_1 = C_2 = 5nF$

Figure 2.18: Simulation results of the highpass filter. theoretical.\*\*\*simulation (1)  $I_o = 100\mu A$ ,  $I_1 = I_2 = I_3 = 10\mu A$ ,  $C_1 = C_2 = 5nF$  (2)  $I_o = 100\mu A$ ,  $I_1 = I_2 = I_3 = 100\mu A$ ,  $C_1 = C_2 = 5nF$

Figure 2.19: Simulation results of the bandpass filter. theoretical, \*\*\*simulation (1)  $I_o = 100\mu A$ ,  $I_1 = I_2 = 10\mu A$ ,  $I_3 = 2\mu A$ ,  $C_1 = C_2 = 5nF$  (2)  $I_o = 100\mu A$ ,  $I_1 = 10\mu A$ ,  $I_2 = 520\mu A$ ,  $I_3 = 15\mu A$ ,  $C_1 = C_2 = 5nF$

Figure 2.20: Simulation results of the notch filter. theoretical. \*\*\*simulation (1)  $I_o = 100\mu A$ ,  $I_1 = I_2 = 10\mu A$ ,  $I_3 = 14.14\mu A$ ,  $C_1 = C_2 = 5nF$  (2)  $I_o = 100\mu A$ ,  $I_1 = I_2 = 100\mu A$ ,  $I_3 = 141.4$ ,  $\mu A$ ,  $C_1 = C_2 = 5nF$

Figure 2.21: Simulation results of the gain of allpass filter. theoretical, \*\*\*simulation.  $I_o = 100\mu A$ ,  $I_1 = I_2 = 10\mu A$ ,  $I_3 = 14.14\mu A$ ,  $C_1 = C_2 = 5nF$

and (2)244.8kHz frequencies. Bandpass filter is simulated for (1)24.48kHz and (2)176.56kHz frequencies. It can be seen that the simulation results agree very well with the presented theory. Deviation less than 5% are obtained for these results. In short the proposed circuit offers the following advantages.

- Arbitrary biquadratic transfer functions are realized with single input.

- With multiple outputs all the five basic filter functions can be obtained.

- Center frequency  $w_o$  and bandwidth  $w_o/Q_o$  can be independently adjusted.

- No external resistances are used.

- grounded capacitors are used.

- No matching conditions are required for the realization of allpass and notch transfer functions.

- Low active and passive sensitivities.

To show the merits and demerits of the proposed filter designs, Table 2.1 shows a comparison with the most recently published CCCII programmable current mode universal filter [50]. Comparison shows that the proposed filter is a better option for universal filter as it uses grounded capacitors and can realize all five transfer functions without any realization conditions.

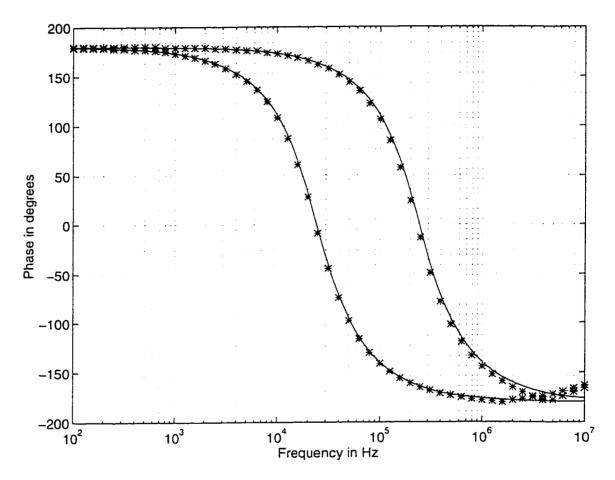

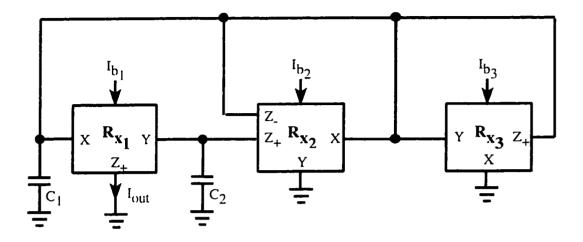

### 2.3.4 Universal Filter 4

A new interesting universal filter can be obtained by connecting two more multiple output current controlled conveyors in parallel to the CCCII-0 and CCCII-2. The

|                              | Universal Filter | Proposed CCCII  | Proposed CCCII  |

|------------------------------|------------------|-----------------|-----------------|

|                              | 1997[50]         | Filter 1        | Filter 3        |

| $w_o$ and $w_o/Q_o$ relation | Independent      | Dependent       | Independent     |

| No. of active elements       | Five             | Four            | Four            |

| No. of capacitors            | Two              | Two             | Two             |

| No. of floating capacitors   | Two              | One             | None            |

| Controlling $w_o$            | Biasing current  | Biasing current | Biasing current |

| Controlling $w_o/Q_o$        | Biasing current  |                 | Biasing current |

| Active/passive sensitivity   | Low              | Low             | Low             |

| Notch/allpass functions      | Not realizable   | Realizable      | Realizable      |

| Realization conditions       |                  | None            | None            |

Table 2.1: Comparison between the proposed CCCII unviersal filters and the previously published filter.

resulting circuit is shown in Figure 2.23. Routine analysis of the circuit assuming ideal CCCII gives the following current transfer functions.

$$\frac{I_{LP_1}}{I_{in}} = \frac{R_{x_4}}{R_{x_2}R_{x_3}R_{x_4}C_1C_2s^2 + R_{x_2}R_{x_3}C_2s + R_{x_4}}$$

(2.44)

$$\frac{I_{LP_2}}{I_{in}} = \frac{I_{LP_3}}{I_{in}} = \frac{R_{x_3}}{R_{x_6}} I_{LP_1}$$

(2.45)

$$\frac{I_{IIP_1}}{I_{in}} = \frac{R_{r_2}R_{r_3}R_{r_4}C_1C_2s^2}{R_{r_3}R_{r_4}C_1C_2s^2 + R_{r_3}R_{r_3}C_2s + R_{r_4}}$$

(2.46)

$$\frac{I_{IIP_2}}{I_{in}} = -\frac{I_{IIP_1}}{I_{in}} = \frac{R_{r_1}}{R_{r_2}} I_{IIP_1}$$

(2.47)

$$\frac{I_{BP_1}}{I_{in}} = \frac{R_{r_2}R_{r_3}C_{2s}}{R_{r_2}R_{r_3}R_{r_4}C_{1}C_{2s}^{2} + R_{r_5}R_{r_5}C_{2s} + R_{r_4}}$$

(2.48)

$$\frac{I_{BP_2}}{I_{in}} = \frac{R_{r_1}R_{r_4}C_{1}C_{2}s}{R_{r_2}R_{r_3}R_{r_4}C_{1}C_{2}s^2 + R_{r_2}R_{r_3}C_{2}s + R_{r_4}}$$

(2.49)

The gains of these transfer functions are approximately given by.

$$G_{LP_1} = G_{HP_1} = G_{BP_1} = 1, \ G_{LP_2} = G_{LP_3} = \frac{R_{x_3}}{R_{x_6}},$$

(2.50)

$$G_{IIP_2} = -G_{IIP_1} = \frac{R_{x_1}}{R_{x_1}}, \ G_{BP_2} = \frac{R_{x_4}}{R_{x_2}}$$

(2.51)

Figure 2.23: Multiple filter functions. CCCII based Universal second order filter-4.

The outputs of  $I_{LP_2}$ ,  $I_{IIP_2}$  and  $I_{BP_2}$  can be used for lowpass, highpass and bandpass filters with adjustable gain. The outputs of  $I_{LP_1}$ ,  $I_{IIP_1}$  and  $I_{BP_1}$  can be connected together for allpass response with a gain of unity and without any matching conditions. The outputs of  $I_{LP_1}$  and  $I_{IIP_1}$  can be connected together to get the notch function with adjustable gain. In this way all the five basic transfer functions are available simultaneously.

The center frequency  $w_o$ , bandwidth  $w_o/Q_o$  and quality factor  $Q_o$  are given by,

$$w_o = \sqrt{\frac{1}{R_{x_2}R_{x_3}C_1C_2}} \tag{2.52}$$

$$\frac{w_o}{Q_o} = \frac{1}{R_{x_4}C_1} \tag{2.53}$$

$$Q_o = R_{r_4} \sqrt{\frac{C_1}{R_{r_2}R_{r_3}C_2}}$$

(2.54)

It can be seen that the center frequency and bandwidth are independently adjustable. In addition to all the advantages available in the previous filter such as grounded capacitors, no matching conditions, low sensitivity etc. this filter has some more advantages. The gain of lowpass, highpass and notch is independently adjustable by  $R_{x_6}$  and  $R_{x_5}$  respectively. The gain of bandpass filter is orthogonally adjustable. All five functions are simultaneously available.

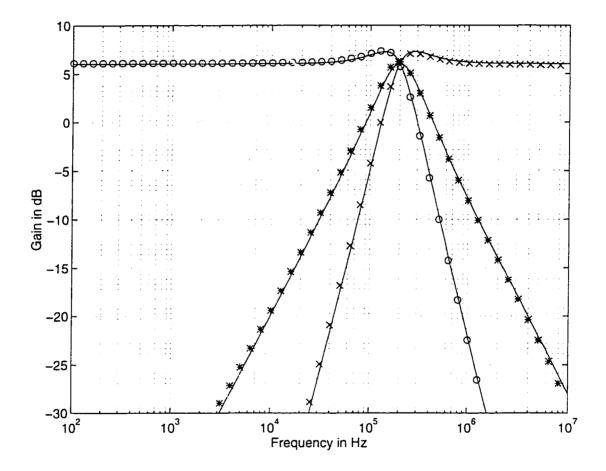

#### Simulation Results and Discussion

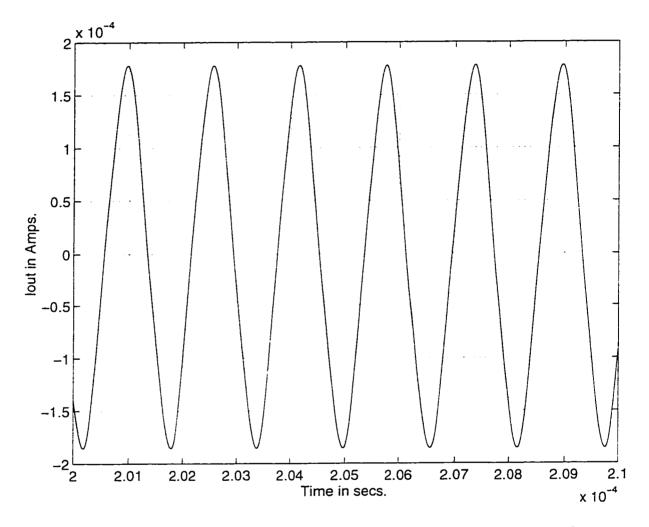

To validate the theoretical analysis, the proposed universal filter is simulated using ICAPS circuit simulation program. The CCCII $\pm$  is modelled by the schematic implementation of Figure 1.15, proposed by Fabre et al. [36] with dc supply voltage of  $\pm 2.5V$ . The filter characteristics here were obtained using the transistors PR100N(PNP) and NR200N(NPN) of the bipolar arrays ALA400 from AT&T [67].

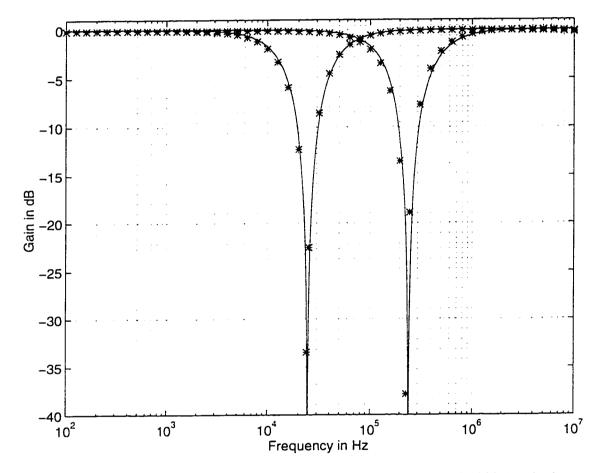

Figures 2.24 to 2.26 show the theoretical and simulation results of lowpass, highpass, bandpass, notch and allpass (gain and phase response) filters respectively. It can be seen that the simulation results agree very well with the presented theory.

## 2.4 SINUSOIDAL OSCILLATORS