### Fault Characterization and Testability Considerations in Multi-Valued Logic Circuits

by

#### Maher Mohammed Mahmoud Al-Sharif

### A Thesis Presented to the

### FACULTY OF THE COLLEGE OF GRADUATE STUDIES

### KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

### DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

### **MASTER OF SCIENCE**

In

### **COMPUTER ENGINEERING**

December, 1998

### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

UMI®

# **NOTE TO USERS**

This reproduction is the best copy available.

UMI®

.

# Fault Characterization and Testability Considerations in Multi-Valued Logic Circuits

BY

Maher Mohammed Mahmoud Al-Sharif

A Thesis Presented to the FACULTY OF THE COLLEGE OF GRADUATE STUDIES

KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

# MASTER OF SCIENCE

COMPUTER ENGINEERING

December, 1998

UMI Number: 1403696

# UMI®

UMI Microform 1403696

Copyright 2001 by Bell & Howell Information and Learning Company. All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

> Bell & Howell Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

### KING FAHD UNIVERSITY OF PETROLEUM AND MINERALS DHAHRAN 31261, SAUDI ARABIA

### COLLEGE OF GRADUATE STUDIES

This thesis written by

#### Maher Mohammed Al-Sharif

under the direction of his Thesis Advisor and approved by his Thesis Committee,

has been presented to and accepted by the Dean of the College of Graduate Studies,

in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE IN COMPUTER ENGINEERING

Thesis Committee: Dr. Mohammed Osman (Chairman) Barr (Co – Chairman) DrMostafa Abd - El 2 (Member) din Amin

Department Chairman a ban/Inte Almojel

Dean, College of Graduate Studies

$\frac{3\circ - 1 - 99}{Date}$

### To my Family

and to

### Bait Tema people

#### Acknowledgments

All praise be to Allah for his limitless help and guidance. Peace and blessings of Allah be upon His prophet Muhammad.

Acknowledgment is due to King Fahd University of Petroleum and Minerals, Dhahran, Saudi Arabia, for the generous support for this research. I would like to express my profound gratitude and appreciation to my advisors, Dr. Mohammed Osman and Dr. Mostafa Abd-El-Barr for their support and patience throughout this thesis. Their continuous support and encouragement can never be forgotten. I would like to thank Dr. Alaaeldin Amin for his consistent support and valuable discussions.

I also wish to thank faculty, graduate students, and the staff members of the Computer Engineering Department for their support. The encouragement and good wishes of my friends, Abdallah Rayhan, Maher Mutlaq, Raed Basha, Jamil Sangrar, Ahmad Ashadawi, Samer Saed, Kalil Balawi, Abdul Rahman Abdul Raheem, Firas Maadi, Ihab Al-Saqqa and Mohammed Bawadi are also worthy acknowledged. Special thanks must be given to my father, the family and my wife for their encouragement and moral support.

# Contents

|   | $\mathbf{List}$ | of Tables                                   | viii |

|---|-----------------|---------------------------------------------|------|

|   | List            | of Figures                                  | x    |

|   | Abs             | stract (English)                            | xiii |

|   | Abs             | stract (Arabic)                             | xv   |

| 1 | Intr            | oduction                                    | 1    |

|   | 1.1             | General                                     | 1    |

|   | 1.2             | Motivation                                  | 2    |

|   | 1.3             | Objectives                                  | 3    |

|   | 1.4             | Thesis Outline                              | 4    |

| 2 | Bac             | kground Material                            | 6    |

|   | 2.1             | Functionally Complete Sets of MVL Operators | 7    |

|   |                 | 2.1.1 Definitions                           | 8    |

|   |                | 2.1.2    | CMOS Circuit Realizations                     | 9  |

|---|----------------|----------|-----------------------------------------------|----|

|   | 2.2            | Testal   | oility Issues in MVL Circuits                 | 16 |

|   |                | 2.2.1    | K-enabled Gates and Fault Propagation         | 17 |

| 3 | Lite           | erature  | e Review                                      | 22 |

| 4 | $\mathbf{Phy}$ | vsical I | Defect Modeling and Simulation                | 31 |

|   | 4.1            | Physic   | cal Defects                                   | 31 |

|   |                | 4.1.1    | Physical Defects & Faults                     | 33 |

|   |                | 4.1.2    | Spot Defects                                  | 34 |

|   | 4.2            | Fault    | Characterization                              | 36 |

|   |                | 4.2.1    | Device Level Fault Characterization           | 36 |

|   |                | 4.2.2    | Layout Level Fault Characterization           | 39 |

|   |                | 4.2.3    | Comparison                                    | 42 |

| 5 | Fau            | lt Cha   | racterization of the MVL Set                  | 43 |

|   | 5.1            | The A    | .pproach                                      | 44 |

|   | 5.2            | Fault    | Characterization of the Literal               | 48 |

|   | 5.3            | Fault    | Characterization of the Complement of Literal | 57 |

|   | 5.4            | Fault    | Characterization of the Cycle                 | 64 |

|   | 5.5            | Fault    | Characterization of the <i>tSum</i>           | 71 |

|   | 5.6            | Fault    | Characterization of the <i>Min</i>            | 74 |

|   | 5.7  | Fault Characterization Summary             | 80 |

|---|------|--------------------------------------------|----|

| 6 | Test | ting of the MVL Set                        | 81 |

|   | 6.1  | Testing of the Literal                     | 82 |

|   | 6.2  | Testing of the Complement of Literal       | 89 |

|   | 6.3  | Testing of the Cycle                       | 89 |

|   | 6.4  | Testing of the $tSum$                      | 95 |

|   | 6.5  | Testing of the Min                         | 01 |

|   | 6.6  | Peculiar Faults Testing and Fault Coverage | 08 |

|   |      | 6.6.1 Oscillations Fault                   | 09 |

|   |      | 6.6.2 A Soft Error                         | 11 |

|   |      | 6.6.3 3* Faults                            | 11 |

| 7 | Des  | ign for Testability 11                     | 16 |

|   | 7.1  | An Application                             | 17 |

| 8 | Disc | cussion and Conclusions                    | 22 |

|   | 8.1  | Summary of the Main Results of the Thesis  | 23 |

|   | 8.2  | Future Work                                | 24 |

|   | Bibl | liography 12                               | 26 |

|   | Vita | 13                                         | 31 |

# List of Tables

| 5.1 | Fault characterization of the literal circuit.              | 58 |

|-----|-------------------------------------------------------------|----|

| 5.2 | Fault characterization of the complement of literal circuit | 65 |

| 5.3 | Fault characterization of the cycle circuit.                | 72 |

| 5.4 | Fault characterization of the <i>tSum</i> circuit.          | 76 |

| 5.5 | Fault characterization of the <i>min</i> circuit            | 79 |

| 5.6 | Summery of the characterized fault categories               | 80 |

| 6.1 | Exhaustive test list for the literal circuit                | 86 |

| 6.2 | Fault coverage tables for $k^1[x]^1$                        | 88 |

| 6.3 | Literal tests                                               | 89 |

| 6.4 | Minimal test sets/sequences for the literal                 | 90 |

| 6.5 | Exhaustive test list for the complement of literal          | 91 |

| 6.6 | Complement of literal tests.                                | 93 |

| 6.7 | Minimal test sets/sequences for the complement of literal   | 94 |

| 6.8 | Exhaustive test list for the cycle.                         | 96 |

| 6.9  | Cycle tests                                                                 |

|------|-----------------------------------------------------------------------------|

| 6.10 | Minimal test sets/sequences for the cycle                                   |

| 6.11 | Exhaustive test list for the sequential faults in the $tSum$ 99             |

| 6.12 | Exhaustive test list for the functional faults in the $tSum$ 100            |

| 6.13 | <i>tSum</i> tests                                                           |

| 6.14 | Exhaustive test list for the <i>min</i> , sequential part 1                 |

| 6.15 | Exhaustive test list for the <i>min</i> , sequential part 2                 |

| 6.16 | Exhaustive test list (in terms of I2) for the $min$ , sequential part 3 105 |

| 6.17 | I2 values and the corresponding $\langle x, y \rangle$ input values         |

| 6.18 | Exhaustive test list for the min, sequential part 3                         |

| 6.19 | Exhaustive test list for the <i>min</i> , functional part 1                 |

| 6.20 | Exhaustive test list for the <i>min</i> , functional part 2                 |

| 6.21 | Minimal test sets/sequences for the min                                     |

| 6.22 | Fault coverage figures and 3* testing                                       |

| 7.1  | Truth table for an MVL full adder                                           |

| 8.1  | Summery of the characterized fault categories                               |

# List of Figures

| 2.1  | Basic circuit elements for CMCL.                                                                         | 11 |

|------|----------------------------------------------------------------------------------------------------------|----|

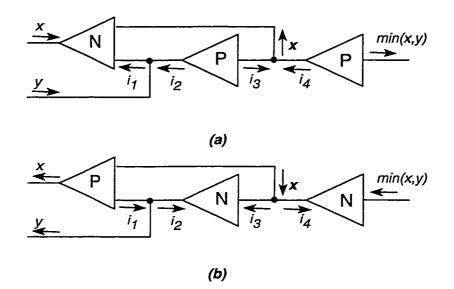

| 2.2  | Circuit realizing <i>min</i> operator. (a): input currents are sinking, (b): input currents are sourcing | 12 |

| 2.3  | Transient-time response of the <i>min</i> operator                                                       | 12 |

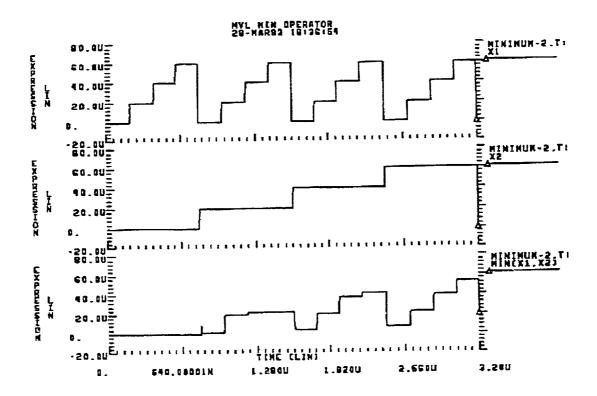

| 2.4  | Circuit realization of <i>tsum</i>                                                                       | 13 |

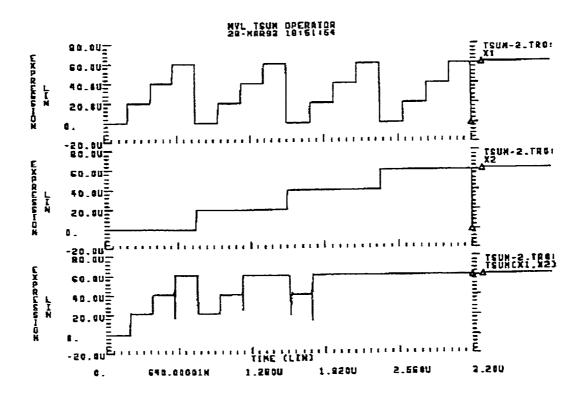

| 2.5  | Transient-time response of the <i>tsum</i> operator                                                      | 13 |

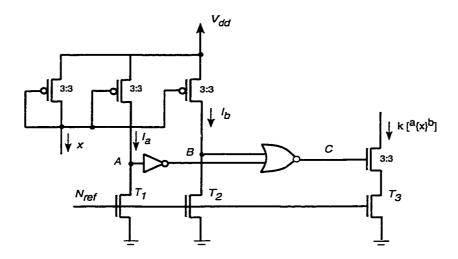

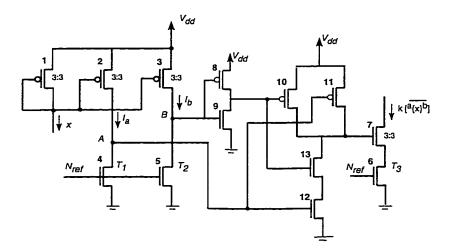

| 2.6  | Realization of a <i>literal</i> $k[^a \{x\}^b]$ operator                                                 | 14 |

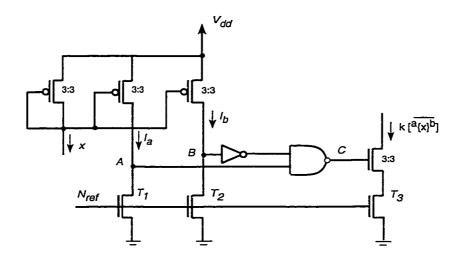

| 2.7  | Realization of a <i>complement of literal</i> $\overline{k[^a\{x\}^b]}$ operator                         | 14 |

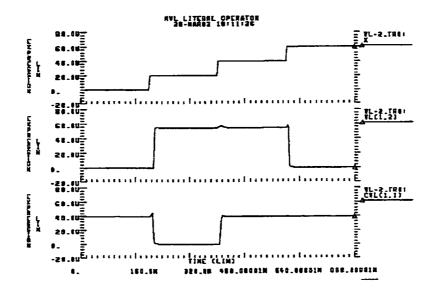

| 2.8  | Transient-time response of $3[1{x}^2]$ and $\overline{2[1{x}^1]}$ operators                              | 15 |

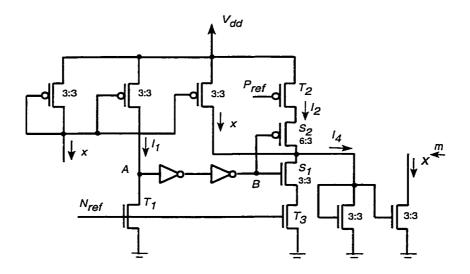

| 2.9  | Circuit realization of the <i>cycle</i> operator.                                                        | 15 |

| 2.10 | Transient-time response of the <i>cycle</i> operator                                                     | 16 |

| 2.11 | k-enabled gates                                                                                          | 18 |

| 2.12 | Fully enabled gate                                                                                       | 20 |

| 2.13 | 1-enabled gate                                                                                           | 20 |

| 3.1  | Different D-chains propagation.                                                                          | 24 |

| 3.2  | Event driven fault simulation.                                                    | 28 |

|------|-----------------------------------------------------------------------------------|----|

| 3.3  | Example for <i>free vertical crossover</i> genetic operator                       | 30 |

| 4.1  | Spot defects overlapping two or more wires.                                       | 34 |

| 4.2  | Open and short faults and their models                                            | 39 |

| 5.1  | Open and short faults and their models                                            | 45 |

| 5.2  | Literal transistor diagram                                                        | 50 |

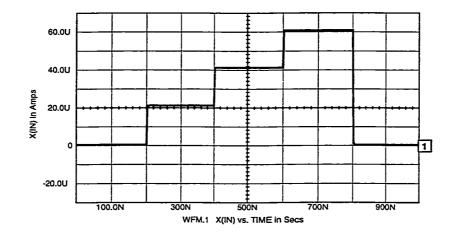

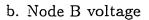

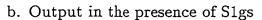

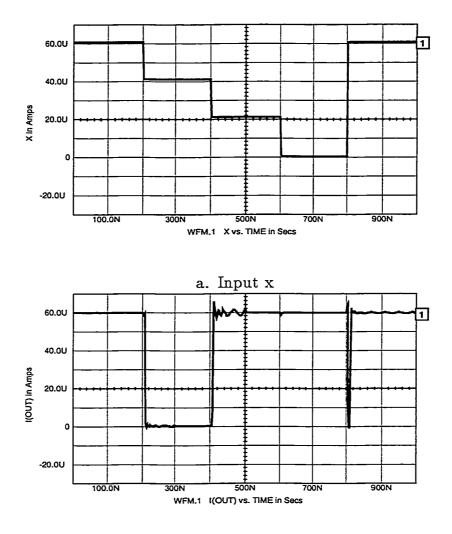

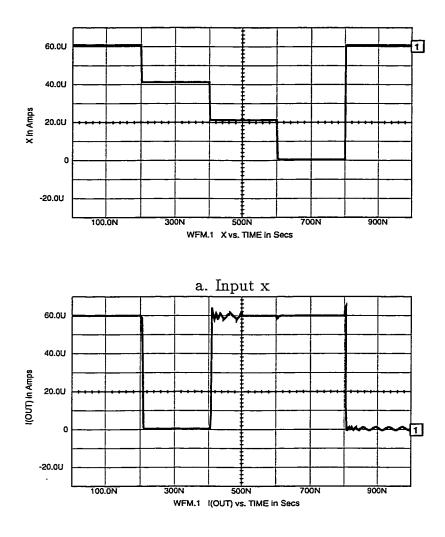

| 5.3  | Response of the literal, $3^1[x]^1$                                               | 51 |

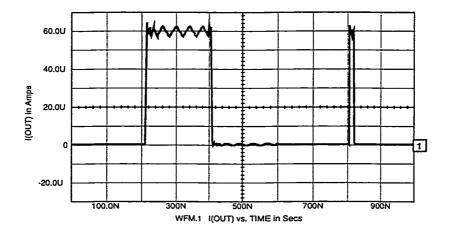

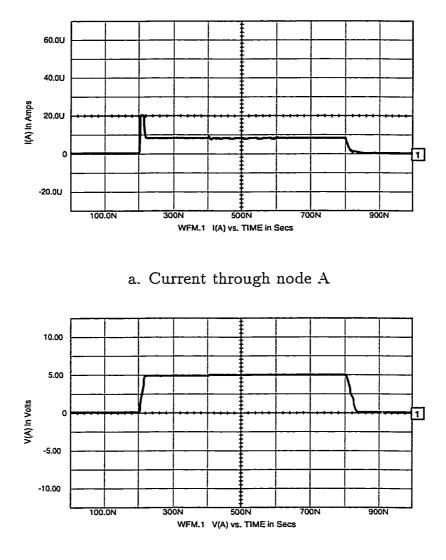

| 5.4  | Node A current and voltage                                                        | 52 |

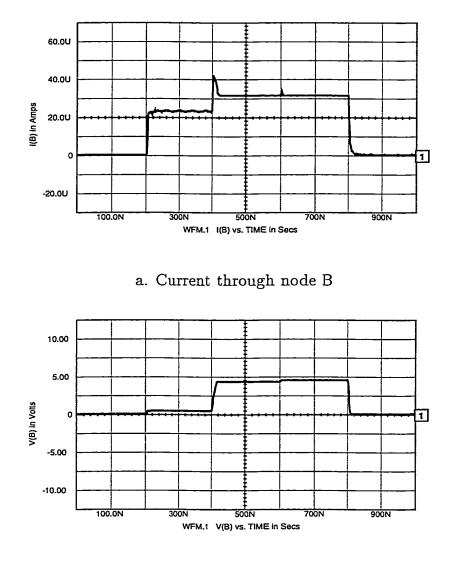

| 5.5  | Node B current and voltage                                                        | 53 |

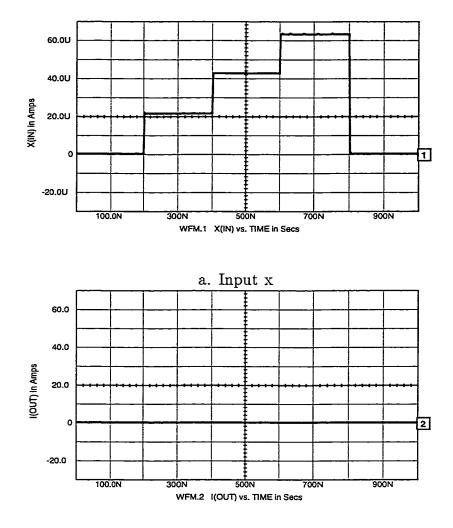

| 5.6  | Response of the circuit for literal $3^1[x]^1$ in the presence of S1gs            | 54 |

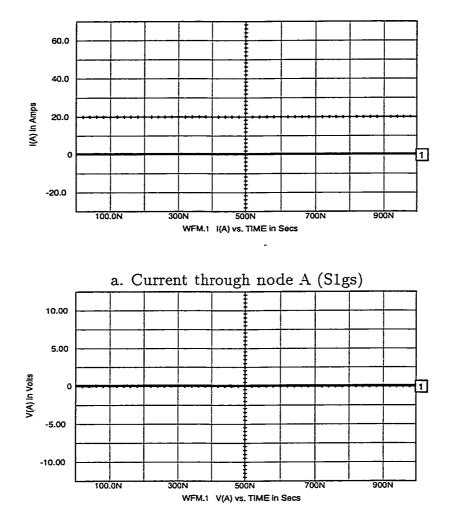

| 5.7  | Node A current and voltage in the presence of S1gs                                | 55 |

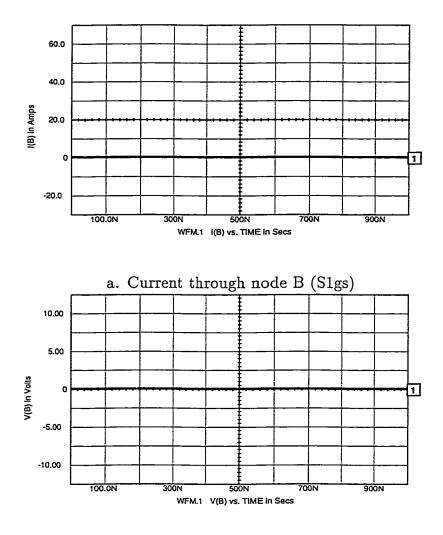

| 5.8  | Node B current and voltage in the prsence of S1gs                                 | 56 |

| 5.9  | Complement of Literal transistor diagram                                          | 60 |

| 5.10 | Response of the complement of literal, $\overline{2^2[x]^3}$                      | 61 |

| 5.11 | Response of the complement of literal, $\overline{3^2[x]^2}$                      | 62 |

| 5.12 | Response of the complement of literal, $\overline{3^2[x]^2}$ in the presence O10d | 63 |

| 5.13 | Cycle transistor diagram                                                          | 67 |

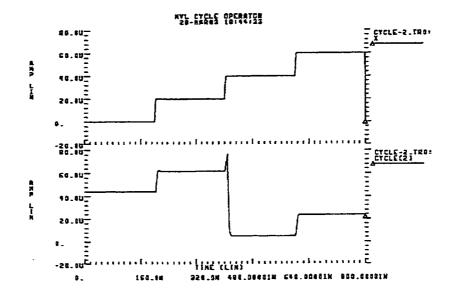

| 5.14 | Response of the cycle, $X^{\leftarrow 1}$                                         | 68 |

| 5.15 | Response of the cycle, $X^{\leftarrow 2}$                                         | 69 |

| 5.16 | Response of the cycle, $X^{-2}$ in the presence of O13d              |

|------|----------------------------------------------------------------------|

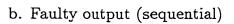

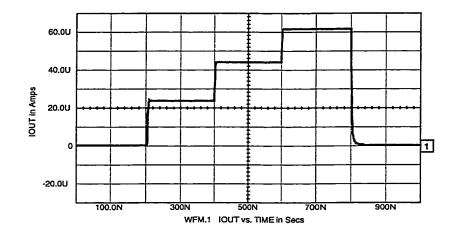

| 5.17 | tSum transistor diagram                                              |

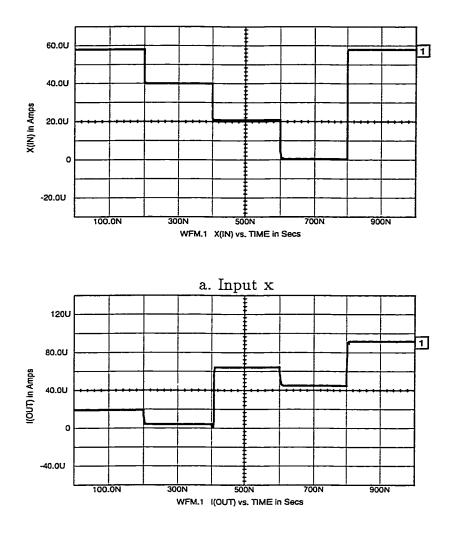

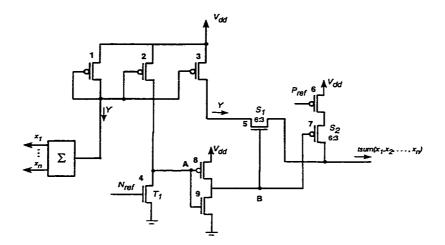

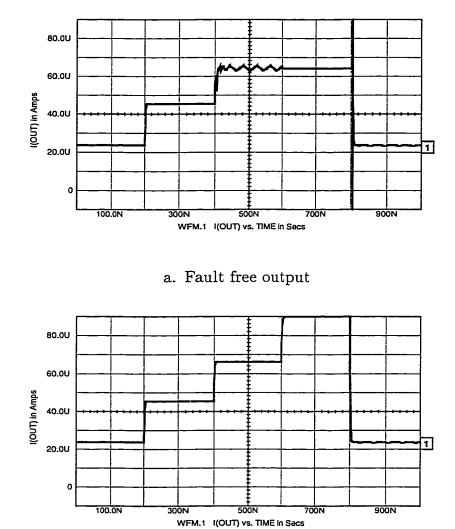

| 5.18 | Response of a $tSum$ circuit                                         |

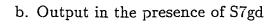

| 5.19 | Response of a $tSum$ circuit in the presence of O3d                  |

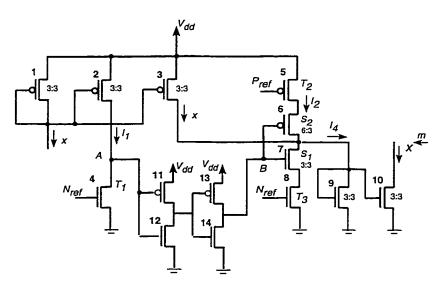

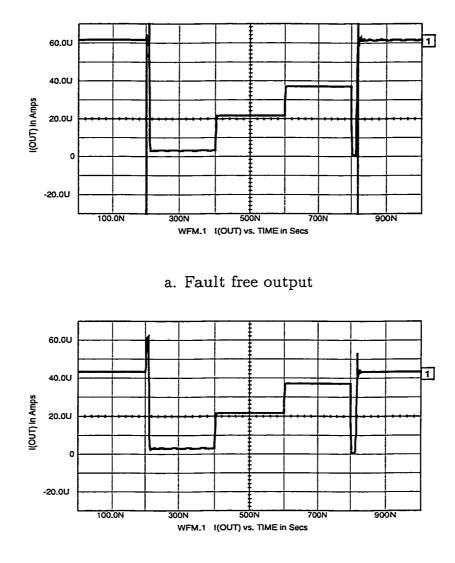

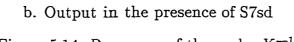

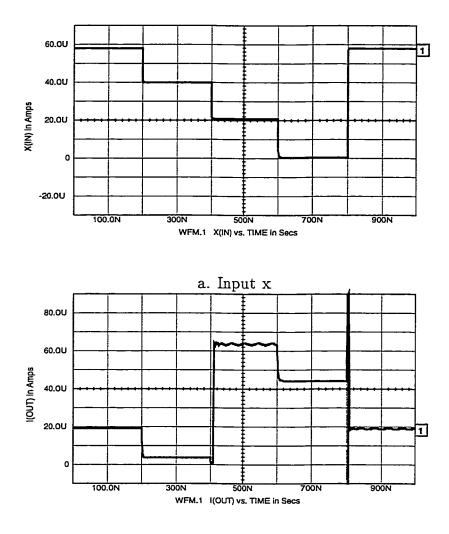

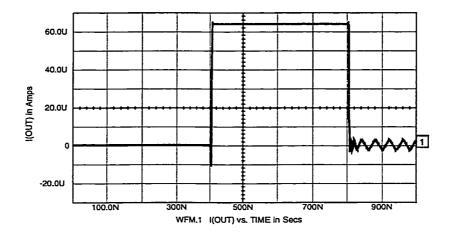

| 5.20 | Min transistor diagram                                               |

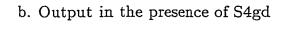

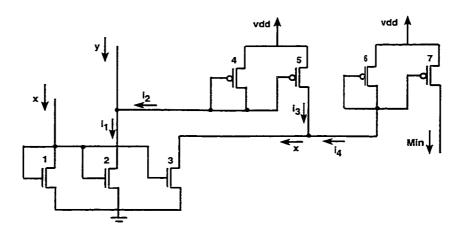

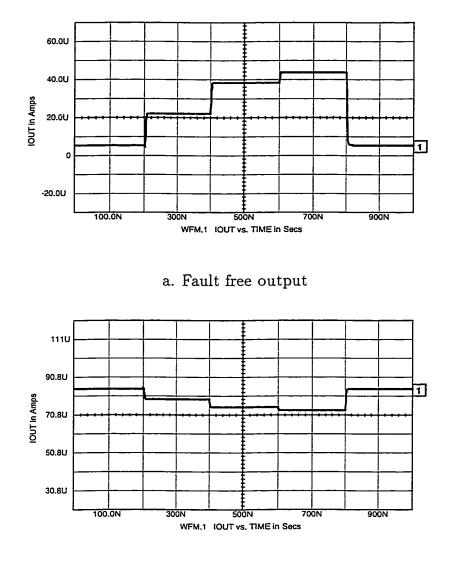

| 5.21 | Response of a <i>min</i> circuit                                     |

| 5.22 | Response of a <i>min</i> circuit in the presence of O5s. $\ldots$ 79 |

| 6.1  | Fault S6gd charging and discharging paths (the literal circuit) 110  |

| 6.2  | Fault S3gd charging and discharging paths (the $tSum$ circuit) 110   |

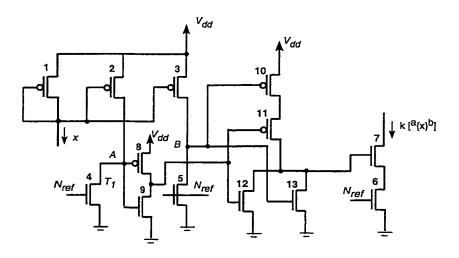

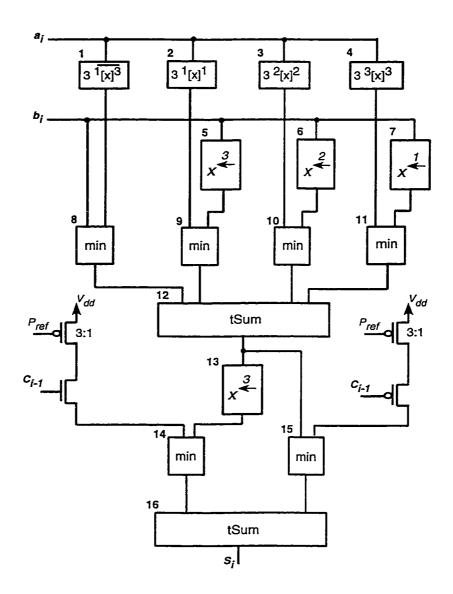

| 7.1  | A 4-valued adder                                                     |

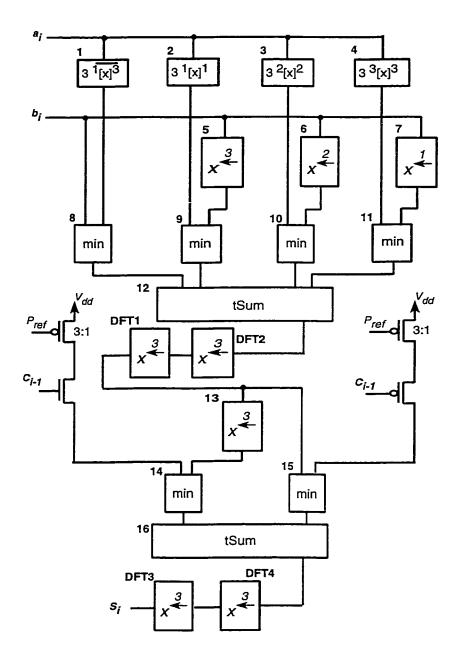

| 7.2  | A testable 4-valued adder                                            |

#### **Thesis Abstract**

Name:Maher Mohammed Al-SharifTitle:Fault Characterization and Testability Considerations<br/>In Multi-Valued Logic CircuitsMajor Field:Computer EngineeringDate of Degree:December, 1998

With the growing interest and the emergence of various implementations of Multiple-Valued Logic circuits (MVL), testability issues of these circuits are becoming crucial. Fault characterization is aimed at finding fault models that best describe faults expected to occur in a given class of circuits or technology. It can be performed either at the layout or the device level representations. Layout level techniques start by inserting defects in the layout of a fault free circuit. The resultant circuit is then extracted from the layout and simulated to study its behavior under the inserted fault. Device level techniques start by inserting shorts and opens directly to the device-levelrepresentation of the fault free circuit. The behavior of the resultant circuit is then studied. In this thesis, we aim to characterize faults in CMOS MVL circuits at the device level. For this purpose, a functionally complete set of MVL operators will be used. The set has been implemented using existing standard binary CMOS technology. This enables us to use the same techniques used for standard binary CMOS. Fault categories in MVL circuits and recommendations for testability will be given. Key Words: MVL circuits, Testing, Fault characterization, Fault modeling, Testability considerations, MVL testing

### Master of Science Degree

King Fahd University of Petroleum and Minerals Dhahran, Saudi Arabia

December, 1998

### خلاصة الرسالة

اسم الطالب الكامل: ماهرمحمد محمود الشريف عنوان الدر اسة: قليد الأخطاء واعنبار التلاخنبارية في الدو الرارقمية المنعد دة القيم المنطقية التخصص: هندسة الحاسب الآلي

تارييخ الشميهادة: ديسمبر (كانون أول) ١٩٩٨م سرمضان ١٤١٩هـ

مع الاهتمام المتزايد والوصول إلى العديد من بناءات الدوائــر الرقمية المتعددة القيم المنطقية، تصبح أمور الاختبارية لهذه الدوائر أكثر أهمية. اختبار هذه الدوائر يعتبر أكثر تعقيداً من اختبار الدوائر تنائية القيم المنطقية. يعزى هذا للعدد الأكبر من القيم المنطقية التي يستطيع حملها أى خط في الدوائر المتعددة القيم المنطقية. وهذا يؤدي بدوره إلى ظهور بعض الظواهر الجديـــدة مثل البوابات الجزئية التمكين. تحديد الأخطاء هو خطوة أساسية مبكرة في عملية تكوين الاختبار ويعنى بإيجاد نموذج للأخطاء بحيث يتضمن الأخطاء المتوقع حدوثها في أي تكنولوجيا معطاة. تحديد الأخطاء يمكن عمله على مستوى الهيكلة أو على مستوى الترانسستور. الطرق التي تعمـل على مستوى الهيكلة تبدأ بإدخال الأخطاء في هيكل الدائرة الصحيحة. يتم بعد ذلك استخراج تمثيل الترانسسور لهذه الدائرة مع الخطأ المدخل سابقاً ومن ثم محاكاتها لمعرفة تصرفها فسي وجود الخطأ. أما الطرق التي تعمل على مستوي الترانسسور فهي تبدأ بإدخال توصيلات زائدة أو فراغات مباشرة إلى تمثيل الترانسسور للدائرة الصحيحة. على سبيل المثال، يمكن إدخال توصيلا زائداً بين طرفين من أطراف أحد الترانسستورات ويتم بعد ذلك محاكاة الدائرة الناتجة لدراسة تصرفها فسى وجود هذا الخطأ. الدراسات على مستوى الهيكلة أو مستوى الترانسستور على تقنيات سيموس وبايسموس أثبتت أن تمثيل الأخطاء بنموذج التعلق بالخطأ ليس دقيقاً كفايسة لتمتيس الأخطاء الفيزيائية التي تحدث في الواقع. في هذه الرسالة غرضنا هو تحديد الأخطاء في الدوائر الرقميـــة المتعددة القيم المصنوعة بتقنية سيموس على مستوى تمثيل الترانسسور. لهذا الغرض، ثم اختيار

مجموعة من العمليات المتكاملة ادائياً من الدوائر الرقمية المتعددة القيم المنطقية. هذه العمليات تم بناؤها بواسطة تقنية سيموس مما يمكننا من تحديد الأخطاء فيها باستخدام الطرق المعروفة لسهذه التقنية. تصنيف الأخطاء في الدوائر الرقمية المتعددة القيم المنطقية وإرشادات للاختبارية سسوف تقدم في هذا البحث.

> حرجة الماجستير في العلوم جامعة الملك فهد للبترول والمعادن الظهران، الم ملكت العربيت السعوديت ديسمبر (كانون أول) ١٩٩٨ مر-رمضان ١٤١٩هـ

## Chapter 1

## Introduction

### 1.1 General

In MVL circuits, signal lines are not restricted to two values. Theoretically, they can carry any desired number of logic values. This increases the amount of information and reduces the space requirements, two desirable features in very large scale integration (VLSI) implementation. Until recently, practical implementations of MVL circuits were not possible due to technology limitations. It has been recently possible to implement MVL circuits using the available standard binary CMOS technology. This resulted in various MVL implementations either as stand alone circuits, e. g. multiplier chips [22], or as modules used in larger binary circuits. Intel, for example, used MVL in the ROM part of its 8087 coprocessor and largely reduced the space requirements making it possible to fit the circuit in a standard chip size [28].

### 1.2 Motivation

With the increasing number of MVL implementations, testing such circuits is becoming crucial. It is more involved to test an MVL circuit as compared to its binary counterpart. This is due to the increased number of logic values and the need to distinguish and eliminate an increased number of possible logic choices. However, during the test generation process, there exists some flexibility since decisions to assign a certain value to a line are not restricted to 0 or 1 only.

Previous work in testing MVL circuits includes generalizing binary testing techniques to the MVL case. Ajab Noor and Abd-El-Barr [1], for example, used Boolean Difference-like method in testing for stuck-at faults in MVL circuits. Spillman and Su [39] modified the D-algorithm to test MVL circuits. Tabakow [42] introduced a generalized D-algebra for error propagation and detection. Other work used new concepts, like the partial sensitivity for gates, found in MVL and formalized them to be used in test generation. For example, Dubrova et. al. [8] used a full sensitivity concept and formalized it to generate expressions to be used in test generation. Previous work on MVL testing has been primarily based on the stuck-at fault model. The adequacy of this model was questioned by various studies (see Chapter 4). Also, fault characterization of MVL circuits has remained unattended so far. For this reason, and due to the increased complexity of test generation of MVL circuits, it is very important to recognize the actual type of faults expected to occur in MVL implementations. This characterization becomes then an important input to any test generation algorithm.

### 1.3 Objectives

The aim of this research work is to characterize faults in MVL circuits. For this purpose, a functionally complete set of MVL operators is selected. The set is described in Chapter 2. This set is not unique and is not minimal, but it is more efficient in realizing MVL functions [20, 21]. One advantage of this set is that it was implemented using standard binary CMOS technology. This enables us to use the same fault characterization techniques used in binary CMOS in order to characterize CMOS MVL circuits. Fault characterization techniques can be conducted at two main levels, namely the layout level or the device level. In the first, a defect is inserted in the layout of a fault free circuit. The new circuit, with the inserted fault, is then extracted from the layout. Next, the resultant circuit is simulated

to study its behavior under the inserted fault. In the second approach, shorts and opens are inserted directly to the device-level representation of the fault free circuit. For example, a short can be inserted between two terminals of a transistor. Then, the behavior of the resultant circuit is studied. In this work, fault characterization in the considered set of MVL operators, is conducted at the **device level**.

### 1.4 Thesis Outline

The rest of this thesis is organized as follows. Chapter 2 introduces some background material. A functionally complete set of MVL operators is introduced. The second part of Chapter 2 introduces some new phenomena found in MVL and their effect on the test generation process. A survey of previous MVL testing work is given in Chapter 3. Chapter 4 surveys studies on the actual physical defects found in VLSI implementations. Such studies form the basis of any fault characterization technique. Techniques used in fault characterization for binary CMOS and BiCMOS are also detailed in Chapter 4. Chapter 5 describes the simulations conducted to characterize the faults. Fault categories found for the operators of the MVL set are given. Further, Chapter 6 illustrates the use of these results to find the valid test vectors for all faults found in an operator circuit by exhaustive simulation. Chapter 7 presents Design for Testability (DFT) recommendations and applications. Discussion and conclusions are given in Chapter 8 which ends with some possible future work.

### Chapter 2

### **Background Material**

In MVL circuits, signal lines are allowed to carry more than two logic values. A line in a 4-valued logic system can represent 4 different logic levels: 0, 1, 2 and 3. To represent the same amount of information in binary logic, will require two lines. This reduction in the number of lines introduces a potential for reducing the wiring interconnect, a very desirable feature needed in very large scale integration (VLSI) implementation. Another advantage of MVL is the increased functionality. For example, using one binary variable, 4 ( $2^{2^1}$ ) different functions can be realized, whereas using a four-valued variable allows the realization of  $256 (4^{4^1})$  different functions. In general, there are  $r^r$  different functions in an *r*-valued, *n*-variable system [20, 21]. Although some MVL algebras were developed as early as Boolean algebra, practical

implementations were not possible due to technology limitations. Recently, MVL gained increasing interest since it became possible to implement MVL circuits using available technologies. Implementation of MVL circuits using the already available binary CMOS process have been reported [20, 21].

Basically there are two ways for using MVL [45]. One, is to use interconnect lines carrying MVL signals between binary devices and gates. Encoding from binary to MVL and decoding from MVL to binary circuits will be needed in this scheme. The second method is to design the whole circuit or some modules (devices and the interconnect) using MVL.

# 2.1 Functionally Complete Sets of MVL Operators

A functionally complete set of MVL operators is a set of MVL operators capable of realizing any arbitrary MVL function. In this section, a functionally complete set of MVL operators is introduced. The set is reported in the work of Jain et. al. [20, 21]. It is implemented using CMOS and consists of six operators: *literal*, *cycle*, *complement of literal*, *complement of cycle*, *min* and *tsum*. Different current values are used to represent the MVL levels. In this implementation, 4-valued logic values are used. Internal threshold circuit elements generate binary voltage signals which control switches that realize appropriate current levels. The functionality of the set implementation is verified by HSPICE simulation [20].

The introduced set is not unique. There are other MVL sets of operators which are also functionally complete. Moreover, the set is not minimal. For example, *literal, min & tsum* are functionally complete. However, the introduced set is shown to be more efficient in realizing MVL functions in terms of the number of operators used and the overall required circuits [21].

#### 2.1.1 Definitions

Let  $R = \{0, 1, 2, ..., r - 1\}$  be the set of logic values for an *r*-valued logic where *r* is the radix. Assume also that  $a, b, \in R$ ,  $a \leq b$  and  $k \in \{1, 2, ..., r - 1\}$ . The following MVL operations are defined.

1. min (minimum operator) is defined as

$min (a_1, a_2, ..., a_n) = a_1 \bullet a_2 \bullet ... \bullet a_n = minimum of (a_1, a_2, ..., a_n)$  where  $a_1, a_2, ..., a_n \in R$ . For example, min (1, 2, 3) = 1.

2. tsum (truncated sum) operator is defined as

$tsum (a_1, a_2, ..., a_n) = a_1 \oplus a_2 \oplus ... \oplus a_n = min(a_1 + a_2 + ... + a_n, r - 1).$  For

example, for r = 4,  $a_1 = 2$ ,  $a_2 = 3$ , and  $a_3 = 1$ , tsum(2, 3, 1) = min(2 + 3 + 1, r-1) = min(6, 3) = 3.

3. complement of a logic level l is defined as

$$\bar{l} = (r-1) - l$$

. For example, for  $r = 4$  and  $l = 1$ ,  $\bar{l} = 3 - 1 = 2$ .

4. literal of an MVL variable x is defined as

$${}^{a}\{x\}^{b} = \begin{cases} \text{ r-1 } & \text{if } a \leq x \leq b \\ \\ 0 & \text{otherwise} \end{cases}$$

A weighted literal,  $k[a\{x\}^b]$ , is defined as

$$k[^{a}\{x\}^{b}] = \begin{cases} k & \text{if } a \leq x \leq b \\ 0 & \text{otherwise} \end{cases}$$

For example, for r = 4,  $2[1\{x\}^2]$  is equal to 2 if  $x \in \{1, 2\}$  and 0 if  $x \in \{0, 3\}$

5. cycle operator. A clockwise cycle is defined as

$\overrightarrow{x}^m = (x+m) \mod r$  where  $m \in R$ . A counter clockwise *cycle* is defined as  $\overleftarrow{x}^m = (x-m) \mod r$ . For example, for r=4, if x = <0123> then  $\overrightarrow{x}^1 = <1230>$ .

### 2.1.2 CMOS Circuit Realizations

The circuit realization, presented in [20], for the above mentioned operators uses both current mode CMOS logic (CMCL) and voltage mode CMOS logic (VMCL) circuit elements. CMCL elements are used to represent MVL levels while binary signals are represented by VMCL elements.

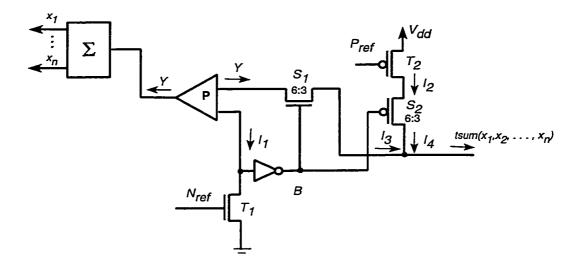

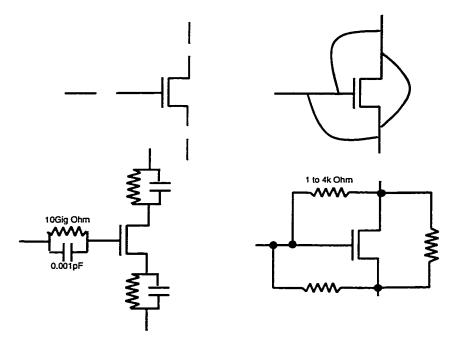

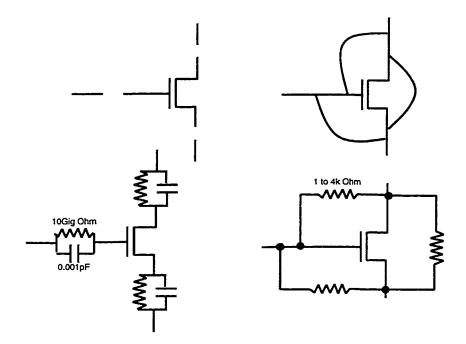

Figure 2.1 shows the basic circuit elements of CMCL which are used in the realization of the above operators. Figure 2.2 shows the realization of the *min* operator. Its transient-time response is shown in Figure 2.3 (scanned from [20] with permission). The *tsum* realization is shown in Figure 2.4 and the transient-time response in Figure 2.5 (scanned from [20] with permission). *Literal* and *complement of literal* operators are shown in Figures 2.6 and 2.7 respectively. Figure 2.8 shows the transient-time responses of  $3[{}^{1}{x}{}^{2}]$  and  $\overline{2[{}^{1}{x}{}^{1}]}$  (scanned from [20] with permission). Figure 2.9 shows the cycle realization. Finally, Figure 2.10 (scanned from [20] with permission) shows the ( $\overleftarrow{x}^{2}$ ) cycle operator transient-time response.

The above realizations will be used in this work to study the possible types of faults that can occur at the end of a production line. The following sections will review fault characterization studies conducted on typical CMOS circuits. The methods used to model possible faults in those studies will be applicable to the above MVL realizations since the same binary CMOS technology is used in both. Some general MVL testability issues are presented in the next subsection.

| Name                                 | Logic Operation                                                               | Symbol                                                                                       | Circuit Realization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sum                                  | $y = x_1 + x_2 + \dots + x_n$                                                 | $\begin{array}{c} x_1 \\ x_2 \\ \vdots \\ x_n \end{array} \begin{array}{c} y \\ \end{array}$ | $\begin{array}{c} x_1 \\ x_2 \\ x_2 \\ \vdots \\ x_n \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Constant                             | <i>y</i> = <i>k</i>                                                           | К→                                                                                           | $P_{ref} \downarrow \kappa \qquad \qquad$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| NMOS<br>and<br>PMOS                  | <i>y<sub>i</sub> = a<sub>i</sub> x</i><br>for <i>i = 1, 2,, n</i>             | $x \qquad N \qquad y_1 \\ \vdots \\ y_n$                                                     | $ \begin{array}{c} \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Current<br>Mirror                    | a <sub>i</sub> : scale factor                                                 | $\begin{array}{c} x \\ \hline P \\ \hline \vdots \\ y_n \end{array}$                         | $ \begin{array}{c} & & V_{dd} \\ \hline & & & \\ \hline \\ \hline$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| P-type<br>and<br>N-type<br>Threshold | For N-type<br>if (x >= k) then<br>y = binary high<br>else<br>y = binary low   | x Thresh(k) $y$                                                                              | $P_{ref} \downarrow \kappa \qquad \qquad \qquad \qquad$ |

| P-type<br>and<br>N-type<br>Switch    | if (Switch is ON) then<br>y = x<br>else (Switch is OFF)<br>y = 0 (no current) | x Switch $y$                                                                                 | $\frac{v_{in}}{\psi_{in}} = \begin{bmatrix} \psi_{x} & v_{in} \\ \psi_{y} & \psi_{x} \end{bmatrix}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Figure 2.1: Basic circuit elements for CMCL.

Figure 2.2: Circuit realizing *min* operator. (a): input currents are sinking, (b): input currents are sourcing

Figure 2.3: Transient-time response of the *min* operator.

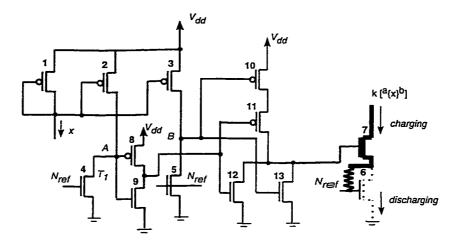

Figure 2.4: Circuit realization of tsum.

Figure 2.5: Transient-time response of the *tsum* operator.

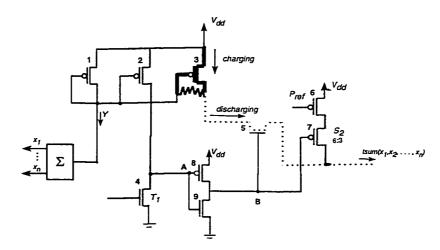

Figure 2.6: Realization of a literal  $k[a\{x\}^b]$  operator.

Figure 2.7: Realization of a complement of literal  $\overline{k[a\{x\}^b]}$  operator.

Figure 2.8: Transient-time response of  $3[1\{x\}^2]$  and  $\overline{2[1\{x\}^1]}$  operators.

Figure 2.9: Circuit realization of the cycle operator.

Figure 2.10: Transient-time response of the cycle operator.

### 2.2 Testability Issues in MVL Circuits

For a given line in a MVL network, the number of possible values that can be assigned is more than those assigned to a binary line. This complicates the test generation process as compared to the binary case. This is due to the increased number of logic values and the need to distinguish and eliminate an increased number of logic choices. However, during the test generation process, there exists some flexibility since decisions to assign a certain value to a line are not restricted to 0 or 1 only.

In addition, new concepts related to the MVL arise. At any given time, an MVL gate can be either partially or fully enabled. A gate is fully enabled along one of its inputs if the gate's output is sensitive to any change on that input. This can be

achieved by setting other inputs to appropriate values. A 2-input binary AND gate can be fully enabled (sensitive) along one of its inputs if the other input, call it the fixed input, is set to 1. So any change on the free input can be sensed at the output. If, on the other hand, the fixed input was assigned to 0, the gate is disabled and changes on the free input have no effect on the output, which will be always 0.

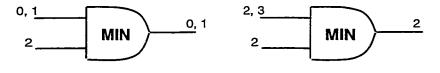

The same concept (enabled or disabled gate) can be generalized to the 2-input MVL min gate by substituting 0s, in binary, with 0s, in MVL, and 1s with r-1. However, if the fixed input is set to k, where 0 < k < r - 1, the min gate is partially enabled (k-enabled). It will be sensitive to some values and disabled for some others. This case does not exist in binary.

To illustrate the above concept, consider the 4-valued, 2-input min gate shown in Figure 2.11a where the fixed input is assigned to k. All inputs greater than or equal to k are indistinguishable at the output. If k = 2 (Figure 2.11b), the gate is sensitive only to 0 and 1. The output is always 2 for the rest of input values. So, input changes for values  $\geq 2$  have no distinguishable effect on the output.

#### 2.2.1 K-enabled Gates and Fault Propagation

During the test generation process of a binary network, an error signal is generated at a given point (line) in the circuit. Then, it is propagated to an observable output.

a.: all  $p \ge k$  are indistinguishable

b.: 2 and 3 are indistinguishable

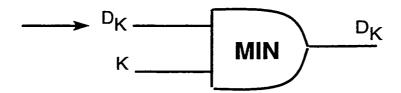

Figure 2.11: k-enabled gates.

During this propagation, assignments are made to some other circuit lines. These assignments have to be justified after a successful propagation of the error signal to an observable output is achieved. If both phases of error propagation and assignments justification are successful, a test is generated for the error signal (the fault). If, on the other hand, the assignments are not justified they are removed from the solution space and the process is repeated with new assignments. This procedure continues until a test is found or all possible assignments are tried. Usually, a time limit is set and when it is exceeded, the procedure stops even if there are untried assignments left. If the procedure stops and no test was found, the fault is considered un-testable. Different algorithms, e. g. D [30], PODEM [13] & FAN [11], try to guide the assignments through the solution space in such a way that minimizes the dead iterations (unjustifiable assignments) and avoids wrong assignments as early as possible. The degree of success in doing so determines the efficiency of the algorithm and its execution time.

For MVL, similar procedure applies. The fact that lines can be assigned to more than two logic values introduces an added complexity. K-enabled gates also add to this complexity and if not treated properly, wrong assignments can be made during error propagation and a lot of time can be wasted.

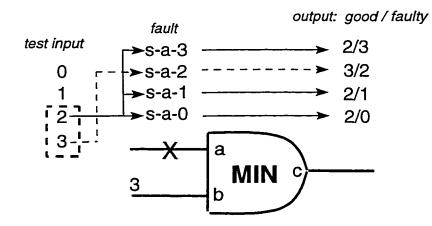

Consider, for example, the 4-valued min gate shown in Figure 2.12. The gate is fully enabled since its fixed input (line b) is assigned to r - 1 = 3. Suppose that a value  $p \in \{0, 1, 2, 3\}$  is assigned to the free line (line a). This value of p will test for all single stuck-at faults except stuck-at-p (s-a-p). To test for s-a-p, any value other than p can be used. For example, 0 will test for s-a-1, s-a-2, s-a-3. Any other value (1, 2, or 3) can test for s-a-0. As a result, a combination of any two values will test for all single stuck-at faults on the free line (line a). Vectors including 2 and 3 can be selected as shown in the figure.

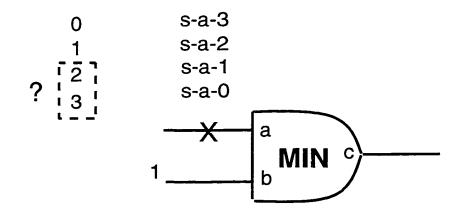

Now, consider the partially enabled *min* gate shown in Figure 2.13. In this case, 0 is the only assignment that can test for s-a-1, s-a-2, s-a-3 giving 0/1, 0/1 and 0/1 output respectively. Any other assignment will only test for s-a-0 (1, 2, or 3 will give 1/0). So, unlike the previous case, the combination 2 & 3 can not be used. Any valid combination must include the input value 0.

This illustrates that k-enabled gates and paths passing through them should be

Figure 2.12: Fully enabled gate.

Figure 2.13: 1-enabled gate.

treated properly in any test generation algorithm. A significant time can be waste=d during test generation if the k-enabled gates concept is not taken into account bey algorithms generating tests for MVL circuits. The occurrence of these k-enable=d gates is network dependent (related to the values of constants, k's, found in the network). Also, every MVL network is likely to have k values (constants) since any set of MVL operators must include a decision operator that limits its output to tw-o values for all input combinations. These values become the k's for gates connecte-d to that output. For example, the literal operator  $2[{}^{1}{x}{}^{2}]$  will give either 0 or 2 on the output. Then if 2, for example, was connected to a *min* gate, it will limit its sensitivity. Values  $\geq 2$  on the other input of the *min* gate will not produc=e distinguishable output changes, as shown in Figure 2.11(b).

# Chapter 3

# Literature Review

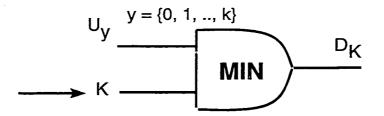

Previous work showed that it is more involved to test MVL circuits as compared to their binary counterparts since the test generation algorithms have to deal with the new phenomena introduced by MVL operators. Spillman and Su [39] modified the D-algorithm to test MVL circuits. They start by identifying k-enabled gates and paths passing through them for the whole circuit. Then special D's are propagated through these paths. For the other paths, D propagation is the same as in the binary case. The D-algorithm is modified to propagate D-chains along three separate types of paths:

1. paths along min gates where the other input of the min exists on a k-path (kenabled min). A simplified example is shown in Figure 3.1(a). The D's along such paths are subscripted with a k. Stuck-at-p faults are indistinguishable for  $p \ge k$ .

- 2. D-chains along k-paths where a k value exists on any point of the path. This is illustrated in Figure 3.1(b). The  $U_y$  notation is introduced to show the limited set of values that a line can have. The set  $y=\{0, 1, ..., k\}$  is the set of values that a line can not assume.

- 3. D-chains along all other remaining paths (normal D-chains).

The modified D-algorithm, first, constructs all tests for distinguishable faults along the k-paths of the circuit. Then, it constructs the tests for distinguishable faults along  $D_k$  chains. Finally, it constructs tests for faults along the remaining D-chains. Further, the introduced  $\triangle$  product algorithm reduces the number of tests by utilizing the U notation.

Tabakow [42] introduced a generalized D-algebra. The purpose was to introduce an algebraic system usable in the process of fault oriented test generation for combinational MVL circuits. This method simplifies path sensitization as compared to the previous method of Spillman and Su. In this system, D's are represented as:  $d_{ij}$ where  $i, j \in \{0, 1, ..., r-1\}$  and r is the radix of the MVL system. The binary D, for example, is represented as  $d_{01}$ . For a ternary algebra,  $d_{02}$  means 0 in the fault-free circuit and 2 in the faulty circuit. Constants like 1 and 2 are represented by  $d_{11}$  and

a.: propagating along k-enabled gates.

**b.:** propagating along k-paths.

Figure 3.1: Different D-chains propagation.

$d_{22}$ , respectively.

The error signal and the generated  $d_{ij}$ 's are propagated by means of intersection rules defined for the system. These rules will only propagate the correct d values through any k-enabled gate directly without the need for a second pass like in the Spillman and Su method. Some of these rules are introduced below with some examples assuming ternary logic (r=3).

$MAX(i,\,j)=i+j=i$  if  $i\geq j$  and j otherwise.

$MAX(d_{i_1j_1}, d_{i_2j_2}) = d_{i_1j_1} + d_{i_2j_2} = d_{(i_1+i_2)(j_1+j_2)}.$

$MIN(i, j) = i \bullet j = i \text{ if } i \leq j \text{ and } j \text{ otherwise.}$

$MIN(d_{i_1j_1}, d_{i_2j_2}) = d_{i_1j_1} \bullet d_{i_2j_2} = d_{(i_1 \bullet i_2)(j_1 \bullet j_2)}.$

As mentioned earlier, if a 2-input min gate, for example, is k enabled, then it is sensitive only to inputs in  $\{0, 1, ..., k-1\}$  where  $k \in \{0, 1, ..., r-1\}$ . Accordingly, the  $d_{ij}$  values that can propagate through should satisfy:

MIN(k,  $d_{ij}$ )  $\in D_{\neq} \leftrightarrow k \in M - \{0, ..., min(i, j)\}$  where M= $\{0, 1, ..., r-1\}$  and  $D_{\neq}$  is the set of all  $d_{ij} / i \neq j$  (a d value that distinguishes the fault-free circuit from the faulty circuit). Similarly, the rule for the MAX operation:

MAX(k,  $d_{ij}$ )  $\in D_{\neq} \leftrightarrow k \in M - \{max(i, j), ..., r-1\}$ . Similar rules are defined for the rest of operations, formalization of propagation rules and definitions are presented to complete the algebraic system. Also, the system is generalized to deal with multiple stuck-at faults.

Also, Vlad Shmerko et. al. [37, 36] modified the D algorithm. However, they used modern results of Logic Differential Calculus and also sensitizing path method to build generalized D-algebra based on the Direct Logic Derivative (DLD) notation.

In parallel, other works have used algebraic methods to find MVL tests. Ajab Noor and Abd-El-Barr [1], for example, used Boolean Difference-like method in testing for stuck-at faults in MVL circuits. Tapia and Guima [43] introduced new differential operators for logic functions in a multi-valued algebra. These operators were used in algorithm to find complete tests for stuck-at type faults in MVL circuits. They showed that the boolean differential operators are special cases of the new MVL operators. Whitney and Muzio [47] generalized the decisive difference method to MVL and used it to define functional transformations as partial differences. Boolean difference is a special case of the partial differences applied.

Other works used some new concepts in finding MVL tests. Dubrova et. al. [8, 9] used the full sensitivity concept, found in MVL, and formalized it to generate expressions to be used in test generation. Basically a function is fully sensitive to some line l if each transition on this line from one logic level to another causes a change in the output logic value. This concept is formalized and used to calculate test vectors for large functions. For example, if a line l in an MVL n-variable function is to be tested for a stuck-at-p fault, it is cut and considered as pseudo input  $x_l$ . Then, the line value is expressed in terms of the function inputs  $l(x_1, x_2, ..., x_n)$ . The function is expressed in terms of its inputs and the line l  $f_l(x_1, ..., x_n, x_l)$ . Then, the formalized procedures are used to find some set of values  $(a_1, ..., a_n)$  such that  $l(a_1, ..., a_n) \neq p$  and some  $k \neq p$  such that  $f_l(a_1, ..., a_n, k) \neq f_l(a_1, ..., a_n, p)$ . A solution for two different values of k will result in tests for all stuck-at faults at line l.

In the work of Wang et. al. [46], a complete test set (CTS) was defined and derived for MVL Min/Max networks. The CTS is capable of detecting any single and multiple stuck-at faults of MVL Min/Max networks. Once this CTS is found for a given function, it will be valid regardless of the implementation. It is similar to the binary Universal Test Set (UTS). The method of generating the CTS starts by defining the literal truth table for the given function. First, the function is described in Sum of Products of literals. There is one column, in the literal truth table, for each literal in the function expression and one row for each possible function value (listed in the row, the literal values that produced this function value). Then, by applying enumeration rules and algorithms, the CTS is derived for the function. This method is reported to be more efficient and time and memory saving than enumerating the truth table of the function.

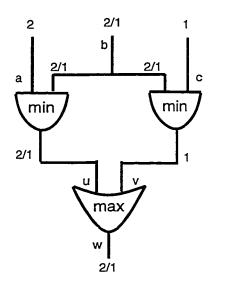

There has been some work reported in the literature on testing Sequential Multi-Valued Logic (SMVL) circuits. Drechsler et. al. [6] presented a fault simulator for Sequential Multi-Valued Logic Networks (SMVLN). This fault simulator was an extension of the combinational circuits fault simulator presented in [7]. The simulator algorithm receives r (the radix of the r-valued MVL), an input sequence, and a description of the circuit as input and returns the fault coverage achieved as output. In addition, the set of undetected faults is returned. The algorithm works in two main steps. First, the list of all possible faults is generated and then simplified by finding the set of equivalent faults. In the second step, the detectability of these faults is determined by an event-driven single fault propagation procedure. In this procedure, the circuit is first evaluated under the input sequence and the value of each line is determined. Faults are then injected into the circuit one by one and only events produced by an inserted fault are propagated to the primary outputs. If, during this propagation, any primary output changes its value, the fault is marked detected and removed from the list. To illustrate the event-driven approach, consider Figure 3.2. Suppose that r = 3, the input vector is [a = 2, b = 2, c = 1] and node b is stuck-at 1. Both min gates have to be re-evaluated which results in a new event at node u. Accordingly, the max gate have to be re-evaluated and the fault is marked detectable since it produces a change at the primary output [7]. To handle SMVLNs, the fault simulator was extended by replacing each memory element by a Secondary Input (SI) and a Secondary Output (SO) [6]. After this replacement, the SMVLN is converted to MVLN where the value of any SI at time t is defined by the value of the corresponding SO at time t-1.

Figure 3.2: Event driven fault simulation.

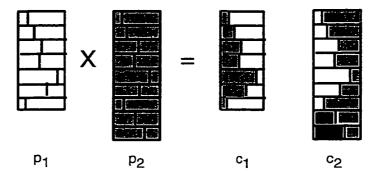

Keim et. al. [23] presented an Automatic Test Pattern Generation (ATPG) tool for SMVLN based on Genetic Algorithms (GA) and reported experimental results for large circuits, with up to some thousand gates. The fault models considered are the stuck-at and skew fault models. There are two types of skew faults. One raises the logical value of an edge in the circuit by one, and the other lowers the logical value of that edge by one. The basic concept in GA is: Two parent elements (genes) are mixed (GA operator) to produce two new generation elements (genes) each of which has a combination of properties from the two parents. In addition to the standard GA operators used, a problem specific operator (Free Vertical Crossover) is defined. The test sequence set is represented by a two-dimensional matrix. The x-dimension represents the number of inputs and the y-dimension represents the number of test patterns (see Figure 3.3 [23]). Free Vertical Crossover is defined as: construct two new elements  $c_1$  and  $c_2$  from two parents  $p_1$  and  $p_2$ . Determine for each test vector t a cut position. Divide each test vector t of  $p_1$  and  $p_2$  in two parts at its cut position. The first (second) part of each test vector  $c_1$  ( $c_2$ ) is taken from  $p_1$  and the second (first) part is taken from  $p_2$ . Figure 3.3 illustrates this operator (the black areas are filled with random patterns). The main idea of the ATPG tool introduced in this work makes use of GA in two phases. The first phase optimizes a given test sequence set for the length and fault coverage. The algorithm in this phase runs until no improvement found for 100 consecutive generations. The second phase increases the size of the set to improve the fault coverage of uncovered

faults in phase one. The stop criterion for the second phase is set after 50 consecutive generations with no improvement.

Figure 3.3: Example for *free vertical crossover* genetic operator.

Other category of research used MVL circuits and concepts to test binary circuits. Mou Hu [18], for example, discussed Design for Testability (DFT) rules to design binary systems based on ternary logic. Two values of the ternary logic were used for normal binary operation. The third value was used only for testing purposes. The third value will appear only in the test vectors and the function's normal response to these vectors. If the function undergoes a fault, its response to the test vector will be one of the binary values indicating the presence of a fault.

# Chapter 4

# Physical Defect Modeling and Simulation

## 4.1 Physical Defects

On the production lines of ICs, physical defects interfere with the desired circuit design and result in faulty chips. The occurrence of such defects depends on the circuit layout, fabrication process, device parameters and many other technology related factors.

There have been tremendous efforts to understand and characterize physical de-

fects in ICs and their effect on the circuit behavior. Many studies were conducted on faulty chips taken from actual production lines [12, 2, 40, 26, 29, 5]. The actual reasons (physical & chemical) behind such defects are not well known. However, statistical data collected from experiments and actual production lines is available in the literature. This becomes an important input to realistic fault modeling studies producing fault models closer to the actual physical defects and guiding test generation to more accurate decisions.

In general, defects can be classified into two groups:

- Shifts in electrical parameters (voltage, threshold, etc.): This can grossly affect the operation of the chip and can be easily detected by parameters measurements.

- 2. Topological layer deformation: This can be classified further into two types:

- (a) Global: such as scratches across the whole chip, photolithography misalignment, line registration errors, too thick gate oxide, too thin polysilicon, etc. These defects are easily detected by almost any test pattern. This is because they tend to have global effects on the chip operation and functionality.

- (b) Local (spot): such as gate oxide pinhole, dust particles on chip or mask.These defects result in complete, or nearly complete, opens or shorts in

some signal lines and affect small (local) portions of the chip producing the hardest faults to detect [4, 5, 19].

#### 4.1.1 Physical Defects & Faults

Defects at the lowest level, the layout level, manifest themselves in a variety of forms at higher levels, electrical or logical level. The description of these effects at high levels is known as *fault modeling*. Fault models should compromise two conflicting features: the needs for accurate modeling of physical defects and easy-to-deal-with models that will not complicate the test generation process [19].

For long time, test pattern generation algorithms relied on the assumption that defects can be modeled at the gate level representation as lines stuck-at 0 or 1. However, as VLSI device sizes decrease and with the emergence of newer technologies, e.g. CMOS and BiCMOS, the adequacy of such assumption becomes questionable. A number of studies showed that the stuck-at model is not adequate to model failure mechanisms found in practice. For CMOS technology, most of the defects result in undesirable bridges (shorts), including gate oxide shorts, breaks (opens) and circuit parameter shifts. These can not be accurately modeled using the stuck-at fault model [12, 2].

#### 4.1.2 Spot Defects

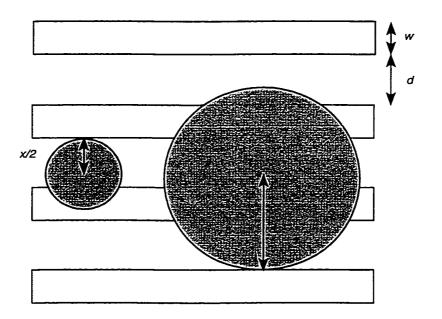

The probability that a spot defect will cause a fault depends on the spot size, spot location, and circuit layout topology. For example, the probability that a spot will short two wires running in parallel depends on the wires's length, spot size (compared to the separation distance), and the location of the spot [5]. If the line width is w, separation distance of the two lines is d, and the spot is represented by a circle of diameter x, then the probability of shorting two lines, or more, can be estimated once these dimensions are known (See Figure 4.1) [19].

Figure 4.1: Spot defects overlapping two or more wires.

The *critical area* is defined as the area where the spot center is expected to occur [4]. For example, the overlapping area of two conducting lines of adjacent layers is critical. Stapper [40] found mathematical models to represent these defects. The models related the critical area to the defect size and location. Defect size and location distribution functions were obtained from statistical data gathered from different production lines and sites. The critical area can be calculated from the process masks. For example, a mask-dependent defect size distribution function  $D_m$  was developed as:

$$D_m(x) = \begin{cases} \overline{D_m} \frac{x}{x_0^2} & \text{for } 0 \le x \le x_0 \\ \\ \overline{D_m} \frac{x_0^2}{x^3} & \text{for } x_0 \le x \le \infty \end{cases}$$

where x is the spot circle diameter,  $x_0$  is a technology dependent constant, and  $\overline{D_m}$  is the average defect density for layer m. The average number of faults  $\lambda_{photo,m}$  (produced at a layer creation process defined by mask m and defect sensitive area A) can be calculated as:

$$\lambda_{photo,m} = \int A(m) D_m(x) dx$$

These models were then used to estimate the fault occurrence and yield of different circuits. After studying the effects of spot defects on the circuit behavior, more realistic types of faults can be recognized which leads to a more accurate tests. Defects that create similar electrical behavior are grouped to produce fault lists. Typical failures found in CMOS technology include: bridging faults (most found), broken wires, missing contacts, extra contacts and newly created devices (low percentage). Such failures result in faults that can not be described as stuck-at faults [19, 10, 2, 5]. This shows the need for characterizing the fault types occurring in a specific technology and not relying only on the stuck-at fault model which in some cases, like SRAM, represents only 50% of the actual faults [5].

## 4.2 Fault Characterization

In general, to find the effects of defects on the circuit behavior (fault characterization), a defect model is proposed and inserted in the circuit. Then, simulation is performed to find the circuit behavior under that defect. This process can be done at two different levels, namely at the device level [34, 44, 10, 48, 15, 17, 24, 25, 27, 31, 32, 41] or at the layout level [4, 5, 35, 40, 26, 19].

#### 4.2.1 Device Level Fault Characterization

The gate level representation of a circuit does not relate directly to the devices locations and layout. There may be lines and connections at the device level representation which do not exist or have no meaning in the gate level representation. For example, the gate-level symbol of a NAND gate does not show the lines connecting its internal transistors. Hence the device level representation is believed to give more accurate representation of the actual circuit elements.

Based on the studies mentioned in the previous section and other studies on the effect of transistor gate-oxide shorts [34, 44], a general procedure for device level fault characterization is widely accepted in the literature. Given the circuit level representation, defects are inserted one at a time. Then, using a standard circuit simulator (e.g. SPICE), the behavior of the circuit is evaluated in the presence of the defect to recognize fault types and groups.

At the device level, the possible faults considered are shorts between terminal nodes (gate-drain, gate-source and source-drain) and opens between these terminals and other circuit nodes connected to them.

Device level fault characterization found in the literature can be classified into two main groups. The first one represents shorts as zero resistance connections. Favalli et. al. [10] simulated faults and compared the analog voltages at relevant nodes with the logic threshold voltage  $V_{lt}$  to find out if the fault generates faulty logical behavior. This gives detectability tables, for each type of fault for each gate, which are used by the simulator to find whether or not the fault is detectable.

The work of Zaghloul et. al. [48] also falls into this group. They proposed a graphical technique in which the transfer characteristics of the circuit's basic elements are graphically intersected to produce the resultant characteristics of a combination of elements at a higher level. This process starts at the faulty part and proceeds to other affected parts up to the primary outputs. This gave more accurate results in evaluating the complex analog behavior of some faults, such as gate-oxide shorts. The second group takes into account the variable short resistance actually found in practice. Hao and McCluskey [15] showed that for typical CMOS circuits this resistance value, in some cases, is critical and circuit behavior varies largely for different values of this resistance. Some shorts can produce normal output, delayed output (delay fault) or logical fault depending on the resistance value of the short.

Similar studies were conducted on BiCMOS technology [17, 24, 25, 27, 31, 32, 41]. These studies showed different behaviors of circuits that can not be detected by tests generated for stuck-at faults. Ma and McCluskey [25], for example, found new types of faults in BiCMOS that do not exist in other technologies. In some cases the faulty circuit produced the correct output for some time and then transferred to a faulty value. In other cases the output was oscillating.

This shows that technology and circuit design and topology largely affect the type of faults expected to occur during fabrication, and highlights the needs for techniques to test for these faults.

For this class of fault characterization, it is common to represent the defects at the transistor level as resistive shorts between terminals and opens between each terminal and circuit nodes connected to it, see Figure 4.2.

Figure 4.2: Open and short faults and their models.

#### 4.2.2 Layout Level Fault Characterization

Although the device level representation is more accurate than the gate level in representing the actual circuit, the layout level deals with the actual circuit representation and highlights the technology and circuit topology dependent features. Generally, layout fault characterization starts by inserting defects at the layout of the circuit. Then, the resultant layout is submitted to an extractor to extract the circuit representation of the modified layout. This circuit representation can then be simulated, using a circuit simulator, to compare the behavior of the new circuit, with the inserted defects, to that of the original one. The results of the previous step are gathered and classified to produce fault lists that are directly related to the actual layout. A typical example is the work of Chess et. al. [4] and Dekker et. al. [5].